Изобретение относится к вычислительной технике и может быть использовано для построения надежных мультипроцессорных систем с возможностью отключения отказавших процессорных блоков и замены их исправными.

Известна мультипроцессорная система, которая содержит однотипные процессорные блоки, канал обмена информацией, системную память, устройства ввода-вывода, вычислительные блоки, триггеры, логические элементы.

В процессе работы системы процессорные блоки выполняют свои программы. Один из них обеспечивает управление работой системы, т.е. является управляющим процессорным блоком.

Недостатком такой системы является невозможность замены другим процессорным блоком вышедшего из строя управляющего процессорного блока, т.е. система оказывается неработоспособной.

Известна мультипроцессорная система, содержащая п однотипных процессорных блоков, канал обмена информацией, системную память, устройства ввода-вывода. Один из процессорных блоков выбирается управляющим, остальные - подчиненные процессорные блоки.

В состав каждого процессорного блока включены элементы И, ИЛИ, блок отключения управляющего процессора, триггер управления, вычислительный блок, которые позволяют отключать вышедшие из строя

XI JGJ

ю

СА)

сл

один или несколько подчиненных процессорных блоков или управляющий процессорный блок, Процессорные блоки можно заменить резервными, а функции управляющего процессорного блока передаются одному из подчиненных процессорных блоков. Система остается работоспособной. Недостатком данной системы является то, что в случае одновремеменного отказа управляющего и подчиненного процессора система становится неработоспособной, так как голосование подчиненных процессоров за отключение управляющего осуществляется по принципу все за. Если одновременно с управляющим процессором выходит из строя хотя бы один из подчиненных, то он может не вырабатывать сигнал отключения управляющего процессора. В этом случае управляющий процессор не будет отключен и система окажется неработоспособной.

Цель изобретения - повышение надежности системы при одновременном отказе управляющего и подчиненных процессорных блоков путем замены их работоспособными процессорными блоками.

Поставленная цель достигается тем, что в мультипроцессорной системе, содержащей п процессорных блоков, системную память, группу устройств ввода-вывода, причем информационные адресные и управляющие входы-выходы каждого процессорного блока через системную шину подключены к одноименным входам-выходам системной памяти и устройствам ввода-вывода, причем каждый процессорный блок содержит элемент И, элемент ИЛИ-НЕ, триггер управления коммутацией, триггер отключения процессора, шинный формирователь, вычислительный блок, информационный вход-выход которого является одноименным входом-выходом процессорного блока, выход признака неисправности управляющего процессорного блока подключен к входу синхронизации триггера управления, информационный вход которого подключен к входу выбора управляющего процессорного блока, первым входам элементов ИЛИ-НЕ и элемента И, выход которого является выходом выбора управляющего процессорного блока, второй вход элемента И подключен к второму входу элемента ИЛИ-НЕ, входу блокировки вычислительного блока и выходу триггера отключения, вход синхронизации которого подключен к выходу шинного формирователя, вход которого является входом отключения управляющего процессорного блока, а информационный вход триггера отключения соединен с выходом триггера управления коммутацией и входом управления коммутацией вычислительного блока, выход отключения подчиненного процессора которого подключен к входу установки в нуль триггера отключения процессора, в каждый процессорный блок

дополнительно введены триггер голосования, триггер реконфигурации, элемент задержки, переключатель, элемент И, выход которого соединен с входом элемента задержки, выход которого подключен к входу

0 установки в нуль триггера голосования и является выходом голосования процессорного блока, тактирующий вход триггера голосования соединен с выходом элемента ИЛИ-НЕ, вход установки в единицу триггера

5 голосования является входом голосования процессорного блока, прямой выход триггера голосования соединен с первым входом элемента И, инверсный вход которого является входом управления сдвигом про0 цессорного блока, второй вход элемента И является входом сдвига процессорного блока, инверсный выход триггера голосования является выходом сдвига процессорного блока, вход установки в ноль триггера

5 реконфигурации является входом сброса процессорного блока, синхровход триггера реконфигурации подключен к тактирующим входу и выходу процессорного блока, вход установки в единицу триггера

0 реконфигурации является входом реконфигурации процессорного блока, выход триггера реконфигурации подключен к выходу реконфигурации процессорного блока и через переключатель к выходу отключения управля5 ющего процессора процессорного блока, входы сдвига, реконфигурации, тактирования и выходы выбора, голосования i-ro (i 1,n) процессорного блока соединены с одноименными выходами и входами (i+1)-ro

0 процессорного блока, выход голосования n-го процессорного блока соединен с тактирующим входом n-го процессорного блока, выходы сброса, управления сдвигом и отключения управляющего процессора всех

5 процессорных блоков через одноименные шины соединены с одноименными входами всех процессорных блоков.

Отличительные признаки в указанной взаимосвязи ранее нигде не встречались,

0 являются существенными и в своей совокупности позволяют увеличить надежность системы за счет возможности замены одновременно отказавших подчиненных и управляющего процессорных блоков рабо5 тоспособными.

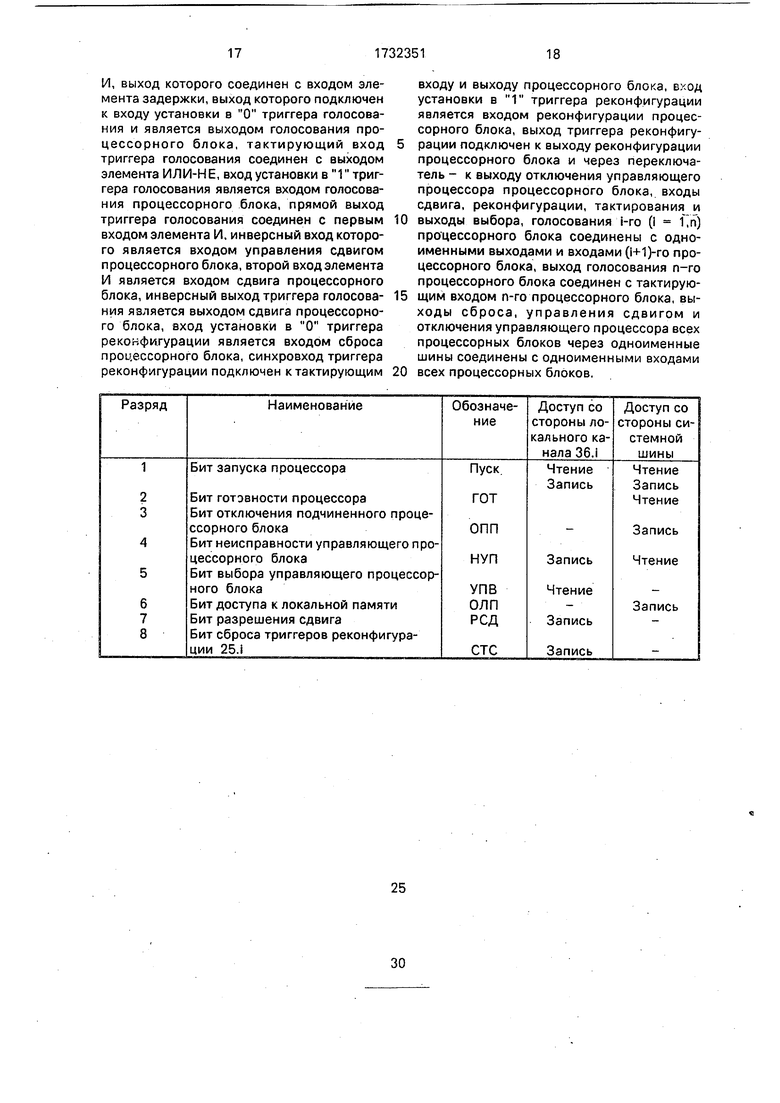

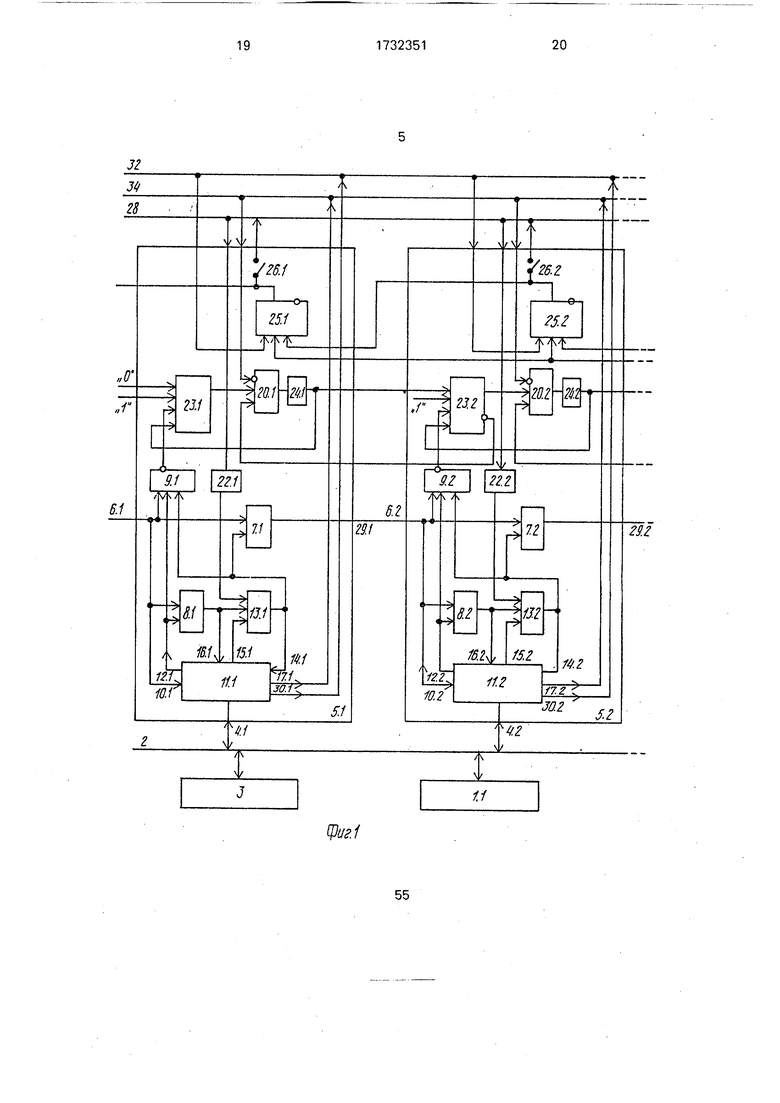

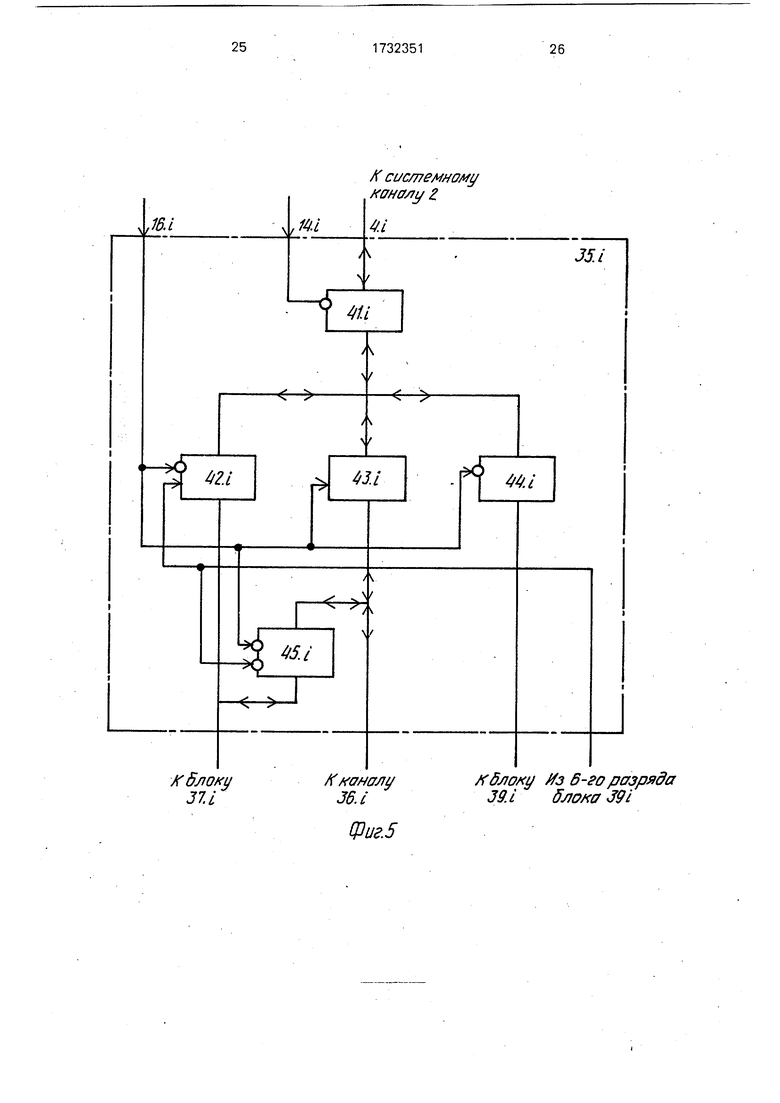

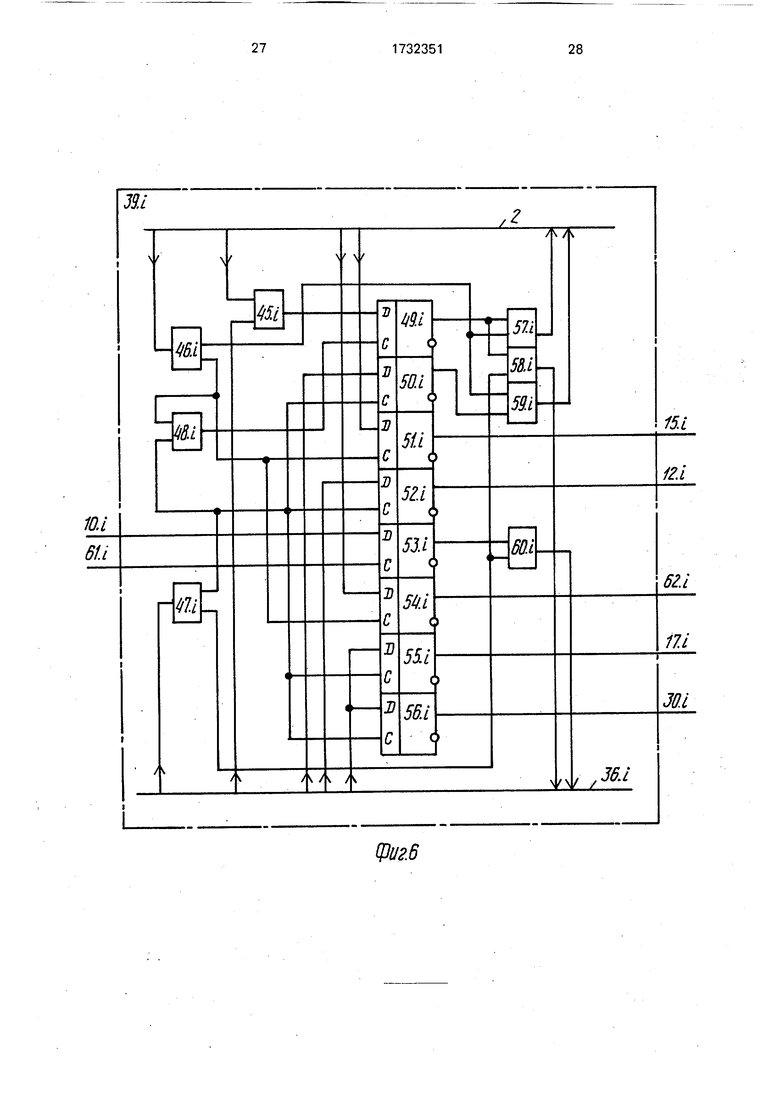

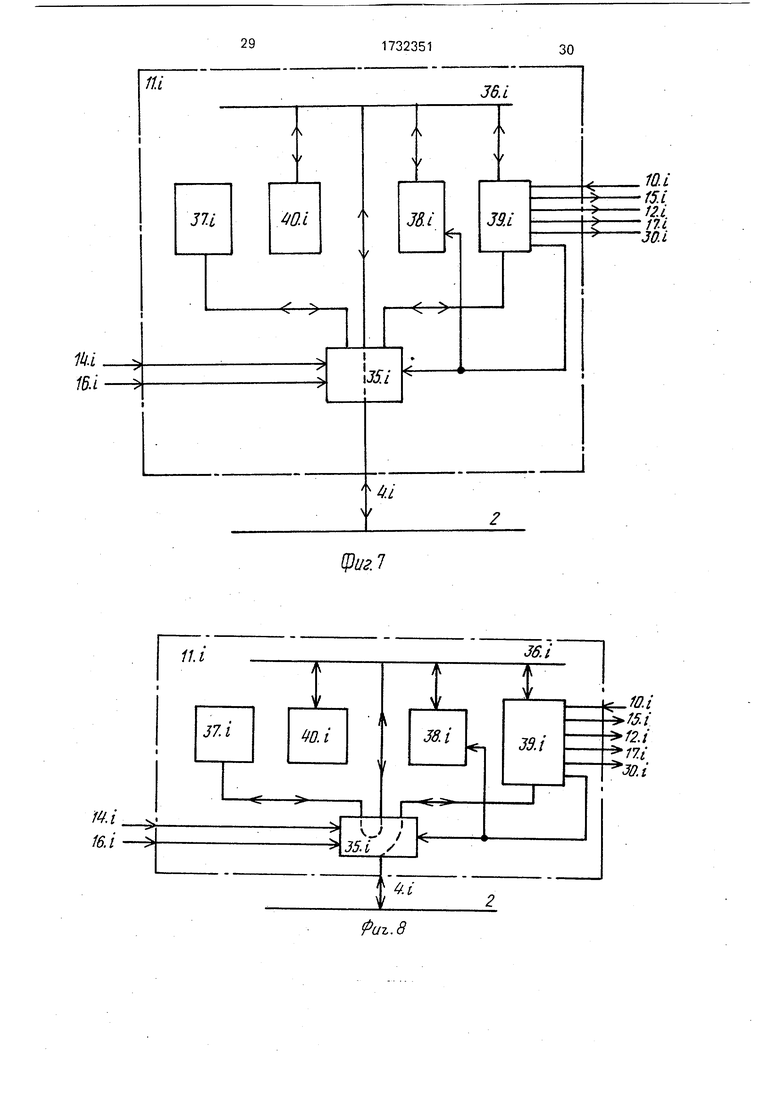

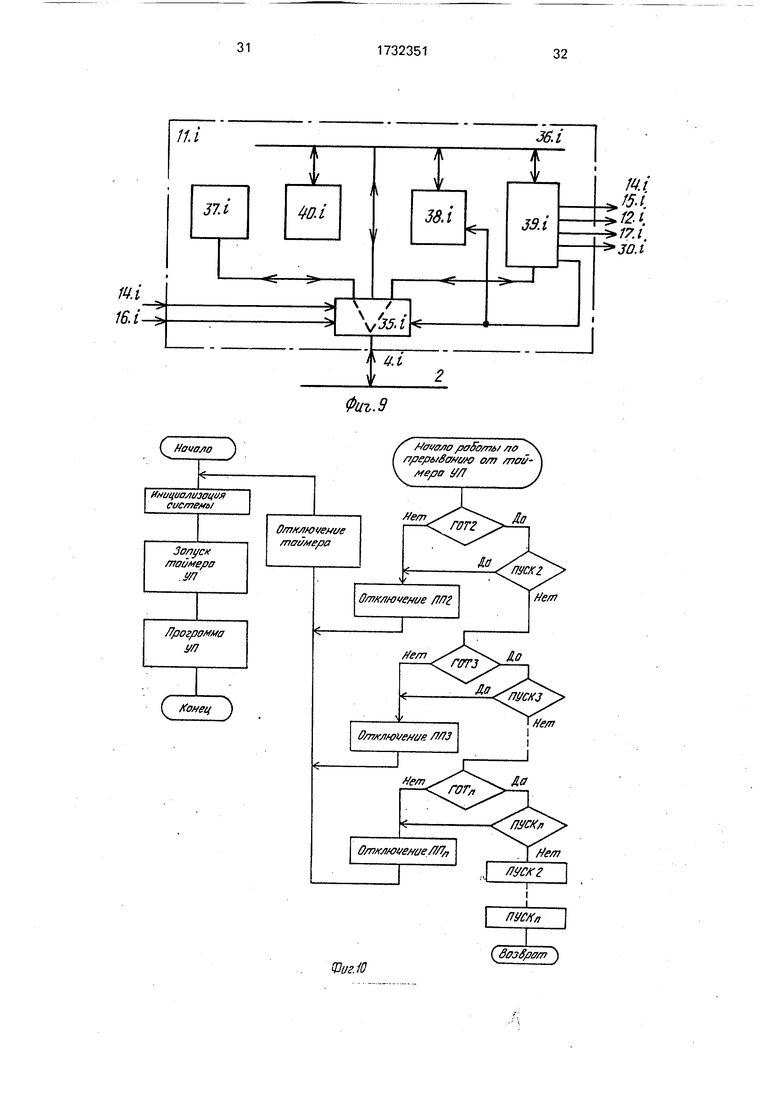

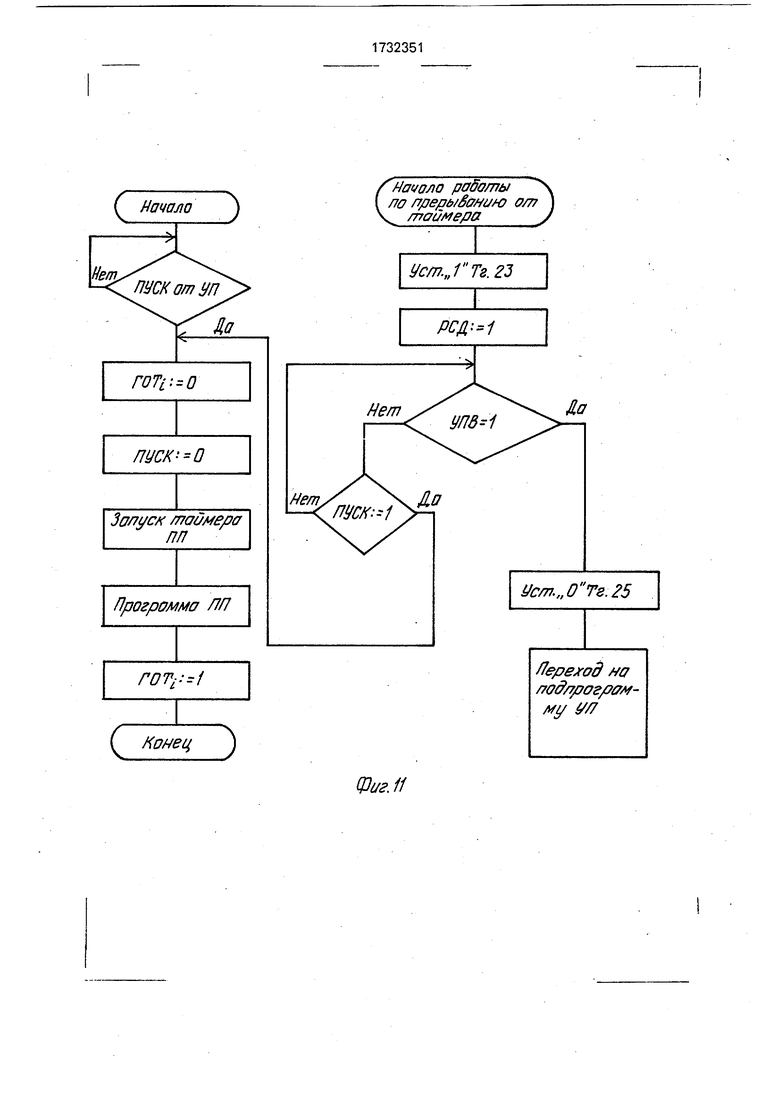

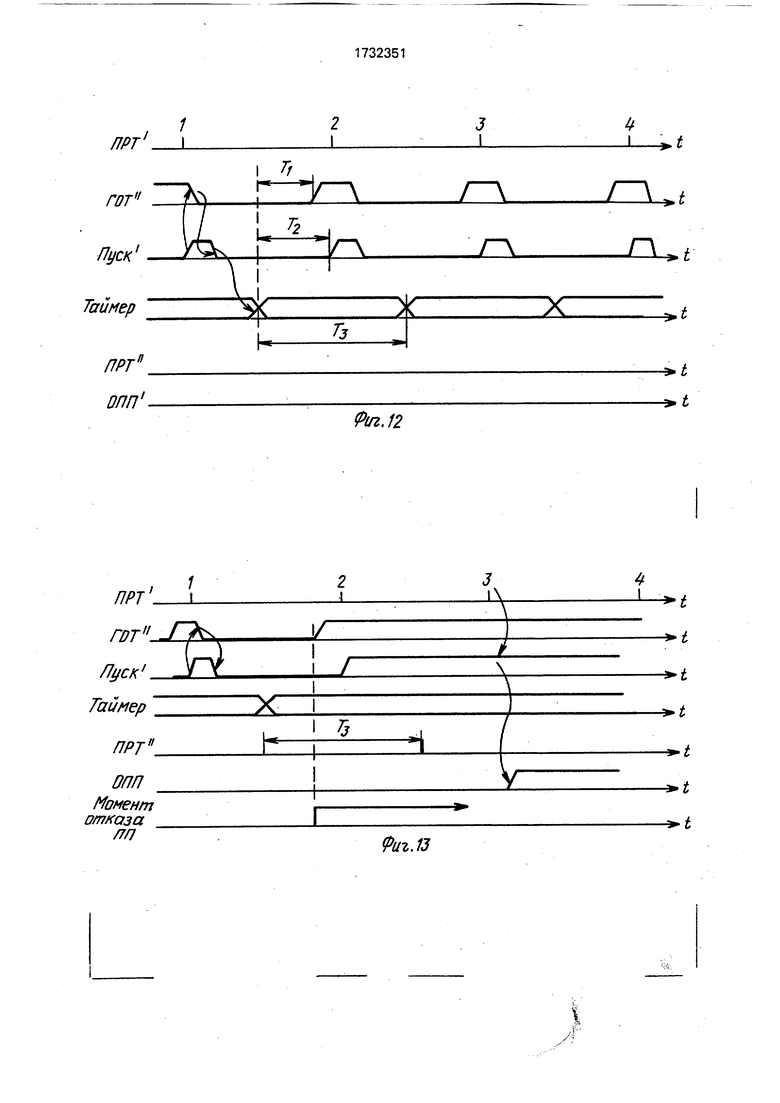

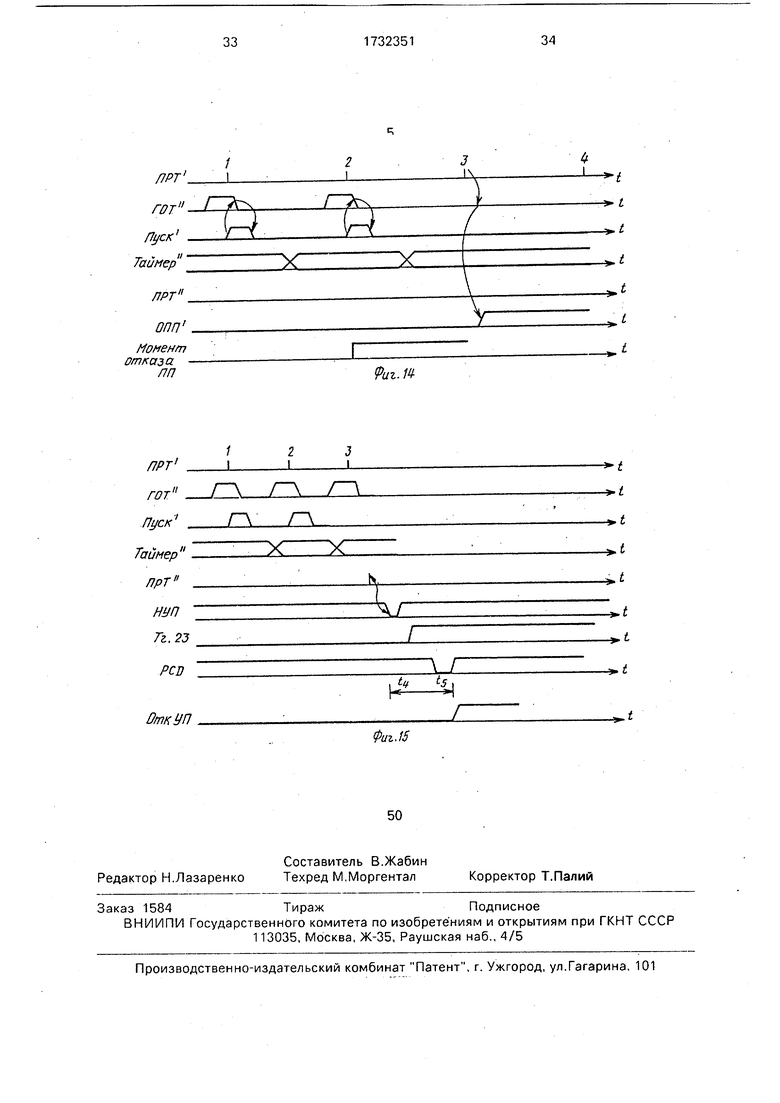

На фиг. 1 и 2 представлена структурная схема предлагаемой вычислительной системы; на фиг. 3 - вычислительный блок; на фиг. 4 - регистр состояния вычислительного блока; на фиг. 5 - коммутатор; на фиг. 6 - регистр состояния; на фиг. 7 - вычислительный Блок управляющего процессорного блока; на фиг. 8 и 9 - вычислительный блок подчиненного процессорного блока; на фиг. 10 - алгоритм работы управляющего процессорного блока; на фиг. 11 - алгоритм работы подчиненного процессорного блока; на фиг. 12 - временная диаграмма работы системы в исправном состоянии; на фиг. 13 - временная диаграмма работы системы при выходе из строя подчиненного процессорного блока после установки им сигнала ГОТ; на фиг. 14 - временная диаграмма работы системы при выходе из строя подчиненного процессорного блока после снятия им сигнала ГОТ; на фиг. 15 - временная диаграмма работы системы при выходе из строя управляющего процессорного блока и замены его работоспособным процессорным блоком.

Мультипроцессорная система (фиг. 1 и 2) содержит устройства ввод-вывода 1.1,...,1,к, соединенные через системную шину обмена информацией 2 с системной памятью 3 и портами ввода-вывода (шинами) 4.1, ..., 4.п процессорных блоков 5.15.п. Вход выбора управляющего процессорного блока 6.i каждого процессорного блока 5.i подключен к первому входу элемента И 7.I, информационному входу триггера управления коммутацией 8.1, первому входу элемента ИЛИ-НЕ 9.1 и входу выбора управляющего процессорного блока 10.S вычислительного блока 11,1. Выход признака неисправности управляющего процессорного блока 12.1 вычислительного блока 11.1 связан с входом синхронизации триггера управления коммутацией 8.1 и вторым входом элемента ИЛИ- НЕ 9.i, третий вход которого подключен к второму входу элемента И 7.1, выходу триггера отключения процессора 13.1 и входу 14.i блокировки вычислительного блока 11.1, выход 15.1 отключения процессорного блока 11.1 связан с входом установки в нуль триггера отключения процессора 13.1. Выход триггера управления коммутацией 8.i подключен к входу 16,1 управления коммутацией вычислительного блока 11.1 и входу установки в единицу триггера отключения процессора 13.1. Выход разрешения сдвига 17.1 вычислительного блока 11.1 связан с выходом управления сдвигом 18.i процессорного блока 5.i, вход 19.i управления сдвигом которого подключен к инверсному входу элемента И 20.i. Вход 21.1 отключения управляющего процессорного блока 5.1 через формирователь 22.1 связан с тактирующим входом триггера отключения процессора 13.1. Тактирующий вход триггера голосования 23.i соединен с выходом

элемента ИЛИ-НЕ 9.i, вход установки в единицу триггера голосования 23.1 является входом голосования процессорного блока 5.i, а прямой выход триггера голосования

23.1 подключен к первому входу элемента И 20.1, второй вход которого является входом сдвига процессорного блока 5.i. Выход элемента И 20. связан с элементом задержки 24.i, выход которого подключен ко входу ус0 тановки в нуль триггера голосования 23. и является также выходом голосования процессорного блока 5.I. Инверсный выход триггера голосования 23.i является выходом сдвига процессорного блока 5.I. На инфор5 мационный вход триггера голосования 23.I подается логическая единица. На вход установки в единицу триггера голосования 23.1 процессорного блока 5.1 подключен логический нуль. На информационный вход

0 триггера реконфигурации 25.п подается логическая единица.

Вход установки в нуль триггера реконфигурации 25.i является входом 33.i сброса процессорного блока 5.I, синхровходтригге5 ра реконфигурации 25.i подключен к тактирующим входу и выходу процессорного блока 5.i, а информационный вход триггера реконфигурации 25.i является входом реконфигурации процессорного блока 5.i, пря0 мой выход триггера реконфигурации 25.I подключен к выходу реконфигурации процессорного блока 5.i и через переключатель 26.I к выходу 27.i отключения управляющего процессорного блока. Шина 28 является ши5 ной отключения управляющего процессорного блока. Выход элемента И 7.i является выходом 29.1 выбора управляющего процессорного блока. Выход ЗОЛ вычислительного блока 11.1 соединен с выходом сброса триг0 гера реконфигурации 31.1 процессорного блока 5.I. Входы сдвига, реконфигурации и тактирования процессорного блока 5.i (i 1,п) соединены с одноименными выходами процессорного блока 5.(i+1), входы голосо5 вания и выбора которого подключены к одноименным выходам процессорного блока 5.. Выход голосования процессорного блока 5.п соединен с тактирующим входом процессорного блока 5.п.

0 Выходы отключения управляющего процессорного блока, сброса триггеров, управления сдвигом всех процессорных блоков через одноименные шины 28, 32. 34 соединены с одноименными входами всех процессорных

5 блоков 5.15.п.

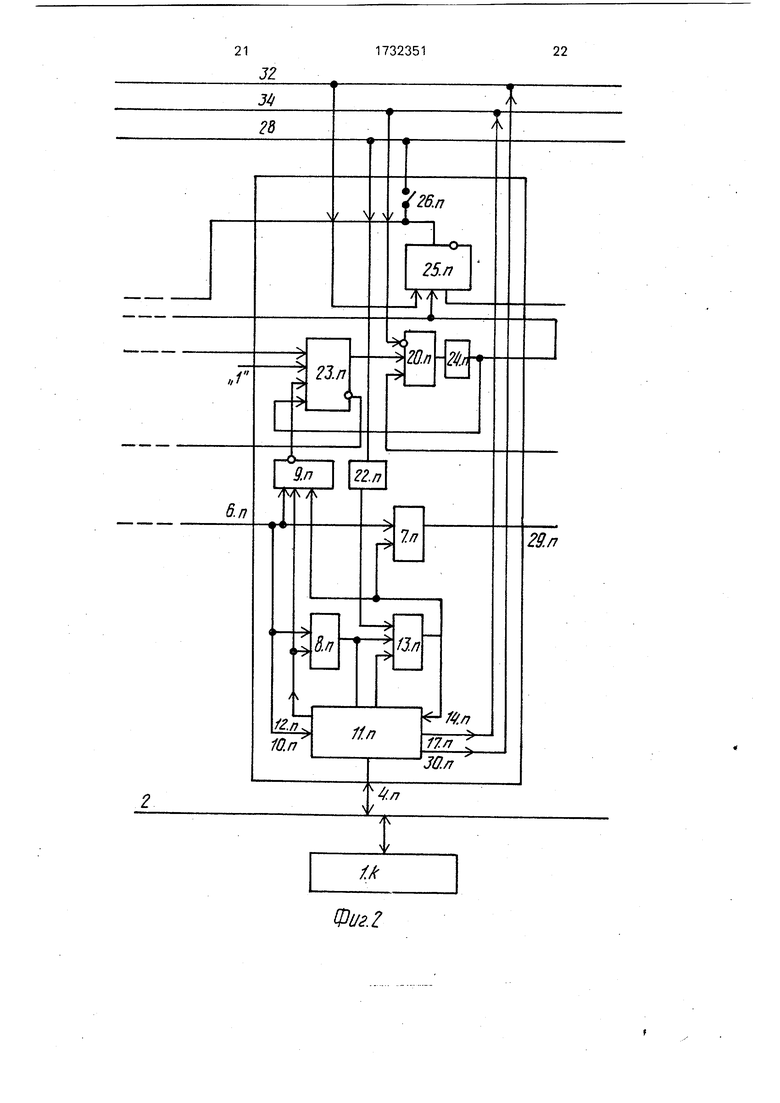

Пример построения вычислительного блока 11.1 представлен на фиг. 3. Системная шина 2 через коммутатор 35,i связана с локальным каналом обмена информацией 36.i, локальной памятью 37.1, процессором 38.1

первой группой входов регистра 39.i состояния. К локальному каналу 36.i подключены также процессор 38.i, регистр состояния 39.i и таймер 40.i. Выходы 15.1, 12.1, 17.1, 30.1 вычислительного блока 11.i являются выходами регистра 39.i состояния, а вход 10.1 вычислительного 11.1 связан с входом регистра 39.1 состояния. Два управляющих входа коммутатора 35.1 являются входами 14.1 и 16.1 вычислительного блока 11.1, а третий его управляющий вход подключен к одному из выходов регистра 39.1 состояния, который связан также с управляющим входом процессора 38.1.

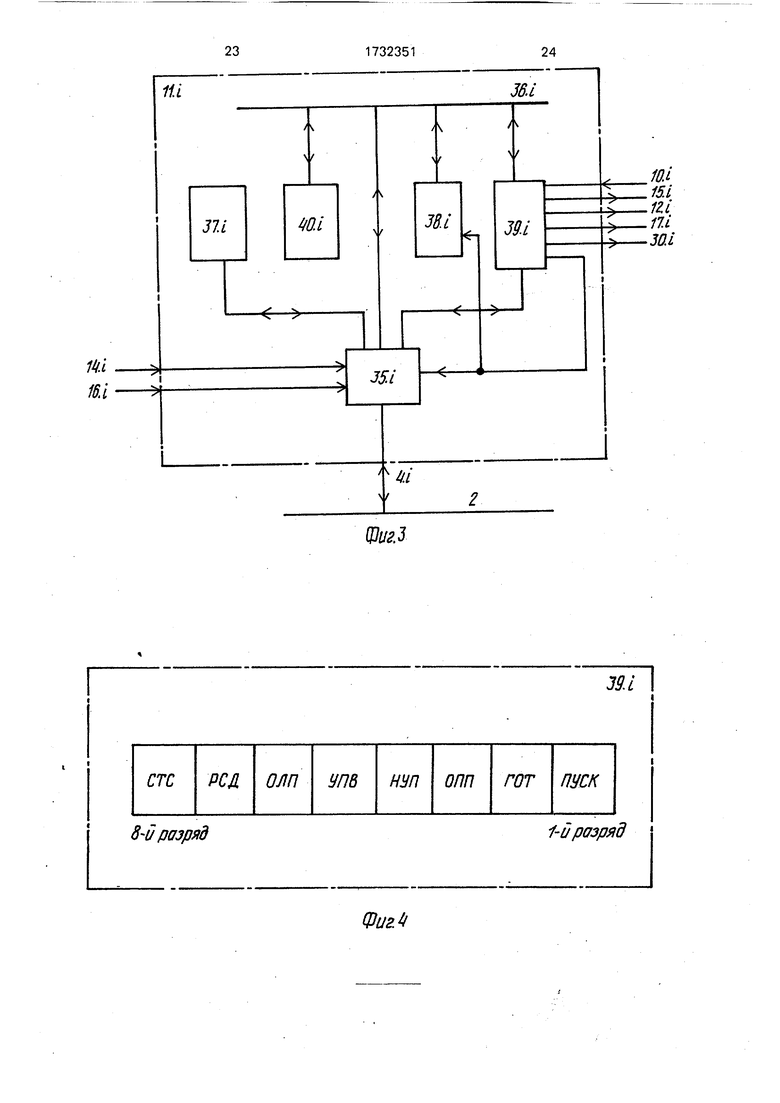

Возможный формат регистра 39.1 состояния представлен на фиг. 4. Назначение каждого разряда поясняется таблицей.

При таком формате регистра 39.1 состояния выходы 15.i, 12.1, 17.1 и 30.1 вычислительного блока 11,1 являются выходами соответственно 3-, 4-, 7- и 8-го разрядов регистра 39.1 состояния, к управляющему входу процессора 38.1 и коммутатора 35.1 подключен выход 6-го разряда регистра состояния, а вход 10.1 вычислительного блока 11.1 является входом 5-го разряда регистра 39.1 состояния.

Остальные разряды регистра 39.1 состояния доступны для чтения и записи со стороны системной шины 2 локального 36.1 канала обмена информацией в соответствии с таблицей.

Коммутатор 35.1 предназначен для передачи информации между шинами, в зависимости от управляющих сигналов, которые поступают на входы управления состоянием (выбран или не выбран) шинных формирователей 41.1-45.1. Выходы управления направлением передачи в шинных формирователях условно не показаны.

Вход 14.1 соединен с инверсным управляющим входом шинного формирователя 41.1, а вход 16.1 подключен к инверсным входам шинных формирователей 42.1, 44.1, первому инверсному вхйду формирователя 45.1 и входу шинного формирователя 43.1, второй инверсный вход шинного формирователя 45.1 и прямой вход формирователя 42.1 связаны с выходом 6-го разряда регистра состояния 39.1.

Системная шина 2 через шинные формирователи 41.1, 43.1 связана с локальным каналом 36.1 обмена информацией, а через шинный формирователь 49.1 с регистром состояния 39.1, через шинный формирователь 42.1 с локальной памятью 37.1, которая подключена посредством шинного формирователя 45.1 и локальному каналу 36.1 обмена информацией.

На фиг. 6 показана возможная схема регистра состояния 39.1. Регистр 39.1 содержит элементы ИЛ И (элементы 45.1,48.1), первый интерфейс 46.1, второй интерфейс 47.1,

триггеры 49.1-56.1, элементы с тремя состояниями (57.1, 58.1, 60.1). Информационный вход триггера 49.1 через первый элемент ИЛИ 45.1 соединен с системным 2 и локальным 36.1 каналами обмена информацией,

0 выход триггера 49.i подключен к первым входам элементов 57.1, 58.1. Вход первого интерфейса 46.I связан с системной шиной 2 обмена информацией, а первый его выход подключен ко второму входу элемента 57.i и

5 первому входу элемента 59.1, второй выход элемента 46.i связан с первым входом второго элемента ИЛИ 48.1 и синхронными входами триггеров 51.1 и 54.1.

Синхронный вход триггера 49.1 подклю0 чен к выходу элемента 48.1, второй вход которого связан с синхронными входами триггеров 50.1, 52.1, 55.1, 56.1 и первым выходом второго интерфейса 47., второй выход которого подключен к второму входу эле5 мента 58.1 и первому входу элемента 60,1, второй вход которого соединен с выходом триггера 54.1.

Вход второго интерфейса 47.1 соединен с локальным каналом 36.1 обмена информа0 цией.

Выходы элементов 58.1 и 60.1 подключены к локальному каналу 36.1, а выходы элементов 57.1 и 59.1 - к системному каналу 2, к которому также подключены информацион5 ные входы триггеров 51.1 и 54.1, а информационные входы триггеров 50.1, 52.1 и 56.1 связаны с локальным каналом 36.1. Выходы триггеров 51.1, 52.1, 55.1 и 56,1 связаны с выходами 15.1, 12.1, 17.1 и 30.1 вычислитель0 ного блока 11.1 соответственно. Входы 10.1 и 61.1 подключены к информационному и тактирующему входам триггера 53.1.

Вход 10.1 связан со входом 6.1 процессорного блока 5.1, а вход 61.1 является

5 внутренним тактирующим входом вычислительного блока 11.1,

Выход 62.1 триггера 54.1 является управляющим входом коммутатора 35.1.

Система работает следующим образом.

0 Процессорный блок 5.1, например, на вход 6.1 которого подается единичный потенциал, выполняет функции управляющего

процессорного блока. На входах 6.2б.п

процессорных блоков 5.25.п в исходном

5 состоянии установлены нулевые потенциалы. Эти процессорные блоки 5.25.п являются подчиненными.

Управляющий процессорный блок 5.1 имеет доступ к системной памяти 3, устройствам ввода-вывода 1.11.k, а также через

соответствующие порты ввода-вывода (шины 4.24.п) к подчиненным процессорным блокам 5.25.п. Он может передавать команды для подчиненных процессорных блоков 5.2, .... 5.п и читать слово состояния этих процессорных блоков (5.2, ..., 5.п). Соответствующими командами осуществляется запуск процессорных блоков 5.2, ..., 5.п, отключение при неисправности одного или нескольких подчиненных процессорных блоков, а также обеспечивается доступ к их локальной (внутренней) памяти (37.2,..., 37.п). Запуск подчиненного процессорного блока 5. осуществляется командой Пуск, которая устанавливает в единичное состояние младший разряд регистра 39.1 состояния (фиг. 4 и 6), отключение подчиненного процессорного блока - командой Отключить подчиненный процессорный блок (установка в единицу 3-го разряда регистра 39.1 состояния (ОПП), а доступ к локальной памяти осуществляется командами Открыть локальную память (запись единицы в 6-й разряд) и Закрыть локальную память (установка в нуль 6-го разряда регистра 39.i (ОЛП)).

Если вычислительный блок 11.i имеет структуру, показанную на фиг. 3, то управляющий процессорный блок 5.1 будет иметь конфигурацию в соответствии с фиг. 7, т.е. процессор 38.1 регистра 39.1 состояния и таймер 40.1 подключены к системному каналу 2 обмена информацией.

Каждый вычислительный блок 11.2

11.п подчиненных процессорных блоков 5.2,.... 5.п в режиме работы имеет конфигурацию, показанную на фиг. 8. При такой структуре регистр 39.i состояния доступен как со стороны системной шины 2, так и со стороны локального канала 36.1, через который процессор 38.i осуществляет обмен информацией со своей локальной памятью 37. и своим таймером 40.i.

При поступлении команды обращения к локальной памяти (Открыть локальную память) конфигурация вычислительного блока 11 .i подчиненного процессорного блока 5.1 изменится и будет иметь вид, показан- нь|й на фиг. 9. В этом случае локальная память 37.i и регистр 39.i состояния подключены к системной шине 2, т.е. доступны для управляющего процессорного блока 5.1.

8 процессе обращения к локальной памяти 37.i со стороны системной шины 2 процессор 38.i вычислительного блока 11.1 переводится в режим ожидания (например, подачей с выхода 6-го разряда регистра 39. состояния сигнала Требования прямого доступа (захвата шины), который предусмотрен в любом серийно выпускаемом микро процессоре).

В исходном состоянии, как указано выше, функции управляющего процессорного

блока выполняет процессорный блок 5.1, а

подчиненные - процессорные блоки 5.2

5.п.

При включении системы производится начальная установка регистров состояний

0 39.139.п. Аппаратным путем разряды

этих регистров устанавливаются в следующие состояния: Пуск О ГОТ 0; ОПП 0; НУП 1; УПВ 0; ОЛП 0; РСД 1; СТС 1.

5 В соответствии с этим на выходах триггеров отключения процессоров 13.113.п

присутствуют нулевые потенциалы. Так как на вход 10.1 вычислительного блока 11.1 поступает со входа процессорного блока 6.1

0 управляющего процессорного блока 5.1 единичный потенциал, то 5-й разряд (УПВ) регистра 39.1 состояния устанавливается в единицу. В остальных же процессорных блоках 5.2,.... 5.п на входах 6.2б.п будут

5 присутствовать нулевые потенциалы, так как все элементы 7.1,..., 7.п будут закрыты, вследствие чего 5-й разряд регистров состояний этих блоков останется в нуле. Только в процессорном блоке 5.1 триггер 8.1 устано0 вится в единицу, так как при единичном потенциале с выхода 12.1 вычислительного блока 11.1 поступающем на тактирующий вход триггера 8.1, последний пропускает единичный сигнал со своего информацион5 ного входа на выход (например, в качестве

триггера 8.18.п можно использовать Dтриггеры, управляемые уровнем тактирующего сигнала, которые при единичном потенциале пропускают информацию со

0 входа D на выход, а при переходе к нулевому уровню защелкивают в триггерах информацию, имеющуюся на входе непосредственно перед этим). Сигнал с выхода триггера 8.1 поступает на вход управления коммутацией

5 16.1 вычислительного блока 11.1 и настраивает коммутатор 35.1 таким образом, что он соединяет системную шину обмена информацией 2 с локальным каналом 36.1 обмена информацией, т.е. процессорный блок 5.1

0 принимает конфигурацию управляющего процессорного блока (фиг. 7).

Таким образом, в процессе работы в управляющем процессорном блоке 5.1 триггер 8.1 находится в единичном состоянии, а

5 триггеры 8.2 8.п процессорных блоков

5,2 5.п - в нулевом состоянии; кроме

этого, триггеры 23.1, ..., 23.п голосования и триггеры 25.125.п реконфигурации установлены также в нулевое состояние. Следовательно, вычислительные блоки 11.2 11.п

имеют конфигурацию показанную на фиг. 8 или 9, т.е. выполняют функции подчиненных процессорных блоков.

В начале работы системы управляющий процессорный блок 5.1 осуществляет инициализацию системы (фиг. 10), т.е. загружает данные и программы в локальную память подчиненных процессорных блоков и производит из запуск. Для загрузки данных и программ в подчиненные процессорные блоки 5.25.п подается команда Открыть локальную память, затем осуществляются циклы обращения к открытой локальной памяти, после чегр локальная память закрывается командой Закрыть локальную память.

После этого по команде Пуск, которая поступает поочередно на каждый процессорный блок 5.25.п, подчиненные процессорные блоки начинают выполнять свои программы.

Далее запускается таймер 40.1 управляющего процессорного блока 5.1, который через одинаковые промежутки времени, называемые тактом системы, осуществляет прерывание работы управляющего процессорного блока 5.1.

Такт системы выбирается в зависимости от времени выполнения программ подчиненными процессорными блоками 5.2

5.п.

После запуска таймера 40.1 управляющий блок 5.1 выполняет свою основную программу, которая будет приостановлена очередным прерыванием от таймера. По этому прерыванию управляющий процессорный блок 5.1 переходит на подпрограмму проверки работоспособности и запуска

подчиненных процессорных блоков 5.2

5.п. При этом поочередно читаются слова состояния каждого процессорного блока 5.25.п. Если в слове состояния очередного процессорного блока 5.i (фиг. 10) в разряде ГОТ записана единица (i 1), а в разряде Пуск записан нуль( 0), то управляющий процессорный блок 5.1 переходит к анализу слова состояния следующего процессорного блока 5.1+1. Если же отсутствует сигнал ГОТ или имеется единица в разряде Пуск, то подчиненный процессорный блок считается отказавшим и отключается командой Отключить подчиненный процессорный блок. После этого управляющий процессорный блок 5.1 останавливает свой таймер 40.1 и переходит к программе инициализации системы. При этом осуществляется перераспределение задач для оставшихся процессорных блоков, загрузка данных и программ в эти процессорные блоки, упорядочивания номеров и числа оставшихся процессорных блоков. Затем

осуществляется их запуск и запуск таймера управляющего процессорного блока 5.1, после чего последний переходит на выполнение своей основной программы.

Если при выполнении подпрограммы по

прерыванию от таймера управляющего блока 5.1 отказавшие процессоры отсутствуют, то осуществляется поочередный запуск подчиненных процессорных блоков и возврат

0 из подпрограммы.

Каждый подчиненный процессорный блок 5.2, ..., 5.п работает в соответствии с алгоритмом на фиг. 11. Вначале каждого системного такта подчиненный процессорный

5 блок 5.I ожидает своего запуска, т.е. анализирует разряд Пуск своего регистра 39.i состояния, который устанавливается со стороны системного канала 2 управляющим процессорным блоком 5.1. При наличии еди0 ницы в разряде Пуск снимают сигналы ГОТ и Пуск, т.е. устанавливают в нуль 1- и 3-й разряды регистра 39. состояния (фиг. 4 и 6). Затем запускают таймер 40.i и переходят на выполнение основной программы,

5 которая может включать и программу диагностики.

После завершения программы устанавливают в единичное состояние разряд ГОТ в регистре 39.i.

0 Если все процессорные блоки 5.25.п

в системе работают правильно, то временная диаграмма обмена сигналами между управляющим блоком 5.1 и каждым подчиненным процессорным блоком соответству5 етфиг. 12.

На диаграмме сигналы, вырабатываемые в управляющем блоке 5.1, отмечены одним штрихом, а в подчиненном - двумя штрихами.

0 Заметим, что период времени Ti соответствует времени выполнения основной программы в подчиненном процессорном блоке 5.I, а Та - промежуток времени от момента запуска таймера подчиненного

5 процессорного блока до поступления следующей команды Пуск от управляющего процессорного блока 5.1; Тз - расчетное время работы таймера подчиненного процессорного блока 5.I. Этот таймер должен

0 вырабатывать запрос на прерывание через промежуток времени больше чем Та.

Рассмотрим работу системы при отказе подчиненного процессорного блока 5.i. Отказ подчиненного процессорного блока мо5 жет произойти после того, как он установил сигнал ГОТ, и после того, как он этот сигнал снял (анализируются соответствующие разряды регистра состояния).

В первом случае отключение отказавшего процессорного блока 5.i осуществляется в соответствии с диаграммой, показанной на фиг. 13, во втором случае - как показано на фиг. 14. И в том, и в другом случае подчиненный процессорный блок выходит из строя после завершения прграм- мы в первом такте.

Как видно из диаграмм, команда Отключить подчиненный процессорный блок вырабатывается вначале третьего такта, поскольку в первом случае не снят сигнал Пуск, а во втором случае не выставлен сигнал ГОТ в регистре 39.i состояния (см. алгоритм работы управляющего процессорного блока на фиг. 10). Заметим, что в первом случае (фиг, 13) таймер 40.i отказавшего подчиненного процессорного блока 5, через промежуток времени Тз может выставить запрос на прерывание работы отказазшего блока 5.I. Этот запрос не оказывает на работу всей системы влияния, так как отказавший процессорный блок 5.I будет отключен в следующем системном такте управляющим процессорным блоком 5.1.

Таким образом, отключение, отказавшего подчиненного процессорного блока 5.i осуществляется программно, путем анализа слова состояния этого процессора вначале каждого системного такта, В отключенном процессорном блоке с помощью сигнала на выходе отключения подключенного процессора 15.1 (путем установки единицы в 3-й разряд (ОПП) регистра 39.1 обеспечивается единичный потенциал на выходе триггера отключения процессора, который открывает по одному из входов элемент 7.i, за счет чего обеспечивается передача сигнала с входа 6.1 на выход 29.1 отказавшего процессорного блока 5.1.

Кроме того, сигнал с выхода блока 13.1 отключает от системной шины 2 обмена информацией вычислительный блок 11.i, поступая на вход 14.1 этого блока, и осуществляет поступление единичного сигнала на один из входов элемента ИЛИ-НЕ 9,i,

В мультипроцессорной системе одновременно с управляющим процессорным блоком допускается выход из строя на- скольких подчиненных процессорных блоков, что определяется выбранной стратегией голосования подчиненных блоков за отключение управляющего прцессерного блока. Если система может выполнять свои функции при наличии к (k n) подчиненных процессорных блоков, то управляющий процессорный блок считается неисправным, если за его отключение проголосовало k из n процессорных блоков.

В исходном состоянии определяется минимально возможное число подчиненных процессорных блоков и замыкается переключатель 26.(п - k + 1), находящийся в процессорном блоке 5.(п - k + 1), остальные переключатели 26.j(j Ј (n -k + 1)) находятся в разомкнутом состоянии.

Если управляющий процессорный блок

5,1 выходит из строя, то он заменяется работоспособным процессорным блоком, который находится первым справа (фиг. 1 и 2) от управляющего процессорного блока

0 5.1 (не считая отключение процессорные, блоки). Если отключенных процессорных блоков нет, то функции управляющего процессорного блока начинает выполнять процессорный блок 5.2.

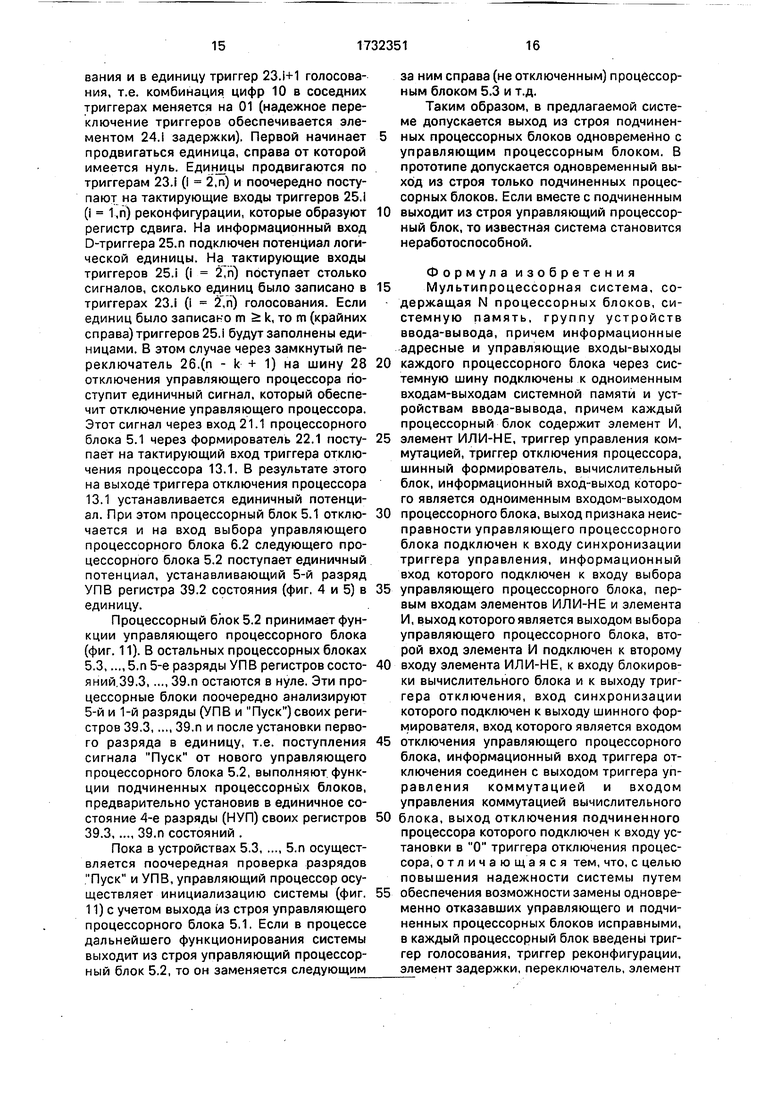

5 Это осуществляется следующим образом, Как следует из фиг. 11, подчиненные процессорные блоки 5.25.п вначале каждого системного такта ожидают сигнал Пуск от управляющего процессорного

0 блока 5.1. При этом (фиг. 15), если сигнал Пуск от управляющего процессорного блока 5.1 не поступает (на фиг. 15, 3-й такт), подчиненный процессорный блок 5.I переходит на подпрограмму обслуживания пре5 рывания от своего таймера 40.i.

В этом случае происходит выработка сигнала (НУП) неисправности управляющего процессорного блока. На выходе 12.1 вычислительного блока 11.1 появляется сигнал

0 низкого уровня, 4-й разряд регистра 39.i состояния на определенное время сбрасывается в нулевое состояние.

Следовательно, на выходе элемента ИЛИ-НЕ 9.i появляется потенциал, который,

5 поступая на тактирующий вход триггера 23.1 голосования устанавливает его в единичное состояние. Через промежуток времени м (фиг, 15), после выработки сигнала НУП, на время ts устанавливается низкий потенци0 ал РСД на выходе разрешения сдвига 17.1 вычислительного блока 11.1. Для этого в 7-й разряд регистра состояния записывается нуль (РСД 0) на время ts.

Промежуток времени t-з учитывает вре5 мя разброса установки триггеров 23.2

23.n во всех подчиненных процессорных блоках 5.2, ..., 5.п, например, в случае из поочередного запуска (фиг. 10). При выработке сигнала РСД на шине 34 устанавлива0 ется низкий уровень сигнала, который поступает на инверсный вход элемента 20.i (i 2,n). Единицы, записанные в триггерах 23.1 (i 2,п), начинают сдвигаться вправо в соседние триггеры 23.1+1 голосования. Это

5 осуществляется следующим образом. Если в триггере 23.i голосования записана единица, а в триггере голосования 23.1+1 записан ноль, то срабатывает элемент 20.i и сигнал с выхода элемента 24.i задержки устанавливают в нуль триггер 23.1 голосования и в единицу триггер 23.1+1 голосования, т.е. комбинация цифр 10 в соседних триггерах меняется на 01 (надежное переключение триггеров обеспечивается элементом 24.i задержки). Первой начинает продвигаться единица, справа от которой имеется нуль. Единицы продвигаются по триггерам 23.i (I 2,п) и поочередно поступают на тактирующие входы триггеров 25.1 (i 1,п) реконфигурации, которые образуют регистр сдвига. На информационный вход D-триггера 25.п подключен потенциал логической единицы. На тактирующие входы триггеров 25.i (i 2,п) поступает столько сигналов, сколько единиц было записано в триггерах 23.i (i 2,п) голосования. Если единиц было записано m к, то m (крайних справа) триггеров 25.1 будут заполнены единицами. В этом случае через замкнутый переключатель 26.(n - k + 1) на шину 28 отключения управляющего процессора поступит единичный сигнал, который обеспечит отключение управляющего процессора. Этот сигнал через вход 21.1 процессорного блока 5.1 через формирователь 22.1 поступает на тактирующий вход триггера отключения процессора 13.1. В результате этого на выходе триггера отключения процессора 13.1 устанавливается единичный потенциал. При этом процессорный блок 5.1 отключается и на вход выбора управляющего процессорного блока 6.2 следующего процессорного блока 5.2 поступает единичный потенциал, устанавливающий 5-й разряд УПВ регистра 39.2 состояния (фиг, 4 и 5) в единицу.

Процессорный блок 5.2 принимает функции управляющего процессорного блока (фиг. 11). В остальных процессорных блоках

5.35.п 5-е разряды УПВ регистров состояний.39.339.n остаются в нуле. Эти процессорные блоки поочередно анализируют 5-й и 1-й разряды (УПВ и Пуск) своих регистров 39.339.n и после установки первого разряда в единицу, т.е. поступления сигнала Пуск от нового управляющего процессорного блока 5.2, выполняют функции подчиненных процессорных блоков, предварительно установив в единичное состояние 4-е разряды (НУП) своих регистров 39.339.n состояний .

Пока в устройствах 5.3, .... 5.п осуществляется поочередная проверка разрядов Пуск и УПВ, управляющий процессор осуществляет инициализацию системы (фиг. 11) с учетом выхода из строя управляющего процессорного блока 5.1. Если в процессе дальнейшего функционирования системы выходит из строя управляющий процессорный блок 5.2, то он заменяется следующим

за ним справа (не отключенным) процессорным блоком 5.3 и т.д.

Таким образом, в предлагаемой системе допускается выход из строя подчиненных процессорных блоков одновременно с управляющим процессорным блоком. В прототипе допускается одновременный выход из строя только подчиненных процессорных блоков. Если вместе с подчиненным

выходит из строя управляющий процессорный блок, то известная система становится неработоспособной.

Формула изобретения

Мультипроцессорная система, содержащая N процессорных блоков, системную память, группу устройств ввода-вывода, причем информационные адресные и управляющие входы-выходы

каждого процессорного блока через системную шину подключены к одноименным входам-выходам системной памяти и устройствам ввода-вывода, причем каждый процессорный блок содержит элемент И,

элемент ИЛИ-НЕ, триггер управления коммутацией, триггер отключения процессора, шинный формирователь, вычислительный блок, информационный вход-выход которого является одноименным входом-выходом

процессорного блока, выход признака неисправности управляющего процессорного блока подключен к входу синхронизации триггера управления, информационный вход которого подключен к входу выбора

управляющего процессорного блока, первым входам элементов ИЛИ-НЕ и элемента И, выход которого является выходом выбора управляющего процессорного блока, второй вход элемента И подключен к второму

входу элемента ИЛИ-НЕ, к входу блокировки вычислительного блока и к выходу триггера отключения, вход синхронизации которого подключен к выходу шинного формирователя, вход которого является входом

отключения управляющего процессорного блока, информационный вход триггера отключения соединен с выходом триггера управления коммутацией и входом управления коммутацией вычислительного

блока, выход отключения подчиненного процессора которого подключен к входу установки в О триггера отключения процессора, отличающаяся тем, что, с целью повышения надежности системы путем

обеспечения возможности замены одновременно отказавших управляющего и подчиненных процессорных блоков исправными, в каждый процессорный блок введены триггер голосования, триггер реконфигурации, элемент задержки, переключатель, элемент

И, выход которого соединен с входом элемента задержки, выход которого подключен к входу установки в О триггера голосования и является выходом голосования процессорного блока, тактирующий вход триггера голосования соединен с выходом элемента ИЛИ-НЕ, вход установки в 1 триггера голосования является входом голосования процессорного блока, прямой выход триггера голосования соединен с первым входом элемента И, инверсный вход которого является входом управления сдвигом процессорного блока, второй вход элемента И является входом сдвига процессорного блока, инверсный выход триггера голосова- ния является выходом сдвига процессорного блока, вход установки в О триггера реконфигурации является входом сброса процессорного блока, синхровход триггера реконфигурации подключен к тактирующим

входу и выходу процессорного блока, вход установки в 1 триггера реконфигурации является входом реконфигурации процессорного блока, выход триггера реконфигурации подключен к выходу реконфигурации процессорного блока и через переключатель - к выходу отключения управляющего процессора процессорного блока, входы сдвига, реконфигурации, тактирования и выходы выбора, голосования i-ro (i 1,n) процессорного блока соединены с одноименными выходами и входами (1+1)-го процессорного блока, выход голосования п-го процессорного блока соединен с тактирующим входом п-го процессорного блока, выходы сброса, управления сдвигом и отключения управляющего процессора всех процессорных блоков через одноименные шины соединены с одноименными входами всех процессорных блоков.

Фиг. 2

/#

ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система | 1991 |

|

SU1820391A1 |

| Мультипроцессорная система | 1987 |

|

SU1524063A1 |

| Устройство для сопряжения процессоров с общей шиной мультипроцессорной системы | 1988 |

|

SU1571606A1 |

| Устройство обработки данных для многопроцессорной системы | 1988 |

|

SU1683039A1 |

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

| Мажоритарно-резервированная магистральная модульная вычислительная система | 1986 |

|

SU1457643A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Многопроцессорная система | 1988 |

|

SU1522228A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

Мультипроцессорная система относится к вычислительной технике и может быть использована для построения мультипроцессорных систем с возможностью отключения отказавших процессорных блоков и замены их исправными. Целью предполагаемого изобретения является повышение надежности системы путем замены отказавших управляющего и подчиненных процессорных блоков работоспособными процессорными блоками. Мультипроцессорная система содержит устройства ввода-вывода, соединенные через системный канал обмена информацией с системной памятью и процессорными блоками. В состав каждого процессорного блока входит вычислительный блок, триггер управления коммутацией, триггер голосования, триггер реконфигурации, триггер отключения управляющего процессора, элементы И, ИЛИ-НЕ, формирователь, переключатель. 15 ил„ 1 табл.

8-иразряд

1-йразряд

Фиг

f

ш

V

ш

ш

/(каналу 36. L

Фиг.5

/С сис/лемному кяналу 2

Ш

л

л v

ft

ш

-

/ f

/

Яблоку Мз б-го разряда Jff.l блока 39i

№.Ј

№

Ш

fe7

Риг. 8

( Начало j

Инициализация ct/c/лемй/

Запуск

таймера

УЛ

Лрограмма УЛ

( Конец j

Фиг 10

Фиг. 9

Mffl/аЛО Ј 06 О/77й/ /70

frpept/SffHi/so от /пай- мера //7J

(ffjf/ ff/7J)

(началоj

Запуск таймера ПП

Программа ЛП

rOTL: 1

( Конец J

(

Hat/оло работы ло ярерь/Яаних) о/т /тгаймера

)

Услп..25

Яереход на /7О&/7рог/ 0мAfl/ /Я

Фиг. 11

/7РТ

Таймер

ПРТ ОПП1.

+ t

Риг. 12

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультипроцессорная система | 1987 |

|

SU1524063A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-07—Публикация

1990-05-21—Подача