Изобретение относится к вычислительной технике и может быть использовано при построении отказоустойчивых управляющих и вычислительных систем.

Цель изобретения - повышение надежности функционирования.

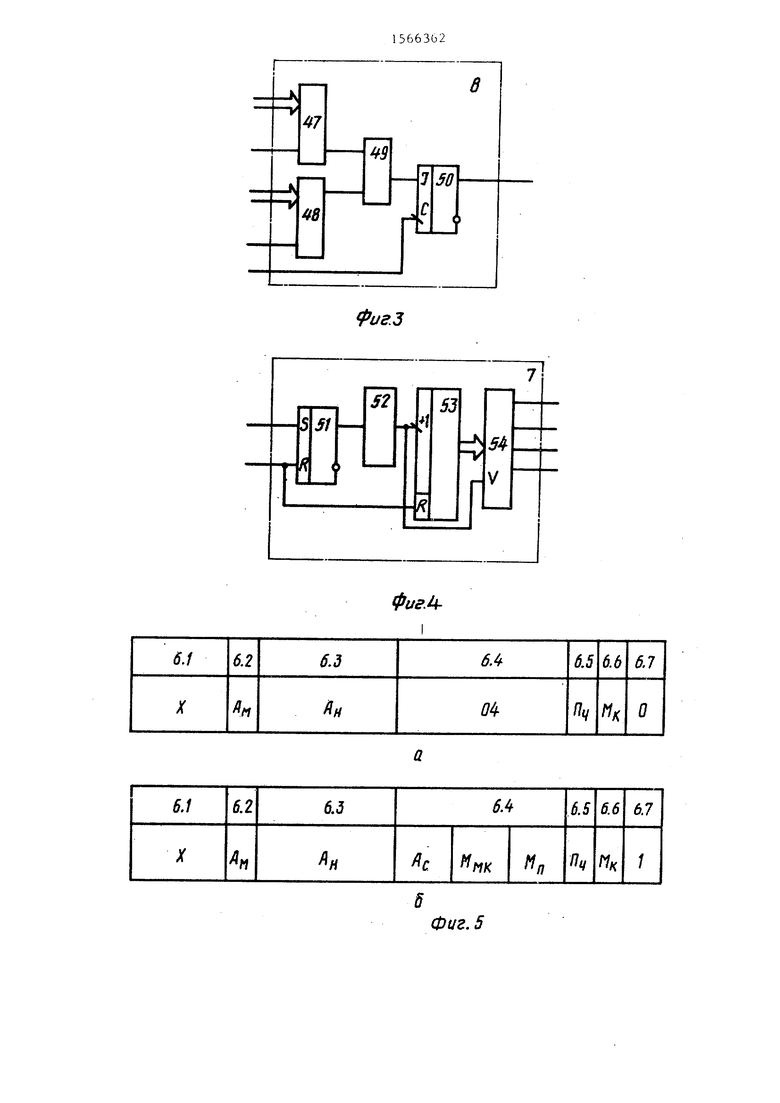

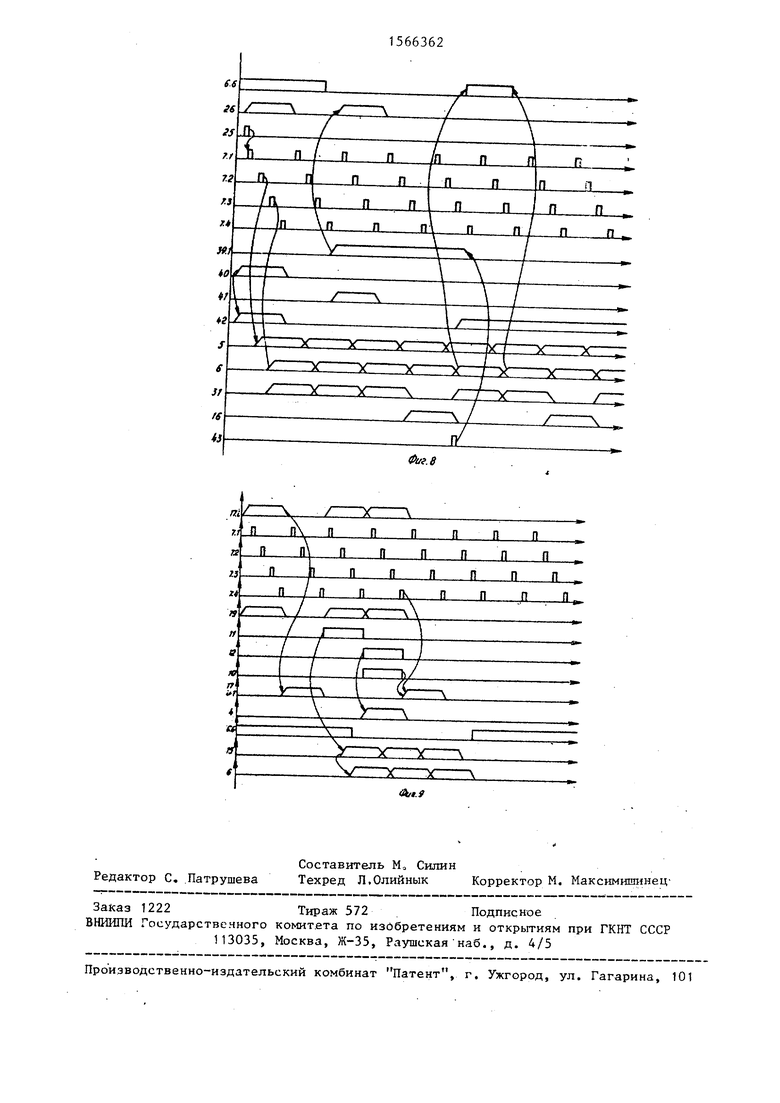

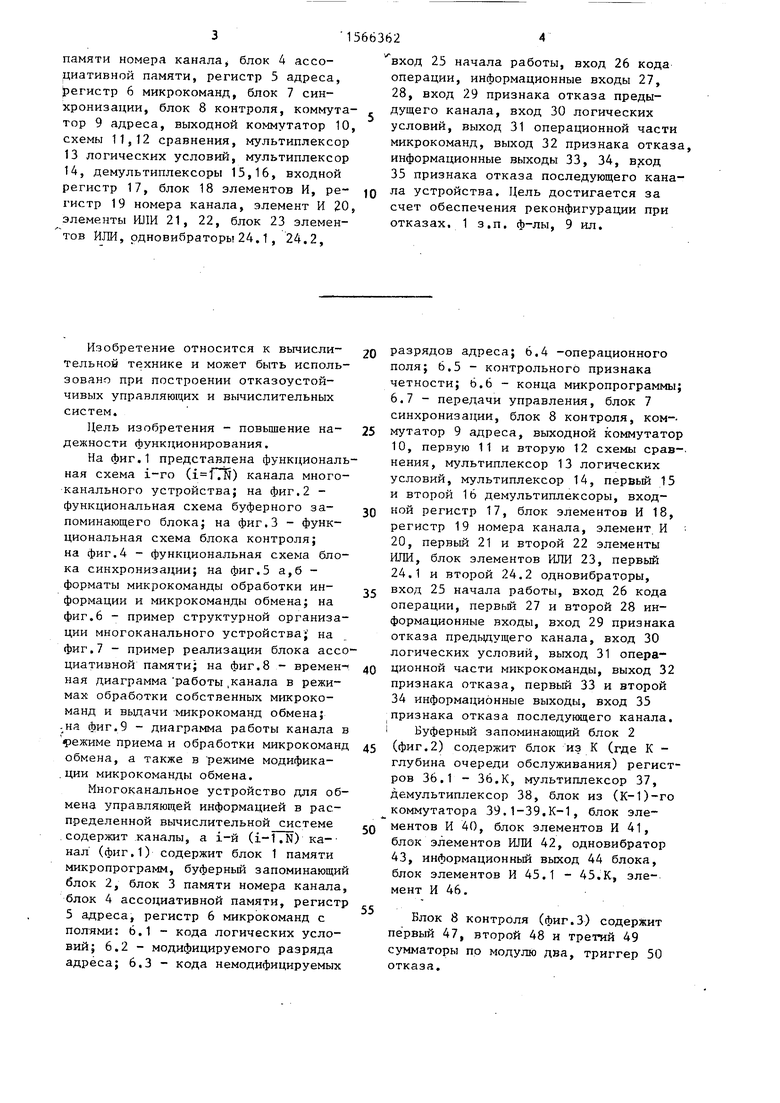

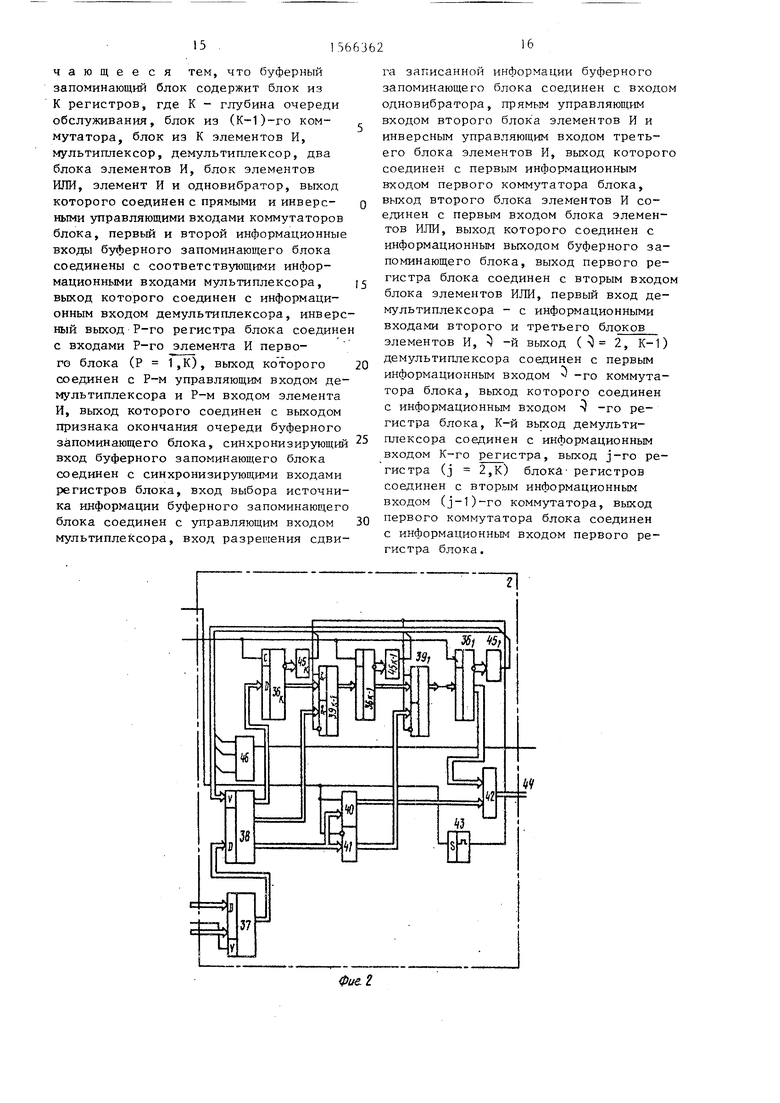

На фиг.1 представлена функциональная схема 1-го ( JNf) канала многоканального устройства; на фиг.2 - функциональная схема буферного запоминающего блока; на фиг.З - функциональная схема блока контроля; на фиг.4 - функциональная схема блока синхронизации; на фиг.5 а, б - форматы микрокоманды обработки информации и микрокоманды обмена; на фиг.6 - пример структурной организации многоканального устройства; на фиг.7 - пример реализации блока ассоциативной памяти; на фиг.8 - времен- ная диаграмма работы .канала в режимах обработки собственных микрокоманд и выдачи микрокоманд обмена; -на фиг.9 - диаграмма работы канала в режиме приема и обработки микрокоманд обмена, а также в режиме модификации микрокоманды обмена.

Многоканальное устройство для обмена управляющей информацией в распределенной вычислительной системе содержит каналы, а i-й (i-I.N) канал (фиг.1) содержит блок 1 памяти микропрограмм, буферный запоминающий блок 2, блок 3 памяти номера канала, блок 4 ассоциативной памяти, регистр 5 адреса, регистр 6 микрокоманд с полями: 6.1 - кода логических условий; 6.2 - модифицируемого разряда адреса; 6.3 - кода немодифицируемых

разрядов адреса; 6.4 -операционного поля; 6.5 - контрольного признака четности; 6.6 - конца микропрограммы; 6.7 - передачи управления, блок 7 синхронизации, блок 8 контроля, ком-мутатор 9 адреса, выходной коммутатор 10, первую 11 и вторую 12 схемы срав-. нения, мультиплексор 13 логических условий, мультиплексор 14, первый 15 и второй 16 демультиплексоры, входной регистр 17, блок элементов И 18, регистр 19 номера канала, элемент И 20, первый 21 и второй 22 элементы ИЛИ, блок элементов ИЛИ 23, первый 24.1 и второй 24.2 одновибраторы,

вход 25 начала работы, вход 26 кода операции, первый 27 и второй 28 информационные входы, вход 29 признака отказа предыдущего канала, вход 30 логических условий, выход 31 операционной части микрокоманды, выход 32 признака отказа, первый 33 и второй 34 информационные выходы, вход 35 признака отказа последующего канала, Буферный запоминающий блок 2

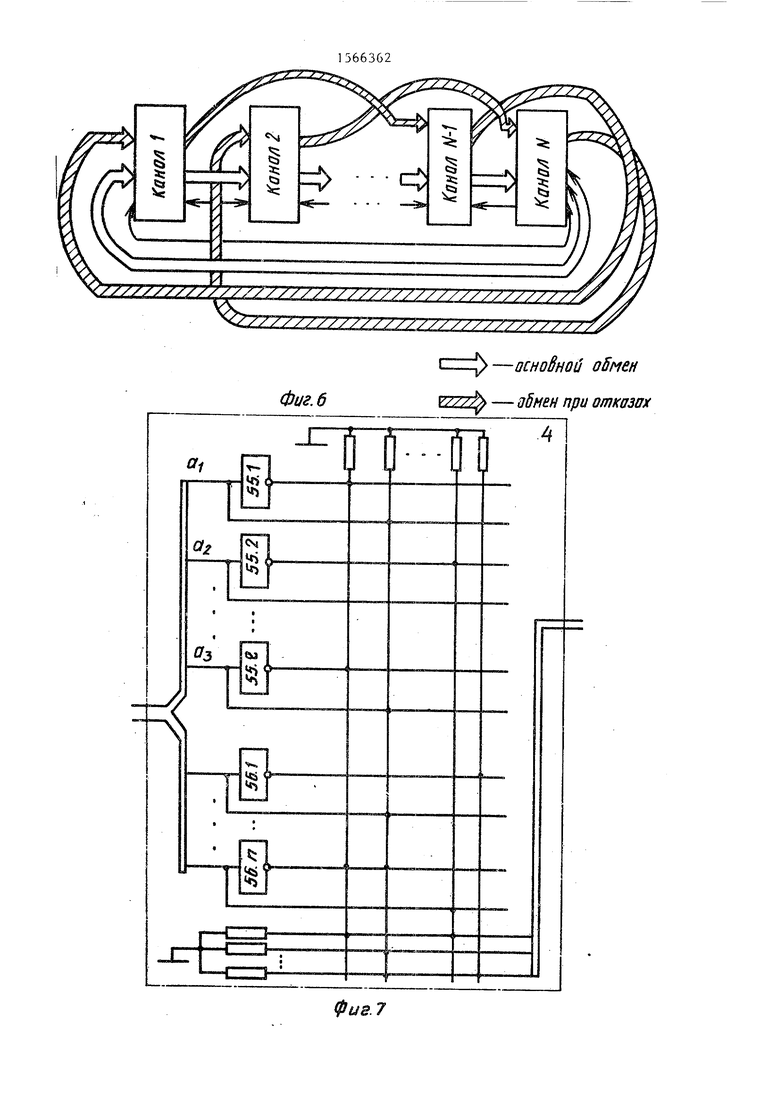

(фиг.2) содержит блок из К (где К - глубина очереди обслуживания) регистров 36.1 - 36,К, мультиплексор 37, демультиплексор 38, блок из (К-1)-го коммутатора 39.1-39.К-1, блок элементов И 40, блок элементов И 41, блок элементов ИЛИ 42, одновибратор 43, информационный выход 44 блока, блок элементов И 45.1 - 45.К, элемент И 46.

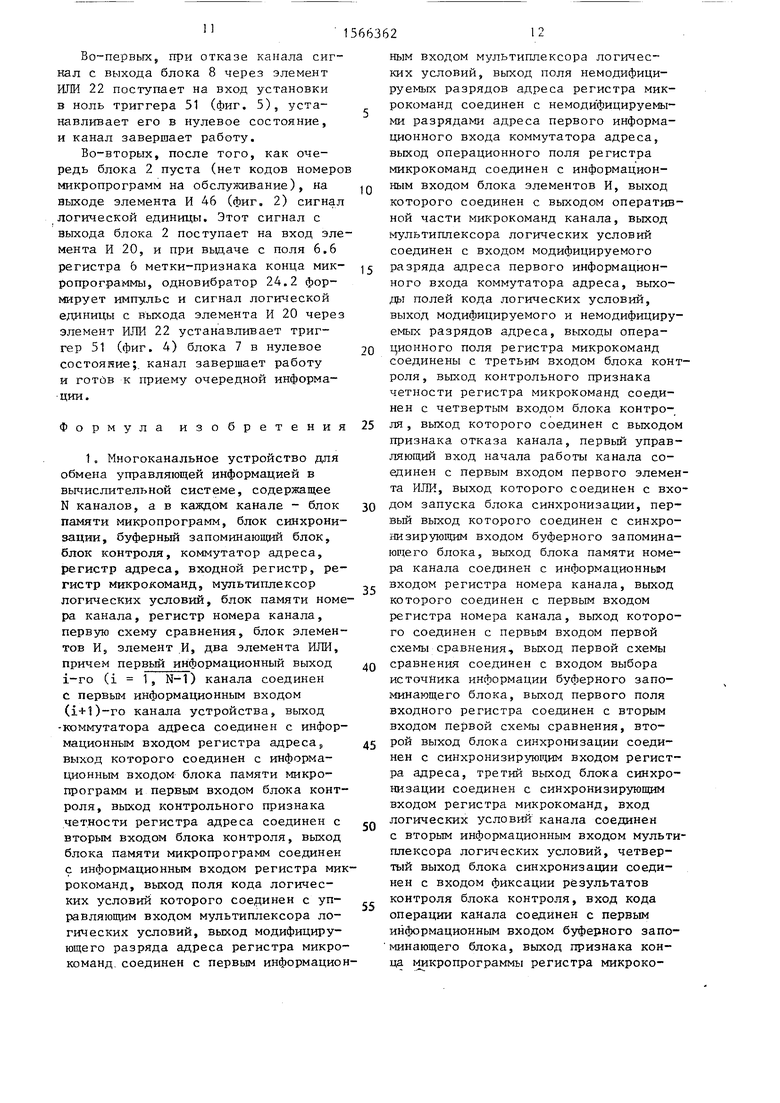

Блок 8 контроля (фиг.З) содержит первый 47, второй 48 и третий 49 сумматоры по модулю два, триггер 50 отказа.

10

Блок 7 синхронизации (фиг.4) со- держит триггер 51 запуска, генератор 52 тактовых импульсов, счетчик 53 и дешифратор 54.

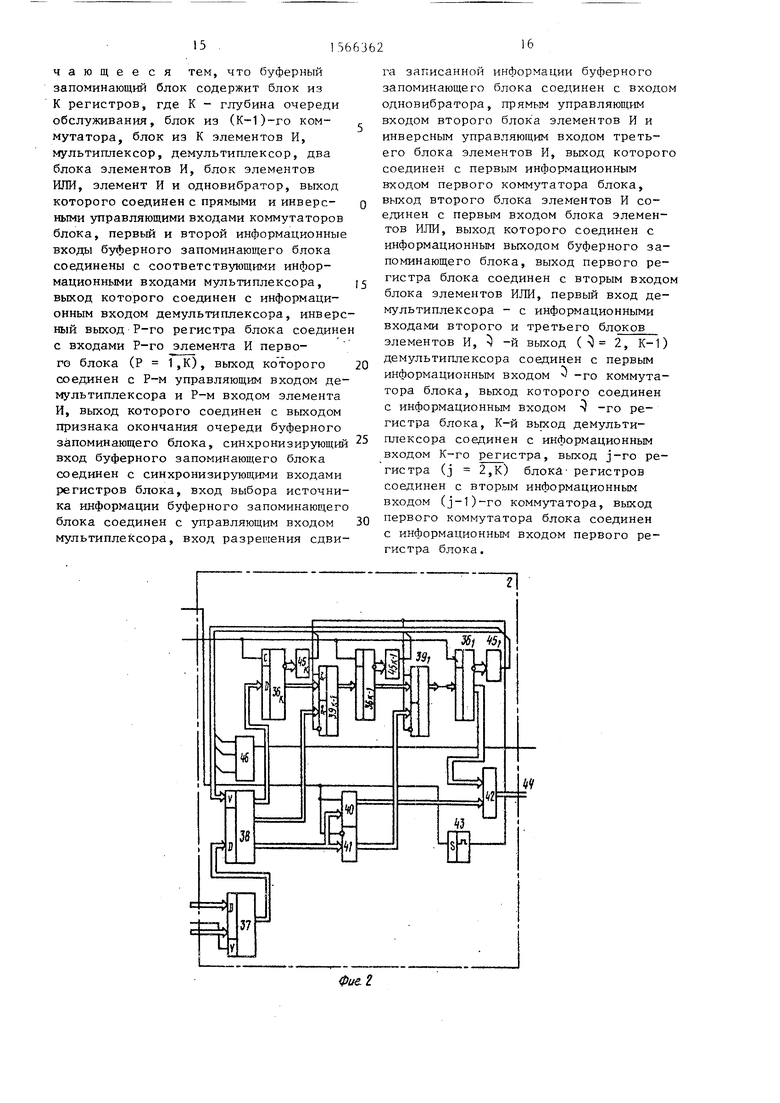

Формат микрокоманды обработки информации (фиг.5а) содержит код проверяемого логического условия X, немодифицируемый разряд адреса Ан, код немодифицируемых разрядов адреса А н , код операционной части (04), признак четности информации 1TL, признак конца микропрограммы Мц,

Отличие формата микрокоманды обмена (фиг.56) заключается в том, что операционная часть микрокоманды разбивается на три подполя - номера канала-получателя информации Ас, номера микропрограммы MMk) номера канала - источника информации Мп,

Блок 4 ассоциативной памяти (фиг.7 представляет программируемую логическую матрицу и содержит две под- атрицы, содержащие два блока резисоров, два блока элементов НЕ 55.1-55.f, 25 и 56.1-56.п.

Устройство работает следующим образом.

Работа устройства возможна в четы- ех режимах: режиме обработки собственных микрокоманд; режиме выдачи икрокоманд обмена; режиме приема и обработки микрокоманд обмена; режие модификации микрокоманды обмена.

Так как в многоканальном устройстве каналы идентичны и могут рабо20

15

30

35

тать независимо, то работу устройства рассмотрим на примере работы отдельного канала.

В исходном состоянии элементы памяти канала находятся в нулевом состоянии (за исключением разряда регистра 6, определяющего признак микропрограммы - поле 6.6). Перед началом работы элементы памяти устанавливаются а нулевое состояние (цепи обнуления на фиг.1 не показаны

В блоке 3 записан код, определяющий местоположение канала в устройстве, построенном в виде кольцевой структуры на основе однотипных каналов. Этот код является идентификатором канала.

Работа канала в режиме обработки собственных микрокоманд.

Работа канала в этом режиме функционирования начинается путем подачи на вход 26 кода операции, определяющего адрес первой микрокоманды микро0

5

0

программы управления. Одновременно с подачей кода операции на вход 25 канала (фиг.1) подается импульс начат ла работы. Этот сигнал через элемент ИЛИ 21 устанавливает триггер 51 блока 7 (фиг.4) в единичное состояние и разрешает тем самым формирование импульсов для синхронизации работы канала.

Так как на выходе схемы сравнения 11 (фиг.1) имеется сигнал логического нуля, то этот сигнал разрешает прохождение кода операции с входа 26

5 через мультиплексор 37 на информационный вход демультиплексора 38 блока 2 (фиг.2),, С выхода регистра 6 на управляющий вход блока 2 поступаг- ет метка-признак конца микропрограммы. Эта метка поступает на управляющий вход первого 40 и второго 41 блоков элементов И и определяет процедуру записи информации в регистр 36.1 или передачу транзитом через блок элементов ИЛИ 42.

Так как блок регистров 36.1-36.К (фиг.2) находится в нулевом состоянии, то на выходах элементов И 45.1-45.К находятся сигналы логической единицы, поступающие на управляющий вход демультиплексора 38 и определяющие распределение поступающих на обслуживание кодов номеров микропрограмм по регистрам по мере заполнения очереди блока 2,

Поступившая информация через де- мультиплексор 38, блок элементов И 40 и блок элементов ИЛИ 42 транзитом через блок 2 (фиг.2) поступает

Q через коммутатор 9 адреса на информационный вход регистра 5 и но первому тактовому импульсу с выхода блока 7 (фиг.1) поступившая информация заносится в регистр 5. Происходит

5 обращение к блоку памяти 1.

По заднему фронту второго тактового импульса считанная микрокоманда, формат которой представлен на фиг.5,а, заносится в регистр 6 (фиг.1).

0 Операционная часть (04) микрокоманды с выхода поля 6.4 регистра 6 через блок элементов И 18 поступает на выход 31 канала для управления соответствующим операционным блоком, наприг мер арифметико-логическим устройством (АЛУ).

Поля 6.1-6.3 регистра 6 формируют адрес очередной микрокоманды с использованием мультиплексора 13. Мульти0

5

плексор 13 предназначен для формирования значения модифицируемого разряда адреса очередной микрокоманды в соответствии со значением сигналов на его информационных входах (поле 6„2 регистра 6 и логические условия с входа 30 устройства) и управляющем входе (поле 6„1 регистра 6).

В процессе выполнения микропрограм мы с входа 26 в блок 2 по тактовым, импульсам с выхода блока 7 могут заноситься коды номеров очередных микропрограмм (коды операций).

По мере выдачи управляющей информа ции каналам происходит ее контроль блоком 8 (фиг 3). При этом происходит контроль как адресный, так и операционной частей микрокоманды методом проверки на четность. При искажении одного из кодов или несоответствии адреса выбранной микрокоманде блок 8 формирует сигнал отказа канала путем установления в единичное состояние триггера 50 (фиг. 3).

Признак отказа канала с выхода блока 8 через элемент ИЛИ 22 поступает на управляющий вход блока 7 (фиг.4) и устанавливает в нулевое состояние триггер 51 и счетчик 53. Генератор 52 прекращает формирование импульсов для синхронизации работы канала и канал завершает работу.

Признак отказа канала поступает, кроме того, на выход 32 канала для передачи информации для последующей реконфигурации выходов предыдущего и входов последующего каналов- (фиг.6) Это необходимо для исключения отказавшего канала и передачи микроко- манд обмена, минуя отказавший канал.

Реконфигурация структуры достигается тем, что сигнал с выхода 32 1-го канала поступает на вход 35 (i-l)-ro канала. Поступающие для транзитной передачи микрокоманды обмена демультиплексором 16 направляются не на 1-й канал, а на (1+1)-й. Управляющий сигнал отказа 1-го канала поступает с входа 29 (i+1)-ro ка- нала (фиг. 1) на управляющий вход мультиплексора 14. Приходящая транзитом информация принимается с (i-1)- го канала, а не. с отказавшего 1-го канала.

Работа канала в режиме выдачи мик рокоманд обмена.

В процессе обработки микрокоманд канал устройства может выдавать мик,-

.

мQ

- 20 25

JQ), 40

д5 ,-п

55

рокоманды обмена другим каналам устройства, образующего кольцевую структуру. Формат микрокоманды обмена представлен на фиг.5,б. В этом случае операционная часть микрокоманды - поле 6.4 регистра 6 образует микрокоманду обмена

м л Ј М 4 М ио с r L1 мс т 11п

где Ас - код (номер) канала приемника информации; Ммк- код (номер) микропрограммы, которую должен выполнить Ас-й канал устройства; М п - код (номер) канала передатчика информации; Ф - знак конкатенации (сцепления) отдельных слогов микрокоманды обмена.

Одновременно с кодом микрокоманды обмена М0 с выхода поля 6.7 регистра 6 выдается метка-признак передачи управления. Эта метка поступает на управляющий вход коммутатора 10 и разрешает прохождение микрокоманды обмена на информационный вход демульт типлексора 16. В зависимости от состояния следующего (1+1)-го канала (в работоспособном он состоянии или состоянии отказа) информация выдается (i-H)-My или (1+2)-му каналам. Одновременно с выдачей информации (микрокоманды обмена) выдается тактовый импульс для записи информации в последующем канале устройства.

Метка-признак передачи управления с выхода 6.7 регистра 6 поступает на инверсный управляющий вход блока элементов И 18 и запрещает тем самым выдачу управляющей информации с поля 6.4 регистра 6 на выход 31 канала.

Далее канал может либо формировать для выдачи микрокоманду обмена в следующей микрокоманде, либо продолжить обработку микропрограммы аналогично рассмотренному ранее.

Работа канала в режиме приема и обработки микрокоманд обмена.

Микрокоманда обмена в зависимости от состояния предыдущего канала поступает либо с входа 27 канала, либо с входа 28 на один из информационных входов мультиплексора 14 (фиг. 1).

Одновременно с поступлением микрокоманды обмена поступает тактовый импульс. Этот импульс позволяет занести поступившую информацию (микрокоманду обмена) в регистр 17, устанавливает через элемент ИЛИ 21 триггер 51 (фиг, 4) блока 7 в единичное состояние, что разрешает формирование тактовьгх импульсов для синхронизации работы канала. Кроме того, по поступившему тактовому импульсу происходит обращение к блоку памяти 3, в котором хранится единственный код, идентифицирующий местоположение (номер) канала в структуре устройства

Считанный из блока памяти 3 идентификатор заносится в регистр 19.

Занесенный в регистр 17 код микрокоманды обмена состоит из трех частей: кода номера канала приемника информации (Ас), кода номера микропрограммы (Ммк), которую должен вы

полнить соответствующий канал устройства и код номера канала источника информации (Мп).

Код номера канала приемника информации с поля регистра 17 поступает на вход схемы 11 сравнения, где происходит сравнение с кодом (идентификатором) данного канала. Так как код номера канала источника информации на схеме 12 сравнения не совпал с идентификатором канала, то информация с выхода демультиплексора 15, дополняясь кодом номера канала источника информации через блок элементов ИЛИ 23 и коммутатор 10 в зависимости от состояния последующего (i+1)--ro канала выдается на один из выходов демультиплексора 16 и один из выходо 33 или 34 канала с последующим каналом устройства.

При совпадении кода номера канала приемника информации с идентификатором данного канала на выходе схемы 11 сравнения формируется сигнал логической единицы. Этот сигнал поступает на управляющий вход мультиплексора 37 (фиг. 2) блока 2 и разрешает тем самым прохождение кода номера микропрограмм (Ммк) с выхода поля регистра 17 (фиг. 1) на информационный вход демультиплексора 38 (фиг. 2) для записи в соответствующий регистр блока регистров 36.1-36.К и последующей его обработки в порядке поступления запросов аналогично тому, как это рассмотрено.

При выдаче последней микрокоманды в поле 6.6 регистра 6 заносится метка-признак конца микропрограммы. Эта метка с выхода регистра 6 поступает на управляющий вход блока 2 (фиг.2) и формирует единичный импульс на выходе одновибратора A3, который, поступая на управляющие входы ком

15

20

25

30

35

.с

40

0

5

мутаторов 1Q.1-39,К-1, разрешает тем самым перезапись информации в блоке 36.1-36 К регистров. При поступлении тактового импульса с выхода блока 7 на синхронизирующие входы регистров 36.1-36.К происходит сдвиг (перезапись) информации. Одновибра- тор 43 устанавливается в исходное (нулевое) состояние и тем самым блок 2 готов к приему поступающих на обслуживание микропрограмм.

Работа канала в режиме модификации микрокоманды обмена.

При работе устройства возможна ситуация, при которой при передаче информации (микрокоманды обмена) j-му каналу возможен его отказ. В этом случае микрокоманда обмена, минуя отказавший канал, по кольцевой структуре устройства возвращается в канал источник информации и заносится в регистр 17.

Схема 12 сравнения производит сравнение идентификатора канала и кода источника информации, при их совпадении формирует сигнал логической единицы. Этот сигнал с выхода схемы 12 сравнения поступает на управляющий вход демультиплексора 15. Информация о коде номера приемника информации и код микропрограмм с выходов полей регистра 17 через де- мультиплексор 15 поступают на вход блока 4.

Блок 4 выполнен в виде программируемой логической матрицы (фиг. 7) и выполняет роль преобразователя кодов, модифицируя код номера канала приемника, в котором произошел отказ. Этим достигается передача управления (микрокоманды обмена) на канал, в блоке памяти которого хранятся копии микропрограмм отказавшего канала. Промодифицированный код номера канала приемника совместно с кодом номера микропрограммы и дополненный кодом номера канала источника информации с выхода поля регистра 17 через блок элементов ИЛИ 23, коммутатор 10 поступает на информационный вход демультиплексора 16 и в зависимости от состояния (i+1)-ro канала выдается или на выход 33, или на выход 34 канала.

Далее устройство функционирует в рассмотренных режимах.

Окончание работы канала заключается в следующем.

Во-первых, при отказе канала сигнал с выхода блока 8 через элемент ИЛИ 22 поступает на вход установки в ноль триггера 51 (фиг. 5), устанавливает его в нулевое состояние, и канал завершает работу.

Во-вторых, после того, как очередь блока 2 пуста (нет кодов номеров микропрограмм на обслуживание), на выходе элемента И 46 (фиг. 2) сигнал логической единицы. Этот сигнал с выхода блока 2 поступает на вход элемента И 20, и при выдаче с поля 6.6 регистра 6 метки-признака конца мик- ропрограммы, одновибратор 24.2 формирует импульс и сигнал логической единицы с выхода элемента И 20 через элемент ИЛИ 22 устанавливает триггер 51 (фиг. 4) блока 7 в нулевое состояние; канал завершает работу и готов к приему очередной информации.

Формула изобретения

1. Многоканальное устройство для обмена управляющей информацией в вычислительной системе, содержащее N каналов, а в каждом канале - блок памяти микропрограмм, блок синхронизации, буферный запоминающий блок, блок контроля, коммутатор адреса, регистр адреса, входной регистр, регистр микрокоманд, мультиплексор логических условий, блок памяти номера канала, регистр номера канала, первую схему сравнения, блок элементов И5 элемент И, два элемента ИЛИ, причем первый информационный выход i-го (i 1, N-1) канала соединен с первым информационным входом (1-Й)-го канала устройства, выход -коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с информационным входом блока памяти микропрограмм и первым входом блока контроля, выход контрольного признака четности регистра адреса соединен с вторым входом блока контроля, выход блока памяти микропрограмм соединен с информационным входом регистра микрокоманд, выход поля кода логических условий которого соединен с уп- равляющим входом мультиплексора логических условий, выход модифицирующего разряда адреса регистра микрокоманд соединен с первым информационным входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра микрокоманд соединен с немодифицируемыми разрядами адреса первого информационного входа коммутатора адреса, выход операционного поля регистра микрокоманд соединен с информационным входом блока элементов И, выход которого соединен с выходом оперативной части микрокоманд канала, выход мультиплексора логических условий соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выходы полей кода логических условий, выход модифицируемого и немодифицируемых разрядов адреса, выходы операционного поля регистра микрокоманд соединены с третьим входом блока контроля, выход контрольного признака четности регистра микрокоманд соединен с четвертым входом блока контроля , выход которого соединен с выходом признака отказа канала, первый управляющий вход начала работы канала соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом запуска блока синхронизации, первый выход которого соединен с синхронизирующим входом буферного запоминающего блока, выход блока памяти номера канала соединен с информационным входом регистра номера канала, выход которого соединен с первым входом регистра номера канала, выход которого соединен с первым входом первой схемы сравнения, выход первой схемы сравнения соединен с входом выбора источника информации буферного запоминающего блока, выход первого поля входного регистра соединен с вторым входом первой схемы сравнения, второй выход блока синхронизации соединен с синхронизирующим входом регистра адреса, третий выход блока синхронизации соединен с синхронизирующим входом регистра микрокоманд, вход логических условий канала соединен с вторым информационным входом мультиплексора логических условий, четвертый выход блока синхронизации соединен с входом фиксации результатов контроля блока контроля, вход кода операции канала соединен с первым информационным входом буферного запоминающего блока, выход признака кон- ид микропрограммы регистра микрокоманд соединен с прямым и инверсным управляющими входами коммутатора адреса, выход элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом останова блока синхронизации, выход блока контроля соединен с вторым входом второго элемента ИЛИ, информационный выход буферного запоминающего блока соединен с вторым информационным входом коммутатора адреса, выход признака окончания очереди буферного запоминающего блока соединен с первым входом элемента И, выход второго поля входного регистра соединен с вторым информационным входом буферного запоминающего блока, о т- личающееся тем, что, с целью повышения надежности функционирования, каждый канал дополнительно содержит блок ассоциативной памяти мультиплексор, два демультиплексора, выходной коммутатор, вторую схему сравнения, блок элементов ИЛИ, два одновибратора, причем первый информационный выход N-ro канала соединен с первым информационным входом первого канала, второй информационный

0

первого элемента ИЛИ, управляющим входом блока памяти номера канала, синхронизирующим входом входного регистра и через первый одновибратор - с синхровходом регистра номера канала, выход регистра номера канала соединен с первым входом второй схемы сравнения, второй вход которой соединен с выходом третьего поля входного регистра, выход второй схемы сравнения соединен с управляющим входом первого демультиплексора, первый выход которого соединен с пер5 вым входом блока элементов ИЛИ, второй выход первого демультиплексора соединен с входом блока ассоциативной памяти, выход которого соединен с вторым входом блока элементов ИЛИ,

0 выход блока элементов ИЛИ соединен с первым информационным входом выходного коммутатора, выходы первого и второго полей входного регистра соединены с информационным входом первого демультиплексора, выход третьего поля входного регистра соединен с первым и вторым входами блока элементов ИЛИ, выход операционного поля регистра микрокоманд соединен с вто5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении отказоустойчивых вычислительных систем. Целью изобретения является повышение надежности функционирования. Устройство содержит блок 1 памяти микрокоманд, буферный запоминающий блок 2, блок 3 памяти номера канала, блок 4 ассоциативной памяти, регистр 5 адреса, регистр 6 микрокоманд, блок 7 синхронизации, блок 8 контроля, коммутатор 9 адреса, выходной коммутатор 10, схемы 11, 12 сравнения, мультиплексор 13 логических условий, мультиплексор 14, демультиплексоры 15, 16, входной регистр 17, блок 18 элементов И, регистр 19 номера канала, элемент И 20, элементы ИЛИ 21, 22, блок 23 элементов ИЛИ, одновибраторы 24.1, 24.2, вход 25 начала работы, вход 26 кода операции, информационные входы 27, 28, вход 29 признака отказа предыдущего канала, вход 30 логических условий, выход 31 операционной части микрокоманд, выход 32 признака отказа, информационные выходы 33, 34, вход 35 признака отказа последующего канала устройства. Цель достигается за счет обеспечения реконфигурации при отказах. 1 з.п.ф-лы, 9 ил.

35

40

выход i-го (i 1, N-2) канала соеди- 30 информационным входом выходного нен с вторым информационным входом (i+2)-ro канала, второй информационный выход (N-1)-го канала соединен с вторым информационным входом первого канала, второй информационный выход N-ro канала соединен с вторым информационным входом второго канала, выход признака отказа i-го (,N-1) канала соединен с входом признака отказа предыдущего канала (i+1)-ro канала и входом признака отказа последующего канала (i-1)-го канала, выход признака отказа первого канала соединен с входом признака отказа предыдущего канала второго канала и входом признака отказа последующего канала N-ro канала, выход признака отказа N-ro канала соединен с входом признака отказа предыдущего канала первого канала и входом признака отказа последующего канала (N-1)-ro канала, первый и второй информацион- ные входы (i-го (i 1, N) канала соединены соответственно с первым и вторым входами мультиплексора, выход которого соединен с информационным входом входного регистра, разряд признака тактирования выхода мультиплексора соединен с вторым входом

коммутатора, выход признака конца микропрограммы регистра микрокоманд соединен с входом разрешения сдвига .записанной информации буферного запоминающего блока и через второй одновибратор - с первым входом элемента И, выход признака подачи управления регистра микрокоманд соединен с инверсным управляющим входом блока элементов И и с прямым и первым инверсным управляющим входами выходного коммутатора, выход которого соеди нен с информационным входом демульти плексора, выход первой схемы сравне- 45 ния соединен с вторым инверсным управляющим входом выходного коммутато ра, вход признака отказа предыдущего канала соединен с управляющим входом мультиплексора, вход признака отказа последующего канала соединен с управ ляющим входом второго демультиплексора, первый и второй выходы которого соединены соответственно с первым и вторым информационными выходами канала, четвертый выход блока синхронизации - с тактовым разрядом информационного входа второго демультиплексора.

55

информационным входом выходного

коммутатора, выход признака конца микропрограммы регистра микрокоманд соединен с входом разрешения сдвига .записанной информации буферного запоминающего блока и через второй одновибратор - с первым входом элемента И, выход признака подачи управления регистра микрокоманд соединен с инверсным управляющим входом блока элементов И и с прямым и первым инверсным управляющим входами выходного коммутатора, выход которого соединен с информационным входом демультиплексора, выход первой схемы сравне- ния соединен с вторым инверсным управляющим входом выходного коммутатора, вход признака отказа предыдущего канала соединен с управляющим входом мультиплексора, вход признака отказа последующего канала соединен с управляющим входом второго демультиплексора, первый и второй выходы которого соединены соответственно с первым и вторым информационными выходами канала, четвертый выход блока синхронизации - с тактовым разрядом информационного входа второго демультиплексора.

чающее ся тем, что буферный запоминающий блок содержит блок из К регистров, где К - глубина очереди обслуживания, блок из (К-1)-го ком- мутатора, блок из К элементов И, мультиплексор, демультиплексор, два блока элементов И, блок элементов ИЛИ, элемент И и одновибратор, выход которого соединен с прямыми и инверс- ными управляющими входами коммутаторов блока, первый и второй информационные входы буферного запоминающего блока соединены с соответствующими информационными входами мультиплексора, выход которого соединен с информационным входом демультиплексора, инверсный выход Р-го регистра блока соединен с входами Р-го элемента И первого блока (Р 1,К), выход которого соединен с Р-м управляющим входом демультиплексора и Р-м входом элемента И, выход которого соединен с выходом признака окончания очереди буферного запоминающего блока, синхронизирующий вход буферного запоминающего блока соединен с синхронизирующими входами регистров блока, вход выбора источника информации буферного запоминающего блока соединен с управляющим входом мультиплексора, вход разрешения сдвига записанной информации буферного запоминающего блока соединен с входом одновибратора, прямым управляющим входом второго блока элементов И и инверсным управляющим входом третьего блока элементов И, выход которого соединен с первым информационным входом первого коммутатора блока, выход второго блока элементов И соединен с первым входом блока элементов ИЛИ, выход которого соединен с информационным выходом буферного запоминающего блока, выход первого регистра блока соединен с вторым входо блока элементов ИЛИ, первый вход демультиплексора - с информационными входами второго и третьего блоков элементов И, } -и выход (, К-1) демультиплексора соединен с первым информационным входом 0 -Го коммутатора блока, выход которого соединен с информационным входом -го регистра блока, К-й выход демультиплексора соединен с информационным входом К-го регистра, выход j-го регистра (j 2,К) блока регистров соединен с вторым информационным входом (j-1)-ro коммутатора, выход первого коммутатора блока соединен с информационным входом первого регистра блока.

Фиг. 5

/LS-sSs /////////// /7 /////// //////

Фиг. 6

фиё.7

czzЈ -основной обмен VZZZfy - обмен при отказах

гл

X

п п п ПDПП0.

ЛНАП

П П П

J0DЛ0

у

i Ј-л

I

i

Фиг. 8

П П П П

J0DЛ0П

у

i Ј-л

х

X

| Электромагнитоакустический преобразователь | 1983 |

|

SU1193575A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Авторское свидетельсьво СССР № 1225452, кл | |||

| С, Ob F 13/00, 198b. | |||

Авторы

Даты

1990-05-23—Публикация

1988-07-21—Подача