Изобретение относится к интегральной микросхемотехнике и может быть использовано при разработке операционных усилителей, компаратора и других устройств аналоговой техники, в интегральном полупроводнике исполнении.

Известны источники-отражатели тока на биполярных транзисторах, которые используются в интегральных микросхемах. В источнике-отражателе тока, содержащем два однотипных транзистора Т1 и Т2 и источник опорного тока И, выполненный на резисторе RI и источнике питания +Ek, выходной ток Iji является функцией опорного тока И и коэффициента усиления тока В.биполярных транзисторов в соответствии с выражением

12

kli

1+(k + 1)B 1 ft)

где k-коэффициент масштабирования тока, который определяется соотношением площадей эмиттерных переходов Ti и Т2 или количеством выходных транзисторов, включенных параллельно Т2. Из этого выражения видно, что недостатком такой схемы является резкое снижение величины выходного тока 2 с уменьшением коэффициента усиления тока В транзистора и увеличением коэффициента масштабирования k.

Введение резистора R2 в базу транзистора для компенсации спада В не решает проблему, как видно из фиг.5 (кривая С).

В известном источнике-отражателе, содержащем три однотипных транзистора Ti.Ta и Тз и источник опорного тока И, выXJ

ю

СО 01 СЬ X

полненный на резисторе RI и источнике питания Ek, зависимость коэффициента масштабирования k от величины В значительно слабее, чем в ранее известном при k 1, однако при k 1 эта зависимость еще сильнее.

Наиболее близким по технической сущности к изобретению является источник-отражатель тока, содержащий два биполярных транзистора р-п-р-типа проводимости Q801, Q802, два полевых р- канальных транзистора 4 и 5, источник опорного тока IIN и шину источников питания Vs.

Коллектор транзистора Q801, являющийся входом источника-отражателя тока, соединен с затвором полевого транзистора 5; базы биполярных транзисторов Q801 и Q802 объединены и соединены с истоком полевого транзистора и со стоком полевого транзистора 4; эмиттеры транзисторов Q801 и Q802 соединены с шиной источника питания Vs и с этой же шиной соединены затвор и исток полевого транзистора 4; сток .полевого транзистора 5 соединен с отрицательной шиной источника питания, выходом источника-отражателя тока является коллектор транзистора 0802.

В такой схеме источника-отражателя тока выходной ток IOVT определяется по формуле

,OVT.|iQ§9i,{N,

(2)

S3Q801

и не зависит от коэффициента усиления тока биполярных транзисторов.

Вместе с тем при изготовлении интегральных схем основным элементом планар- ной технологии является транзистор типа n-p-п, который по своим усилительным и частотным свойствам значительно лучше p/n/p-транзисторов с боковой инжекцией. Данная известная схема источника-отражателя тока может быть построена на основе n-p-n-транзисторов, однако в этом случае полевые транзисторы 4 и 5 должны быть п-канальные.

Таким образом, схема источника-отражателя тока не может быть реализована на основе так называемой упрощен ной BI-FET- технологии, которая использует только два типа комплементарных транзисторов - биполярный n-p-n-типа и полевой р-каналь- ный(РЕТ). .

.Цель изобретения - реализация источника-отражателя тока на основе упрощенной BI-FET технологии с применением только биполярного n-p-n-транэистора и полевого р-канального транзистора.

Поставленная цель достигается тем, что в источнике-отражателе тока, содержащем источник опорного тока, входной и выходные биполярные транзисторы, полевой

транзистор, нагрузки и две шины источника питания, причем коллектор входного транзистора соединен с затворим полевого транзистора и через источник опорного тока - с первой шиной источника питания, базы

0 входного и выходных транзисторов объединены между собой, эмиттеры этих транзисторов соединены со второй шиной источника питания, и с этой шиной соединен сток полевого транзистора, коллекторы

5 выходных транзисторов через соответствующую нагрузку соединены с первой шиной источника питания, согласно изобретению введены дополнительные источник тока и биполярный транзистор, этот дополнитель0 ный источник тока включен между истоком

полевого транзистора и первой шиной источника питания, база дополнительного биполярного транзистора соединена с истоком полевого транзистора, эмиттер до5 полнительного биполярного транзистора соединен с базами входного и выходных транзисторов и через резистор - со второй шиной источника питания, а коллектор дополнительного биполярного транзистора

0 соединен с первой шиной источника питания, при этом все биполярные транзисторы n-p-n-типа между собой и соединены с эмиттером дополнительного биполярного транзистора n-p-n-типа между первой ши5 ной источника питания и коллектором входного транзистора включен источник опорного тока, а в коллекторах выходных транзисторов включены нагрузки. Затвор полевого транзистора соединен с коллекто0 ром входного транзистора, сток полевого транзистора соединен со второй шиной источника питания, а исток этого транзистора через дополнительный источник тока соединен с первой шиной источника питания; с

5 этой же шиной соединен коллектор вспомогательного биполярного транзистора, база которого соединена с истоком полевого транзистора. Эмиттеры входного и выходных транзисторов соединены со второй ши0 ной источника питания, и с этой же шиной через дополнительный резистор соединен эмиттер дополнительного биполярного транзистора.

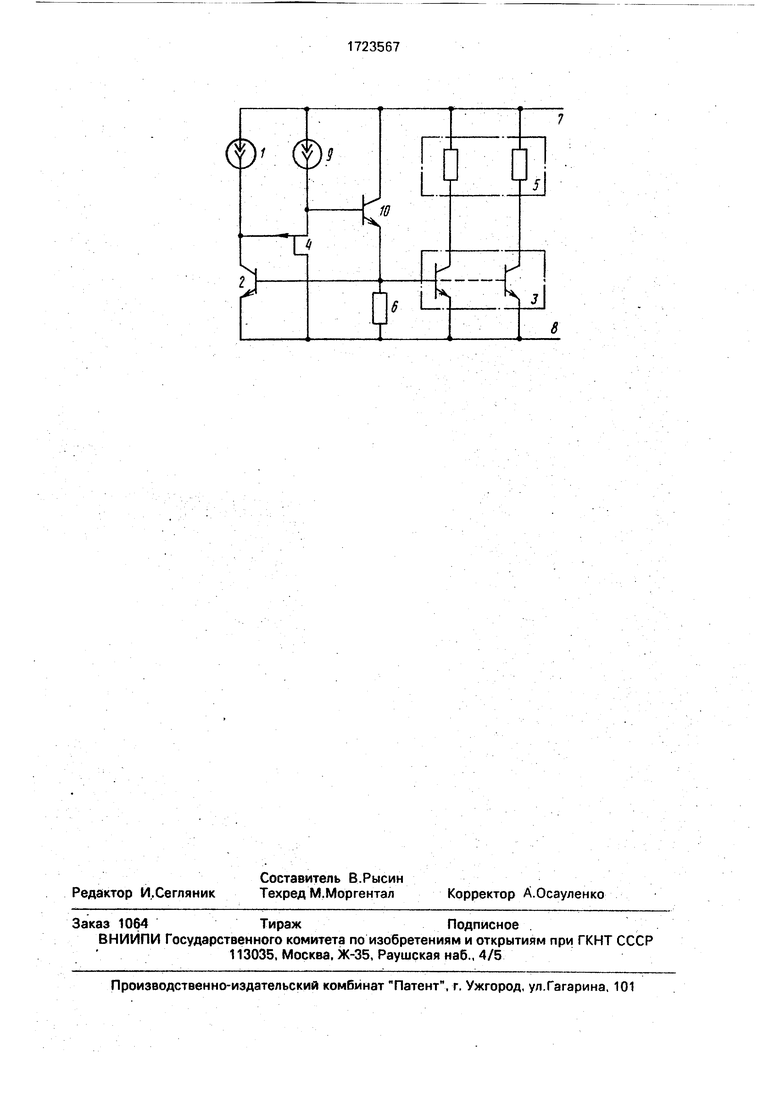

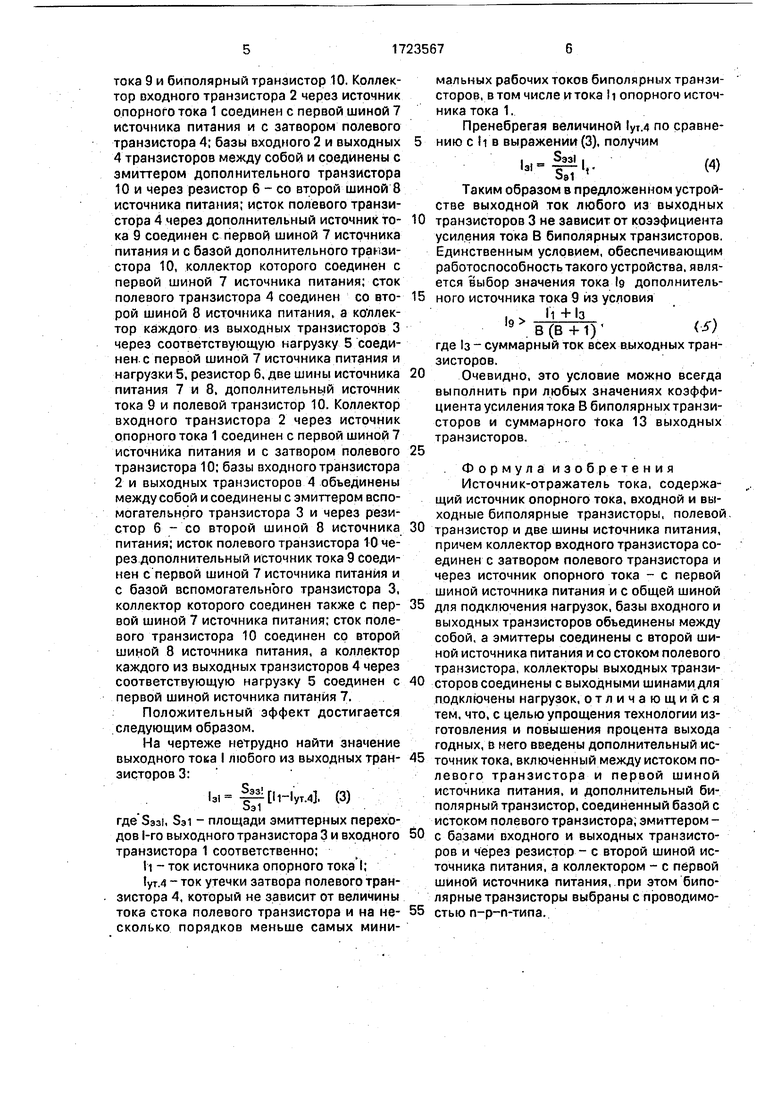

На чертеже представлена схема источ5 ника-отражателя тока.

Устройство содержит источник опорного тока 1, входной 2 и выходные 3 биполярные транзисторы, полевой транзистор 4 нагрузку 5, резистор 6, две шины источника питания 7 и 8, дополнительные источник

тока 9 и биполярный транзистор 10. Коллектор сходного транзистора 2 через источник опорного тока 1 соединен с первой шиной 7 источника питания и с затвором полевого транзистора 4; базы входного 2 и выходных 4 транзисторов между собой и соединены с эмиттером дополнительного транзистора 10 и через резистор 6 - со второй шиной 8 источника питания; исток полевого транзистора 4 через дополнительный источник тока 9 соединен с первой шиной 7 источника питания и с базой дополнительного транзистора 10, коллектор которого соединен с первой шиной 7 источника питания; сток полевого транзистора 4 соединен со второй шиной 8 источника питания, а ко ллек- тор каждого из выходных транзисторов 3 через соответствующую нагрузку 5 соединен, с первой шиной 7 источника питания и нагрузки 5, резистор 6, две шины источника питания 7 и 8, дополнительный источник тока 9 и полевой транзистор 10. Коллектор входного транзистора 2 через источник опорного тока 1 соединен с первой шиной 7 источника питания и с затвором полевого транзистора 10; базы входного транзистора 2 и выходных транзисторов 4 объединены между собой и соединены с эмиттером вспомогательного транзистора 3 и через резистор 6 - со второй шиной 8 источника питания; исток полевого транзистора 10 через дополнительный источник тока 9 соединен с первой шиной 7 источника питания и с базой вспомогательного транзистора 3, коллектор которого соединен также с первой шиной 7 источника питания; сток полевого транзистора 10 соединен со второй шиной 8 источника питания, а коллектор каждого из выходных транзисторов 4 через соответствующую нагрузку 5 соединен с первой шиной источника питания 7.

Положительный эффект достигается следующим образом.

На чертеже нетрудно найти значение выходного тока I любого из выходных транзисторов 3:

Зэз

5э1

.4 (3)

где Зэз1, Зэ1 - площади эмиттерных переходов 1-го выходного транзистора 3 и входного транзистора 1 соответственно;

И - ток источника опорного тока I;

1ут.4 - ток утечки затвора полевого транзистора 4, который не зависит от величины тока стока полевого транзистора и на несколько порядков меньше самых мини0

5

0

5

0

5

0

5

0

5

мальных рабочих токов биполярных транзисторов, в том числе и тока 1 опорного источника тока 1.

Пренебрегая величиной 1уТ.4 по сравнению с It в выражении (3), получим

u,-|si,.«

Таким образом в предложенном устройстве выходной ток любого из выходных транзисторов 3 не зависит от коээфициента усиления тока В биполярных транзисторов. Единственным условием, обеспечивающим работоспособность такого устройства, является выбор значения тока Ig дополнительного источника тока 9 из условия

ii + 1з

(S)

19

В (В +1)

где з - суммарный ток всех выходных транзисторов.

Очевидно, это условие можно всегда выполнить при любых значениях коэффициента усиления тока В биполярныхтранзисторов и суммарного тока 13 выходных транзисторов.

. Ф о р м у л а и з о б р е т е н и я

Источник-отражатель тока, содержащий источник опорного тока, входной и выходные биполярные транзисторы, полевой, транзистор и две шины источника питания, причем коллектор входного транзистора соединен с затвором полевого транзистора и через источник опорного тока - с первой шиной источника питания и с общей шиной для подключения нагрузок, базы входного и выходных транзисторов объединены между собой, а эмиттеры соединены с второй шиной источника питания и со стоком полевого транзистора, коллекторы выходных транзисторов соединены с выходными шинами для подключены нагрузок, отличающийся тем, что, с целью упрощения технологии изготовления и повышения процента выхода годных, в него введены дополнительный источник тока, включенный между истоком полевого транзистора и первой шиной источника питания, и дополнительный биполярный транзистор, соединенный базой с истоком полевого транзистора; эмиттером - с базами входного и выходных транзисторов и через резистор - с второй шиной источника питания, а коллектором - с первой шиной источника питания, при этом биполярные транзисторы выбраны с проводимостью п-р-п-типа.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРСЕНИД-ГАЛЛИЕВЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784666C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2766868C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615071C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

Изобретение относится к электротехнике и может быть использовано в аналоговых и цифровых микросхемах радиоэлектронной аппаратуры для задания статических режимов работы элементов. Цель- упрощение технологии изготовления и повышение процента выхода годных изделий. Источник-отражатель тока содержит биполярные транзисторы 2,3 и 10, полевой транзистор 4, опорные источники 1 и 9 тока, резистор 6. Выполнение транзисторов 2,3 и 10 с проводимостью п-р-п-типа, а транзистора 4 с каналом р-типа и соединения стока транзистора 4 и эмиттеров транзисторов 2 и 3 с шиной 8 питания, эмиттера транзистора 10 с базами транзисторов 2 и 3, а цепи затвор-исток транзистора 4 между коллектором транзистора 10 позволяют обеспечить необходимую стабилизацию токов выходных транзисторов 3 при изменении коэффициента усиления биполярных транзисторов и упростить технологию изготовления, повысив тем самым процент выхода годных изделий. 1 ил. w Ё

| Патент США NJ 4603290, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 4473794 | |||

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-03-30—Публикация

1989-10-16—Подача