Изобретение относится к области аналоговой микроэлектроники и может быть использовано в структуре аналого-цифровых интерфейсов и IP-модулей систем связи и телекоммуникаций, допускающих работу в условиях воздействия проникающей радиации, низких или высоких температур.

Известно значительное количество базовых схем операционных усилителей (ОУ) на основе так называемого «перегнутого» каскода, которые реализуются на биполярных (BJT) и полевых транзисторах (JFet, КМОП, КНИ, КНС и др.), а также при их совместном включении [1-27].

Существуют схемы ОУ с входным каскадом на JFET и выходным «перегнутым» каско дом на p-n-р биполярных транзисторах [1,2], ОУ с входным каскадом на JFET и «перегнутым» каско дом на n-p-п биполярных транзисторах [3], ОУ с входными каскадами на КМОП и «перегнутым» каско дом на p-n-р биполярных транзисторах [4-6], ОУ с входными каскадами на КМОП и «перегнутым» каскодом на n-p-n биполярных транзисторах [7-9], ОУ с входным каскадом на биполярных n-p-n и выходным «перегнутым» каскодом на p-n-р биполярных транзисторах [10-16], ОУ с входным каскадом на p-n-р и выходным «перегнутым» каскодом на n-p-n биполярных транзисторах [17-20], а также серийных ОУ с входными JFET и выходным «перегнутым» каскодом на n-p-n биполярных транзисторах [21-23].

Таким образом, сочетание входного дифференциального каскада и выходного «перегнутого» каскода является основой схемотехники современных ОУ.

Во многих применениях схема ОУ адаптируется под конкретные технологические процессы и внешние воздействующие факторы, например, влияние низких температур и радиации, т.к. только в этом случае обеспечивается реализациях предельных параметров ОУ.

В настоящее время в российской и зарубежной микроэлектронике уделяется повышенное внимание арсенид-галлиевым микросхемам. Данное направление создания электронной компонентной базы относится к числу востребованных в задачах космического приборостроения. Однако особенности арсенид-галлиевых технологических процессов накладывают существенные ограничения на типы реализуемых транзисторов и их характеристики. Так, например, арсенид-галлиевый технологический процесс, освоенный в США [24-27], а также в Минском научно-исследовательском институте радиоматериалов НАН (https://mniirm.by/), ориентирован на изготовление аналоговых схем, содержащих только полевые GaAs транзисторы с управляющим р-n переходом и биполярные GaAs p-n-р транзисторы. Применение других полупроводниковых приборов не допускается. Это накладывает существенные ограничения на схемотехнику аналоговых устройств, ориентированных на данный технологический процесс.

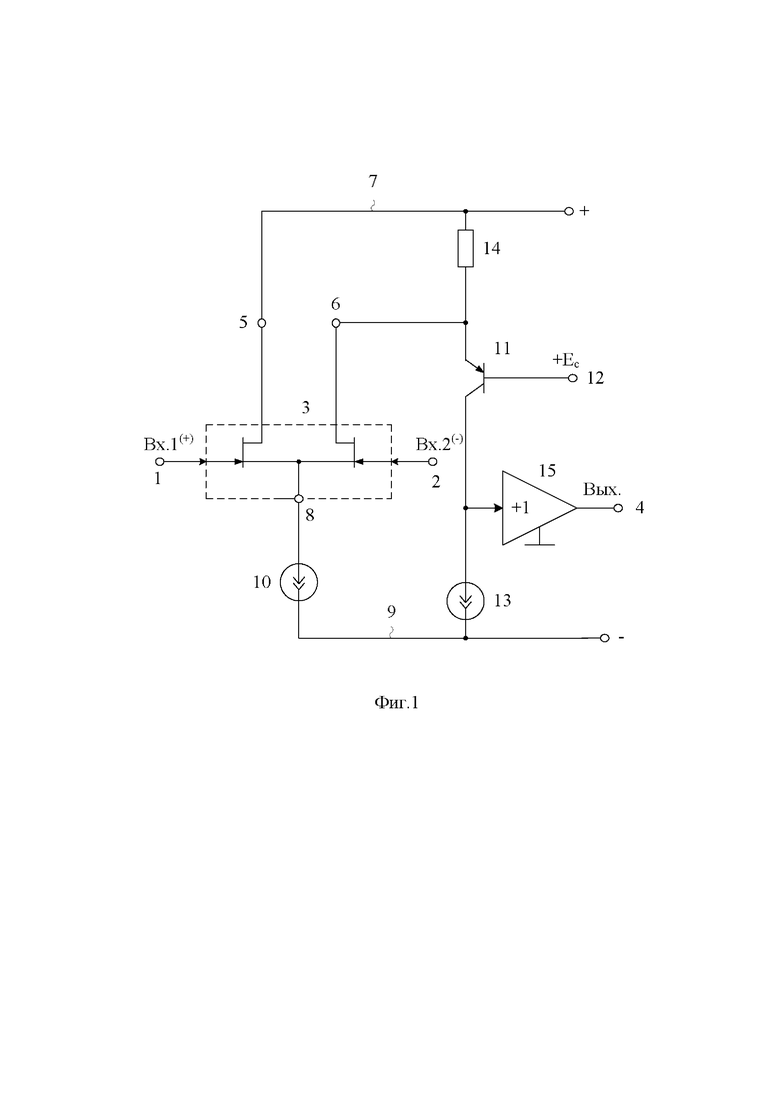

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ, представленный в монографии «Подойников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М.: Энергоатомиздат, 1983. - 216 стр.». Он содержит (фиг. 1) первый 1 и второй 2 входы устройства, связанные со входами входного дифференциального каскада 3 на полевых транзисторах с управляющим р-n переходом, выход устройства 4, первый 5 и второй 6 токовые выходы входного дифференциального каскада 3, причем первый 5 токовый выход связан с первой 7 шиной источника питания, общая истоковая цепь 8 входного дифференциального каскада 4 соединена со второй 9 шиной источника питания через источник опорного тока 10, второй 6 токовый выход входного дифференциального каскада 3 соединен с эмиттером выходного биполярного p-n-р транзистора 11 промежуточного каскада, база которого подключена к источнику напряжения смещения 12, а коллектор через источник опорного тока 13 промежуточного каскада связан со второй 9 шиной источника питания, первый 14 вспомогательный транзистор, выходной буферный усилитель 15, низкоомный выход которого является выходом 3 устройства.

Существенный недостаток ОУ-прототипа состоит в том, что при его реализации на JFET полевых и p-n-р биполярных арсенид-галлиевых транзисторах он имеет повышенные значения систематической составляющей напряжения смещения нуля (Uсм). Это обусловлено отрицательным влиянием на статический режим классических ОУ на «перегнутых» каскодах тока базы используемых биполярных р-n-р транзисторов, который с уменьшением температуры существенно увеличиваются из-за деградации коэффициента усиления по току базы (β).

Основная задача предполагаемого изобретения состоит в создании операционного усилителя с «перегнутым» каскодом, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим р-n переходом и биполярных GaAs p-n-р транзисторах, имеющего малые значения систематической составляющей напряжения смещения нуля.

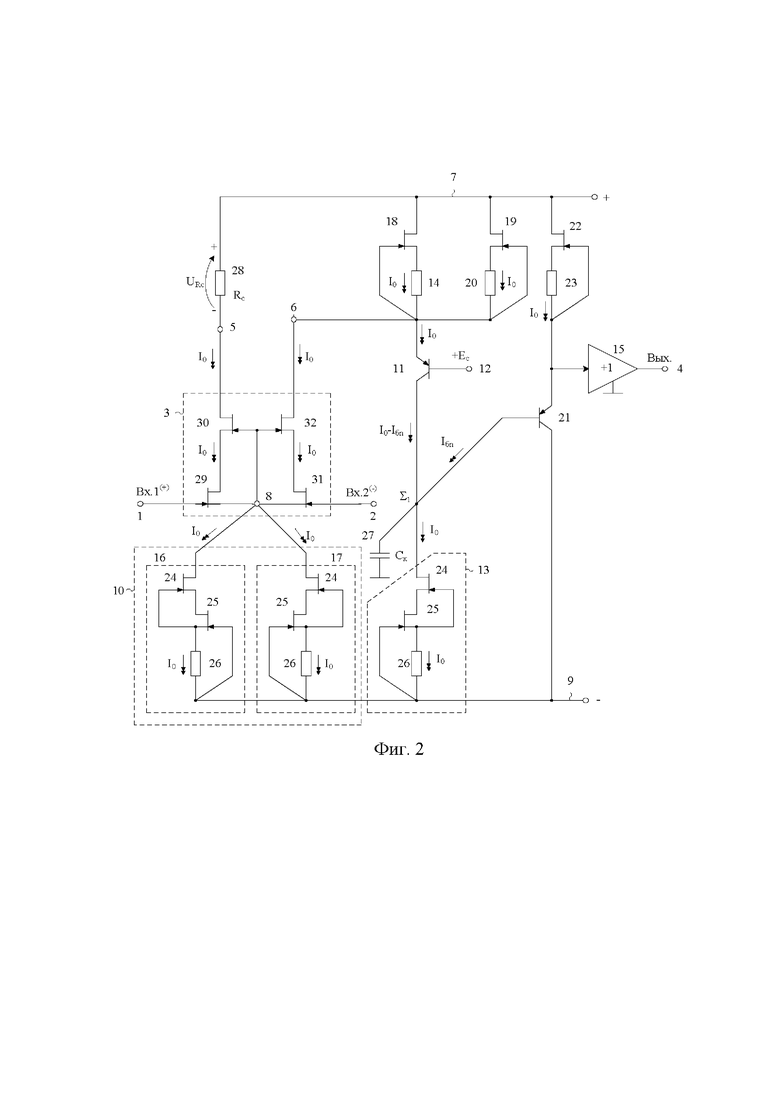

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, связанные со входами входного дифференциального каскада 3 на полевых транзисторах с управляющим р-n переходом, выход устройства 4, первый 5 и второй 6 токовые выходы входного дифференциального каскада 3, причем первый 5 токовый выход связан с первой 7 шиной источника питания, общая истоковая цепь 8 входного дифференциального каскада 4 соединена со второй 9 шиной источника питания через источник опорного тока 10, второй 6 токовый выход входного дифференциального каскада 3 соединен с эмиттером выходного биполярного p-n-р транзистора 11 промежуточного каскада, база которого подключена к источнику напряжения смещения 12, а коллектор через источник опорного тока 13 промежуточного каскада связан со второй 9 шиной источника питания, первый 14 вспомогательный транзистор, выходной буферный усилитель 15, низкоомный выход которого является выходом 3 устройства, предусмотрены новые элементы и связи -источник опорного тока 10 выполнен в виде двух идентичных и параллельно включенных первого 16 и второго 17 вспомогательных источников опорного тока на каскодных составных полевых транзисторах, источник опорного тока 13 промежуточного каскада реализован на каскодных составных транзисторах и идентичен первому 16 и второму 17 вспомогательным источникам опорного тока, эмиттер выходного биполярного р-n-р транзистора 11 промежуточного каскада соединен с затвором первого 18 дополнительного полевого транзистора, исток которого через первый 14 вспомогательный резистор соединен со вторым 6 токовым выходом входного дифференциального каскада 3, второй 6 токовый выход входного дифференциального каскада 3 связан с затвором второго 19 дополнительного полевого транзистора, сток которого подключен к первой 7 шине питания, а исток через второй 20 вспомогательный резистор соединен с эмиттером первого выходного биполярного транзистора 11 промежуточного каскада, коллектор выходного биполярного p-n-р транзистора 11 промежуточного каскада связан с базой дополнительного биполярного транзистора 21, коллектор которого соединен со второй 9 шиной источника питания, а эмиттер соединен со входом выходного буферного усилителя 15 и затвором третьего 22 дополнительного полевого транзистора, сток которого подключен ко второй 7 шине источника питания, а исток соединен с эмиттером дополнительного биполярного транзистора 21 через дополнительный резистор 23.

На чертеже фиг. 1 показана схема ОУ-прототипа.

На чертеже фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

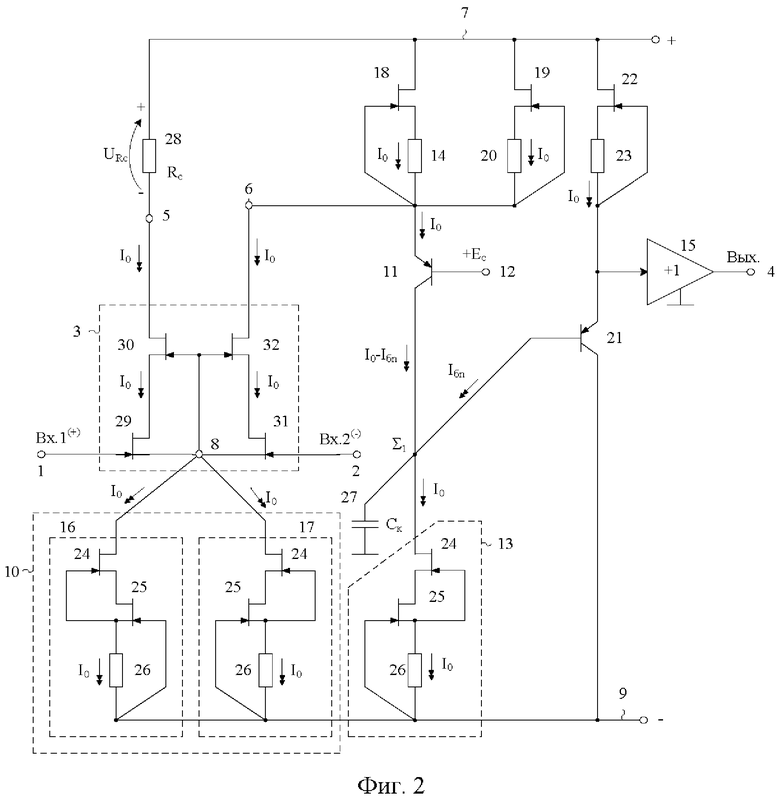

На чертеже фиг. 3 приведена схема заявляемого ОУ фиг. 2 на арсенид-галлиевых полевых и арсенид-галлиевых биполярных транзисторах в среде LTspice в при t=27°C, +Vcc=-Vee=10 В, R1÷R7=11 кОм, V1=7.362 В, Ск=20 пФ и ширине канала JFET GaAs 1 мкм.

На чертеже фиг. 4 приведена логарифмическая амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ фиг. 3

Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля фиг. 2 содержит первый 1 и второй 2 входы устройства, связанные со входами входного дифференциального каскада 3 на полевых транзисторах с управляющим р-n переходом, выход устройства 4, первый 5 и второй 6 токовые выходы входного дифференциального каскада 3, причем первый 5 токовый выход связан с первой 7 шиной источника питания, общая истоковая цепь 8 входного дифференциального каскада 4 соединена со второй 9 шиной источника питания через источник опорного тока 10, второй 6 токовый выход входного дифференциального каскада 3 соединен с эмиттером выходного биполярного p-n-р транзистора 11 промежуточного каскада, база которого подключена к источнику напряжения смещения 12, а коллектор через источник опорного тока 13 промежуточного каскада связан со второй 9 шиной источника питания, первый 14 вспомогательный транзистор, выходной буферный усилитель 15, низкоомный выход которого является выходом 3 устройства. Источник опорного тока 10 выполнен в виде двух идентичных и параллельно включенных первого 16 и второго 17 вспомогательных источников опорного тока на каскодных составных полевых транзисторах, источник опорного тока 13 промежуточного каскада реализован на каскодных составных полевых транзисторах и идентичен первому 16 и второму 17 вспомогательным источникам опорного тока, эмиттер выходного биполярного p-n-р транзистора 11 промежуточного каскада соединен с затвором первого 18 дополнительного полевого транзистора, исток которого через первый 14 вспомогательный резистор соединен со вторым 6 токовым выходом входного дифференциального каскада 3, второй 6 токовый выход входного дифференциального каскада 3 связан с затвором второго 19 дополнительного полевого транзистора, сток которого подключен к первой 7 шине питания, а исток через второй 20 вспомогательный резистор соединен с эмиттером первого выходного биполярного транзистора 11 промежуточного каскада, коллектор выходного биполярного p-n-р транзистора 11 промежуточного каскада связан с базой дополнительного биполярного транзистора 21, коллектор которого соединен со второй 9 шиной источника питания, а эмиттер соединен со входом выходного буферного усилителя 15 и затвором третьего 22 дополнительного полевого транзистора, сток которого подключен ко второй 7 шине источника питания, а исток соединен с эмиттером дополнительного биполярного транзистора 21 через дополнительный резистор 23.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, первый 16 и второй 17 вспомогательные источники опорного тока на каскодных составных полевых транзисторах, а также источник опорного тока 13 промежуточного каскада выполнены по идентичным схемам, содержащим четвертый 24 и пятый 25 дополнительные полевые транзисторы и согласующий резистор 26, причем сток четвертого 24 дополнительного полевого транзистора соединен с истоком пятого 25 дополнительного полевого транзистора и является выходом первого 16 и второго 17 вспомогательных источников опорного тока, его затвор соединен с истоком пятого 25 дополнительного полевого транзистора и через согласующий резистор 26 подключен ко второй 9 шине источника питания, причем сток пятого 25 дополнительного полевого транзистора соединен с истоком пятого 25 дополнительного полевого транзистора, а затвор пятого 25 дополнительного полевого транзистора связан со второй 9 шиной источника питания.

Устойчивость ОУ фиг. 2 обеспечивается корректирующим конденсатором 27 (Ск), который иногда может отсутствовать. Для симметрирования статических режимов по напряжению затвор-сток транзисторов входного дифференциального каскада 3 может использоваться вспомогательный резистор 28 (Rc). Для повышения коэффициента ослабления входного синфазного сигнала ОУ фиг. 2 входной дифференциальный каскад 3 может выполняться на основе каскодных составных полевых транзисторов 29-30, 31-32.

Компьютерное моделирование схемы фиг. 3 подтверждает, что статические токи всех цепей стабилизации статического режима ОУ идентичны и с высокой точностью равны 698 мкА. Выполнить данное условие в схеме ОУ возможно только на JFET транзисторах.

Рассмотрим работу предлагаемого ОУ фиг. 2.

Основная особенность схемы фиг. 2 состоит в применении идентичных источника опорного тока 13 промежуточного каскада (I13=I0), первого 16 (I16=I0) и второго 17 (I17=I0) вспомогательных источников опорного тока, а также таких же цепей стабилизации статического режима выходного биполярного p-n-р транзистора 11 промежуточного каскада и дополнительного биполярного транзистора 21, которые реализованы на первом 18, втором 19 и третьем 22 дополнительных полевых транзисторах (IR14=IR20=IR21=I0). В результате для высокоимпедансного узла Σ1 можно составить следующее уравнение Кирхгофа для «втекающих» и «вытекающих» токов:

где I0 - численные значения тока всех токостабилизирующих двухполюсников в схеме фиг. 2;

β11, β21 - коэффициенты усиления по току базы выходного биполярного p-n-р транзистора 11 промежуточного каскада и дополнительного биполярного транзистора 21;

I13=I0 - ток источника опорного тока 13 промежуточного каскада.

При этом разностный ток в узле Σ1 (ток статической ошибки) равен

Если в диапазоне внешних воздействий β11=β21 то ΔIΣ=0 и, как следствие, систематическая составляющая напряжения смещения нуля ОУ фиг. 2 Uсм, приведенная к его входу, принимает малые значения:

где SДК - крутизна усиления входного дифференциального каскада 3.

Как показывает компьютерное моделирование (фиг. 3), численные значения Uсм лежат в диапазоне 30-50 мкВ.

Учитывая, что все источники опорного тока, устанавливающие статический режим ОУ фиг. 2, имеют высокое выходное дифференциальное сопротивление, в схеме фиг. 2 обеспечивается повышенный коэффициент усиления по напряжению (80-90 дБ), что достаточно для многих применений.

Компьютерное моделирование (фиг. 3, фиг. 4) показывает, что предлагаемый ОУ, схемотехника которого адаптирована на применение в тяжелых условиях эксплуатации, имеет существенные достоинства в сравнении с известными вариантами построения ОУ при их реализации в рамках рассматриваемого арсенид-галлиевого технологического процесса, обеспечивающего создание только полевых транзисторов с управляющим р-n переходом и биполярных p-n-р транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в структуре аналого-цифровых интерфейсов и IP-модулей систем связи и телекоммуникаций, допускающих работу в условиях воздействия проникающей радиации, низких или высоких температур. Технический результат: создание операционного усилителя с «перегнутым» каскодом, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим р-n переходом и биполярных GaAs р-n-р транзисторах, имеющего малые значения систематической составляющей напряжения смещения нуля. Устройство содержит первый (1) и второй (2) входы, связанные со входами входного дифференциального каскада (3) на полевых транзисторах с управляющим р-n переходом, выход устройства (4), первый (5) и второй (6) токовые выходы входного дифференциального каскада (3), причем первый (5) токовый выход связан с первой (7) шиной источника питания, общая истоковая цепь (8) входного дифференциального каскада (4) соединена со второй (9) шиной источника питания через источник опорного тока (10), второй (6) токовый выход входного дифференциального каскада (3) соединен с эмиттером выходного биполярного p-n-р транзистора (11) промежуточного каскада, база которого подключена к источнику напряжения смещения (12), а коллектор через источник опорного тока (13) промежуточного каскада связан со второй (9) глиной источника питания, первый (14) вспомогательный транзистор, выходной буферный усилитель (15), низкоомный выход которого является выходом (3) устройства. Источник опорного тока (10) выполнен в виде двух идентичных и параллельно включенных вспомогательных источников опорного тока. Источник опорного тока (13) промежуточного каскада реализован на каскодных составных транзисторах и идентичен первому (16) и второму (17) вспомогательным источникам опорного тока. 1 з.п. ф-лы, 4 ил.

1. Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля, содержащий первый (1) и второй (2) входы устройства, связанные со входами входного дифференциального каскада (3) на полевых транзисторах с управляющим р-n переходом, выход устройства (4), первый (5) и второй (6) токовые выходы входного дифференциального каскада (3), причем первый (5) токовый выход связан с первой (7) шиной источника питания, общая истоковая цепь (8) входного дифференциального каскада (4) соединена со второй (9) шиной источника питания через источник опорного тока (10), второй (6) токовый выход входного дифференциального каскада (3) соединен с эмиттером выходного биполярного p-n-р транзистора (11) промежуточного каскада, база которого подключена к источнику напряжения смещения (12), а коллектор через источник опорного тока (13) промежуточного каскада связан со второй (9) шиной источника питания, первый (14) вспомогательный транзистор, выходной буферный усилитель (15), низкоомный выход которого является выходом (3) устройства, отличающийся тем, что источник опорного тока (10) выполнен в виде двух идентичных и параллельно включенных первого (16) и второго (17) вспомогательных источников опорного тока на каскодных составных полевых транзисторах, источник опорного тока (13) промежуточного каскада реализован на каскодных составных транзисторах и идентичен первому (16) и второму (17) вспомогательным источникам опорного тока, эмиттер выходного биполярного p-n-р транзистора (11) промежуточного каскада соединен с затвором первого (18) дополнительного полевого транзистора, исток которого через первый (14) вспомогательный резистор соединен со вторым (6) токовым выходом входного дифференциального каскада (3), второй (6) токовый выход входного дифференциального каскада (3) связан с затвором второго (19) дополнительного полевого транзистора, сток которого подключен к первой (7) шине питания, а исток через второй (20) вспомогательный резистор соединен с эмиттером первого выходного биполярного транзистора (11) промежуточного каскада, коллектор выходного биполярного p-n-р транзистора (11) промежуточного каскада связан с базой дополнительного биполярного транзистора (21), коллектор которого соединен со второй (9) шиной источника питания, а эмиттер соединен со входом выходного буферного усилителя (15) и затвором третьего (22) дополнительного полевого транзистора, сток которого подключен ко второй (7) шине источника питания, а исток соединен с эмиттером дополнительного биполярного транзистора (21) через дополнительный резистор 23.

2. Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля по п. 1, отличающийся тем, что первый (16) и второй (17) вспомогательные источники опорного тока на каскодных составных полевых транзисторах, а также источник опорного тока (13) промежуточного каскада выполнены по идентичным каскодным схемам, содержащим четвертый (24) и пятый (25) дополнительные полевые транзисторы и согласующий резистор (26), причем сток четвертого (24) дополнительного полевого транзистора соединен с истоком пятого (25) дополнительного полевого транзистора и является выходом первого (16) и второго (17) вспомогательных источников опорного тока, его затвор соединен с истоком пятого (25) дополнительного полевого транзистора и через согласующий резистор (26) подключен ко второй (9) шине источника питания, причем сток пятого (25) дополнительного полевого транзистора соединен с истоком пятого (25) дополнительного полевого транзистора, а затвор пятого (25) дополнительного полевого транзистора связан со второй (9) шиной источника питания.

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2640744C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ СТАТИЧЕСКОГО РЕЖИМА | 2019 |

|

RU2710930C1 |

| US 7411451 B2, 12.08.2008 | |||

| US 6144234 A1, 07.11.2000 | |||

| US 5952882 A1, 14.09.1999. | |||

Авторы

Даты

2022-11-29—Публикация

2022-03-18—Подача