Изобретение относится к устройствам управления и может применяться в системах автоматизации управления технологическими линиями и оборудованием.

Известно устройство содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, управляющие и адресные шины, программный и коммутационный блоки, последний состоит из трехвходового дешифратора, двухвходовых элементов И, элементов ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ и управляемой ячейкой памяти с соответствующими связями (патент СССР N 1801223, 1992).

Наиболее близким по технической сущности является устройство, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, адресные и командные шины, программный и коммутационный блоки, причем последний состоит из трехвходового дешифратора, элемента 2-2И-2ИЛИ, двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, двух элементов И, двух управляемых ячеек памяти, элементов ИЛИ и НЕ, причем входы дешифратора соединены через командные шины с программным блоком, а два выхода с входами блока оперативной памяти и выходного блока, а также с двумя входами элемента ИЛИ, другие выходы дешифратора соединены с первыми входами элемента 2-2И-2ИЛИ, вторые входы последнего связаны с выходами входного блока и блока оперативной памяти, а выход через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и через первый элемент И с управляющим входом первой ячейки памяти, информационный вход которой подключен к программному блоку, а выход через вторые элементы И и ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИЛИ связан с управляющим входом второй ячейки памяти, информационный вход последней соединен с выходом элемента НЕ. Недостатком такого устройства является большое количество командных шин.

Целью изобретения является сокращение числа командных шин и процесса программирования.

Поставленная цель достигается тем, что в известное устройство содержащее входной и выходной блоки, блоки оперативной памяти, командные и адресные шины, блок синхронизации вместе с генератором импульсов, связанный третьим выходом с программным блоком, блок коммутации, содержащий дешифратор, элемент 2-2И-2ИЛИ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И, элементы ИЛИ и НЕ, первая и вторая управляемые ячейки памяти, причем дешифратор соединен двумя выходами с входами блока оперативной памяти и выходного блока, а другими двумя выходами с входами элемента 2-2И-2ИЛИ, выход последнего подключен к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, который своим выходом связан непосредственно с первым входом первого элемента И, второй вход которого соединен с первым выходом блока синхронизации, а выход с управляющим входом первой ячейки памяти, выход последней подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого связан с первым входом элемента ИЛИ, второй и третий входы последнего соединены также с двумя выходами дешифратора, а выход - с первым входом второго элемента И, второй вход которого подключен к второму выходу блока синхронизации, а выход - к управляющему входу второй ячейки памяти, информационный вход которой связан с выходом элемента НЕ, а выход соединен с информационными входами выходного блока и блока оперативной памяти, в блок коммутации введен преобразователь кода с определенной взаимосвязью входных и выходных параметров, причем входы преобразователя кода подключены к соответствующим выходам программного блока, а выходы - соответственно к трем входам дешифратора, второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, связанным вместе второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, информационному входу первой ячейки памяти и входу элемента НЕ, к третьему входу второго элемента И.

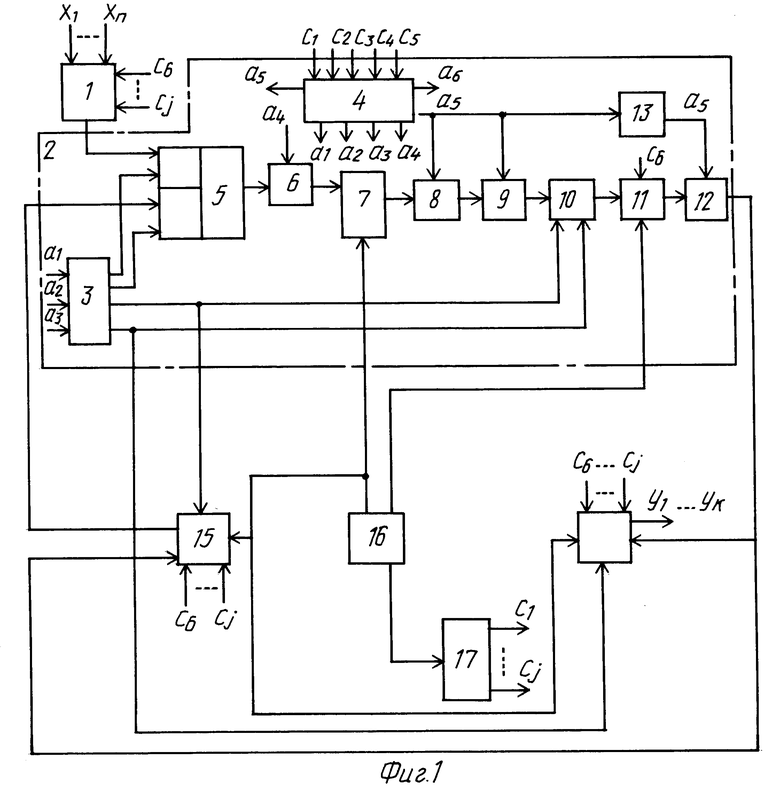

Предлагаемое устройство представлено функциональной схемой на фиг. 1.

Устройство содержит входной блок 1, входы которого подключены к первичным датчикам X1...Xn, а выход связан с блоком коммутации 2, состоящий из дешифратора 3, связанного входами a1, a2 и a3 с выходами преобразователя кода 4, а выходами - с входами элемента 2-2И-2ИЛИ 5, выход последнего соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, выход которого связан с входом первого элемента И 7, выход последнего подключен к управляющему входу первой управляемой ячейки памяти, выход которой соединен с входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, выход последнего, через элемент ИЛИ 10 и второй элемент И 11 связан с управляющим входом второй управляемой ячейки памяти 12, информационной вход которой соединен с выходом элемента НЕ 13, а выход к входам выходного блока 14 и блока оперативной памяти 15, связанных также с первым выходом блока синхронизации 16, другой выход которого подключен к входу программного блока 17.

На фиг. 9 представлена взаимосвязь между входными C1...C5 и выходными параметрами a1...a6 в преобразователь кода 4.

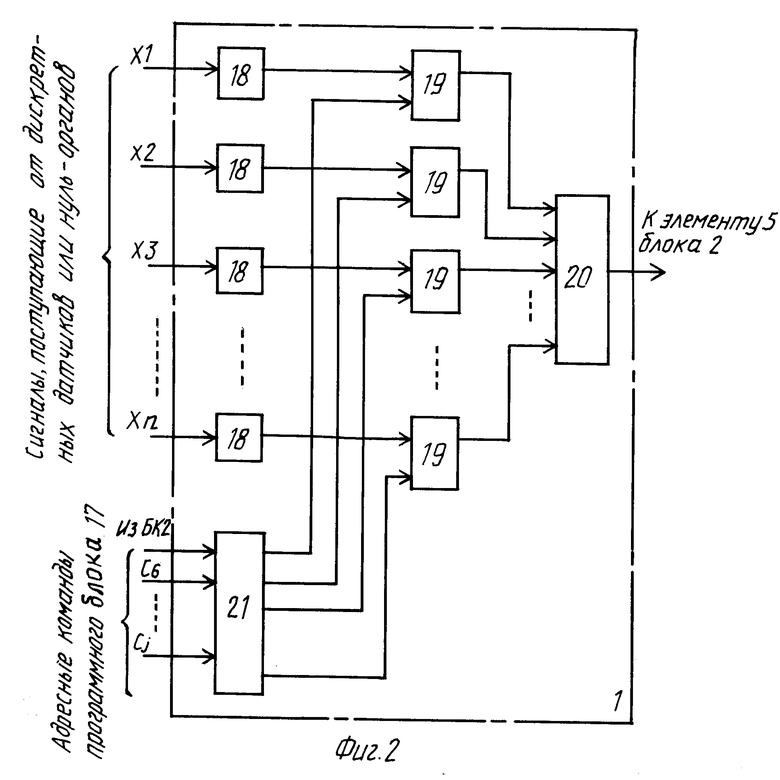

Входной блок известной конструкции 1 представлен на фиг. 2. Он содержит элементы 18, преобразующие входные сигналы X1...Xn в унифицированные логические сигналы "1" и "0", элементы считывания И 19, связанного с ними элемента ИЛИ 20 и дешифратора 21, управляющего работой элементов 19 по адресным командам C6...Cj.

Выходной блок 14 (фиг. 3) состоит из элементов И 22, стандартных ячеек памяти (триггеров) 23, куда заносится информация из блока БК 2 и соответствующих усилителей 24, передающих логические сигналы из ячеек памяти на электропроводные механизмы и световую индикацию, по адресным и управляющим командам из программного блока 17 и БК2, поступающим на дешифратор 25.

В качестве примера на фиг. 4 изображена функциональная схема программного блока 17 известной конструкции.

Программный блок 17 (фиг. 4) состоит из стандартных элементов: счетчика импульсов 26, дешифратора 27, распределяющего импульсы во времени и по направлению, диодной матрицы с горизонтальными и командными шинами, диодов и инверторов (на чертеже не показаны) или как в примере на фиг. 4 стандартных ППЗУ 28, выполненных, например, на микросхемах серии 155РЕЗ, К573РФ1 и т.д., в которых записана программа работы всего устройства.

Блок оперативной памяти 15, который состоит из ячеек памяти, элементов записи и считывания и в качестве которого могут быть использованы стандартные ОЗУ (оперативные запоминающие устройства) или как в примере, приведенном на фиг. 5, блок оперативной памяти содержит элементы 29 обращения к ячейкам памяти, в качестве которых могут быть использованы элементы И, ячейки памяти 30, элементы считывания 31, в качестве которых могут быть использованы элементы И, элемент ИЛИ 32, и первый и второй дешифраторы 33. По командам, поступающим из БК2 и программного блока 17, первый дешифратор 33 через соответствующий элемент 29 заносит в соответствующую ячейку памяти информацию, поступающую из БК2, а второй дешифратор 33 по командам из БК2 и программного блока 17 считывает информацию через элемент считывания 31 из соответствующей ячейки 30, которая через элемент ИЛИ 32 поступает на вход БК2.

В качестве ячеек памяти 2 и 12 (фиг. 1) можно использовать стандартный духтактный D-триггер, например, типа К176ТМ2, при этом на тактовый вход C подается сигнал с выходов элементов И 7 и И 11, а на D-вход подается информационный сигнал a5 или  из программного блока 17. Перед работой триггеры устанавливаются в исходное, например, единичное (нулевое) состояние путем подачи соответствующих сигналов на установочные входы.

из программного блока 17. Перед работой триггеры устанавливаются в исходное, например, единичное (нулевое) состояние путем подачи соответствующих сигналов на установочные входы.

Надо также учесть, что выход элемента И 36 в известном блоке синхронизации 16 (фиг. 6) соединен с элементом И 7 (фиг. 1) и с блоками выходным 14 и оперативной памяти 15 и обеспечивает запись информации в ячейки памяти этих блоков и ячейку памяти 8 (фиг. 1) во второй четверти такта, выход элемента 38 обеспечивает запись информации через элемент И 11 в триггер 12 (фиг. 1) в третьей четверти такта, что следует из приведенных диаграмм работы блока синхронизации 16 на фиг. 7. Это позволяет на одном такте вначале (во второй четверти такта) записывать информацию из триггера 12 в блоки 15 и 14, или через элемент И 7 в ячейку памяти 8, а затем записывать информацию в триггер 12 (в третьей четверти такта). Работа блока синхронизации аналогична его работе в прототипе. Генератор импульсов 41 формирует непрерывную последовательность импульсов, которые поступают на вход счетного триггера 34, с прямого выхода счетного триггера 34 импульсы поступают на вход элемента И 35, который по их совпадению с импульсами генератора импульсов 41 выдает тактовые импульсы, поступающие на вход программного блока 17, который на основе этих тактовых импульсов формирует команды управления. Причем в результате возможного сбоя синхроимпульса относительно тактового импульса элемент И-НЕ 37 сформирует импульс сброса, который обнулит счетный триггер 39, связанный с генератором 41, через элемент НЕ 40 и положение синхроимпульса восстановится фиг. 8.

Стрелками, направленными к элементам и блокам помечены входы этих элементов и блоков.

Выходные клеммы устройства помечены стрелкой с индексом Y1...Yк.

C1...C5 - командные сигналы, управляющие работой блока 2.

C6. . . Cj - адресные сигналы, определяющие номера ячеек памяти в блоках 15, 14 или определенный вход X1...Xn в блоке 1.

Принцип работы предлагаемого устройства покажем на примере вычисления фрагмента булевой функции  содержащего функционально полный набор логических функций, т.е. И, ИЛИ, НЕ. Причем переменная X4 была ранее записана в ячейку памяти блока 15.

содержащего функционально полный набор логических функций, т.е. И, ИЛИ, НЕ. Причем переменная X4 была ранее записана в ячейку памяти блока 15.

Адреса всех ячеек памяти в блоках 1, 15, 14 определяются адресными сигналами C6...Cj.

Перед началом работы триггер 8 устанавливается в единичное состояние, т. е. на его выходе будет присутствовать логическая "1", а триггер 12 в нулевое.

Определим, что при сочетании командных сигналов a1, a2, a3 на входах дешифратора 2 соответственно 100 активизируется первый сверху выход, при 010 активизируется второй выход, при 110 активизируется третий выход, а при 001 активизируется четвертый (нижний) выход дешифратора 3. Будем считать, что запись значений a5 и  происходит в триггеры 8 и 12, когда на их управляющих входах логическая единица переходит в логический нуль.

происходит в триггеры 8 и 12, когда на их управляющих входах логическая единица переходит в логический нуль.

На первом такте из программного блока, через преобразователь кода 4, поступают сигналы a1 = 1, a2 = 0, a3 = 0, a4 = 1, a5 = 0, a6 = 0. При этом значение X1 из блока 1 поступает на верхний вход элемента 5, инвертируется в элементе 6 и поступает через элемент 7 во второй четверти такта на управляющий вход триггера 8 и если X1 = 1, то триггер 8 останется в прежнем состоянии, если X1 = 0, то триггер 8 перейдет в нулевое состояние, т.к. a5 = 0. На следующем (втором) такте во второй его четверти под действием команд a1. ..a6 (100101) переменная X2 из блока 1, определяемая значениями адресных сигналов (как и в случае X1) C6...Cj поступит с инверсией на управляемый вход триггера 8 и, если X2 = 1, триггер 8 не изменит своего единичного состояния, а если X2 = 0, то триггер 8 обязательно окажется в нулевом состоянии. На втором такте в третьей его четверти значение функции X1•X2 под действием сигналов a4 = 0 и a6 = 1 поступит на управляющий вход триггера 12, и если X1 • X2 = 1, то триггер 12 перейдет в единичное состояние, т.к.  В противном случае триггер 12 останется в нулевом состоянии. На третьем такте под действием команд a1...a6 (000110) в триггер 8 запишется "1", если он был в состоянии "0".

В противном случае триггер 12 останется в нулевом состоянии. На третьем такте под действием команд a1...a6 (000110) в триггер 8 запишется "1", если он был в состоянии "0".

На четвертом такте под действием команд a1...a6 (100000) переменная X3 из блока поступает на управляемый вход триггера 8, и если X3 = 0, то триггер 8 останется в состоянии "1", а если X3 = 1, то триггер 8 перейдет в состояние "0". На пятом такте под действием команд a1...a6 (010101) переменная X4 из блока 15 появится на входе триггера 8 во второй четверти такта, и если X4 = 1, то триггер 8 останется в прежнем состоянии, а если X4 = 0, то триггер 8 перейдет в нулевое состояние. В третьей четверти такта под действием команды a6 значение функции  появится на управляемом входе триггера 12, и если оно равно "1", то триггер 12 перейдет (или останется) в состоянии "1", а если

появится на управляемом входе триггера 12, и если оно равно "1", то триггер 12 перейдет (или останется) в состоянии "1", а если  , то триггер 12 не изменит своего состояния. Таким образом, на выходе ячейки памяти 12 будет находиться результат вычисления функции

, то триггер 12 не изменит своего состояния. Таким образом, на выходе ячейки памяти 12 будет находиться результат вычисления функции  На следующем такте этот результат может быть записан в блоки 15 или 14 под действием управляющих сигналов C1...C3 110 или 001 соответственно при C6 = 0.

На следующем такте этот результат может быть записан в блоки 15 или 14 под действием управляющих сигналов C1...C3 110 или 001 соответственно при C6 = 0.

В таблице на фиг. 9 также обозначены логические операции в соответствии с кодами команд C1...C5. При этом X(БH) _→ Tp1 соответствует записи одного из значений X1. ..Xn из блока БН 1 в первую ячейку памяти 8, X(БOП) _→ Tp1 означает запись переменной X из блока БОП 15 в первую ячейку памяти 8, Tp1 _→ Tp2 обозначает запись переменной с выхода первой ячейки памяти 8 во вторую ячейку памяти 12.

Введение преобразователя кода 4 в устройство позволило уменьшить количество линий связи между программным блоком 17 и блоком коммутации 2 с шести до пяти при сохранении функциональных возможностей устройства, что в свою очередь упрощает процесс программирования соответствующими блоками внутри устройства. В этом состоит технико-экономический эффект.

Программируемое устройство для логического управления электроприводами и сигнализацией может применяться в системах автоматизации технологическими линиями и оборудованием. Достигается эта цель тем, что в устройство, содержащее входной и выходной блоки, блок оперативной памяти, командные и адресные шины, блок синхронизации вместе с генератором импульсов, связанный третьим выходом с программным блоком, блок коммутации, содержащий дешифратор, элемент 2-2И-2ИЛИ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента И, элементы ИЛИ и НЕ, первую и вторую управляемые ячейки памяти с соответствующими связями, в блок коммутации дополнительно введен преобразователь кода с определенной взаимосвязью входных и выходных параметров. Введение преобразователя кода позволяет сократить число линий связи между блоком коммутации и блоком программным с шести до пяти, что также ведет к упрощению процесса программирования при сохранении функциональных возможностей устройства, способного программным способом реализовывать все булевы функции. 9 ил.

Программируемое устройство для логического управления электроприводами и сигнализацией, содержащее входной и выходной блоки, блок оперативной памяти, адресные и командные шины, программный блок, блок коммутации и блок синхронизации с генератором импульсов, первый выход которого подключен к первым входам выходного блока и блока оперативной памяти, а второй выход блока синхронизации подключен к входу программного блока, выходы последнего связаны адресными шинами с входным и выходным блоками и блоком оперативной памяти, а командными шинами - с входами блока коммутации, содержащего дешифратор, элемент 2 - 2И - 2ИЛИ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента И и две управляемых ячейки памяти, при этом первый и второй выходы дешифратора связаны с первыми входами элемента 2 - 2И - 2ИЛИ, вторые входы которого подключены к выходам входного блока и блока оперативной памяти, а выход связан с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом блока синхронизации, а выход - с управляющим входом первой управляемой ячейки памяти, выход которой связан с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй и третий входы которого подключены к третьему и четвертому выходам дешифратора, соединенными также с третьими входами соответственно блока оперативной памяти и входного блока, а выход связан с первым входом второго элемента И, второй вход которого связан с третьим выходом блока синхронизации, а выход соединен с управляющим входом второй ячейки памяти, информационный вход последней связан с выходом элемента НЕ, а выход подключен к вторым входам блока оперативной памяти и выходному блоку, второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом элемента НЕ, отличающееся тем, что в блок коммутации введен преобразователь кода с взаимосвязью входных и выходных параметров, входы преобразователя кода подключены к первым пяти выходам программного блока, а выходы соответственно к трем входам дешифратора, второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третьему входу второго элемента И.

| Устройство для дистанционного программного управления сигнализацией и электропроводными механизмами | 1990 |

|

SU1801223A3 |

Авторы

Даты

1998-08-20—Публикация

1996-09-24—Подача