Устройство хранения и считывания информации с коррекцией одиночных ошибок относится к вычислительной технике и может быть использовано для повышения отказоустойчивости запоминающих устройств.

Известно устройство памяти с обнаружением двойных ошибок (Патент РФ на изобретение №2659479 от 01.06.2017 г.), содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1, r2 и r3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2р, r3р, блок выявления ошибки, блок элементов ИЛИ, блок элементов И, элемент И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, вход установки в нулевое состояние, вход записи, вход считывании, адресные входы, вход синхронизации подключены соответственно к первому, второму, третьему и четвертому, пятому входам узла памяти, информационные входы подключены к шестым входам узла памяти и к входам входного кодирующего устройства, выходы которого подключены к седьмым входам узла памяти, информационные выходы узла памяти подключены к входам выходного блока кодирования и к первым входам блока элементов И, выходы выходного блока кодирования подключены к первым входам блока выявления ошибки, вторые входы которого подключены к выходом контрольных разрядов узла памяти, а выходы подключены к входам блока элементов ИЛИ, выход которого подключен к первому входу элемента И, второй вход блока элементов И и второй вход элемента И подключены к входу синхронизации, выходы первого блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала "Ошибка", входной блок кодирования формирует значение контрольного разрядов r1 путем сложения по модулю 2 информационных символов y1,y2,y3, y4, y5, y6, y7, y8, y9, y10, y11, y12, поступающих на его входы, в соответствии с правилом: r1= y3⊕y4⊕y5⊕y6⊕y9⊕y10⊕y11⊕y12, значение контрольного разряда r2 - путем сложения по модулю 2 информационных символов y1, y2, y3, y4, y5, y6, y7, y8, y9, y10, y11, y12, поступающих на его входы, в соответствии с правилом: r2=y3⊕y6⊕y7⊕y8⊕y9⊕y10⊕y11⊕y12, значение контрольного разряда r3 - путем сложения по модулю 2 информационных символов y1, y2, y3, y4, y5, y6, y7, y8, y9, y10, y11, y12, поступающих на его входы, в соответствии с правилом: r3=y1⊕y2⊕y4⊕y5⊕y7⊕y8⊕y10⊕y11, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1p, r2p, r3p путем сложения по модулю 2 информационных символов y1p, y2p, y3p, y4p, y5p, y6p, y7p, y8p, y9p, y10P, y11p, y12p, поступающих на его входы при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1p=y3p⊕y4p⊕y5p⊕y6p⊕y9p⊕y10p⊕y11p⊕y12p; r2p=y3p⊕y6p⊕y7p⊕y8p⊕y9p⊕y10p⊕y11p⊕y12p; r3p=y1p⊕y2p⊕y4p⊕y5p⊕y7p⊕y8p⊕y10p⊕y11p, блок выявления ошибки осуществляет поразрядное сложения по mod2 значений контрольных разрядов r1S, r2S и r3S, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1p, r2p, r3p, сформированных на выходах выходного блока 3 кодирования.

Недостатком устройства является низкая отказоустойчивость, та как ошибки обнаруживаются, но не корректируются.

Наиболее близким по техническому решению является устройство хранения и передачи данных с исправлением одиночных ошибок в байте информации и обнаружением произвольных ошибок в байтах информации (Патент РФ на изобретение №2450331 от 10.05. 2012 г.)), содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, коммутатор, блок коммутаторов, корректор, блок корректоров, отличающаяся тем, что оно дополнительно содержит первый блок элементов ИЛИ, второй блок элементов ИЛИ, инвертор, элемент И, блок элементов И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, двадцати четырех разрядные информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, вход синхронизации подключен к пятому входу узла памяти и к первому входу блока элементов И, информационные входы подключены к шестым входам узла памяти и к входам входного блока кодирования который формирует значения контрольных разрядов r1, r2, r3, r4, r5, r6 путем сложения по модулю 2 информационных символов x1 x2 x3, z1 z2 z3, a1 а2 а3, c1 c2 c3, e1 e2 e3, f1 f2 f3, g1 g2 g3, h1 h2 h3., поступающих на входы входного блока кодирования, в соответствии с правилом: r1=x1⊕z1⊕а1⊕с1⊕е1⊕f1⊕g1⊕h1; r2=x2⊕z2⊕а2⊕с2⊕e2⊕f2⊕g2⊕h2; r3=x3⊕z3⊕a3⊕c3⊕e3⊕f3⊕g3⊕h3; r4=x1⊕z3⊕a2⊕c2⊕c3⊕e1,⊕е3⊕f1⊕f2⊕g1⊕g2⊕g3; r5=x2⊕z1⊕a3⊕c1⊕c3⊕e1⊕e2⊕f2⊕f3⊕g1⊕g2⊕g3; r6=x3⊕z2⊕a1⊕c1⊕c2⊕e2⊕e3⊕f1⊕f3⊕g1⊕g2⊕g3 которые поступают на седьмые входы узла памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора, блока корректоров и к входам выходного блока кодирования, который формирует значения проверочных контрольных разрядов r1П, r2П, r3П, r4П, r5П, r6П путем сложения по модулю 2 информационных символов x1П x2П x3П, z1П z2П z3П, a1П а2П а3П, с1П с2П с3П, е1П е2П е3П, f1П f2П f3П, g1П g2П g3П, h1п h2П h3П, поступающих на входы входного блока кодирования с информационных выходов узла памяти, в соответствии с правилом: r1П=х1П⊕z1П⊕а1П⊕с1П⊕е1П⊕f1П⊕g1П⊕h1П; r2П=x2П⊕z2П⊕а2П ⊕с2П⊕е2П⊕f2П⊕g2П⊕h2П; r3П=x3П⊕z3П⊕a3П⊕c3П⊕e3П⊕f3П⊕g3П⊕h3П; r4П=x1П⊕z3П⊕а2П⊕a2П⊕c2П⊕c3П⊕e1П⊕e3П⊕f1П⊕f2Пg1П⊕g2П⊕g3П; r5П=x2П⊕z1П⊕a3П⊕c1П⊕c3П⊕e1П⊕e2П⊕f2П⊕f3П⊕g1П⊕g2П⊕g3П; r6П=x3П⊕z2П⊕a1П⊕c1П⊕c2П⊕e2П⊕e3П⊕f1П⊕f3П⊕g1П⊕g2П⊕g3П, выходы выходного блока кодирования подключены к первым входам блока вычисления синдрома ошибки к вторым входам которого, подключены выходы контрольных разрядов узла памяти, первые выходы блока вычисления синдрома ошибки подключены к первым входам дешифратора, к первым входам коммутатора, к входам первого блока элементов ИЛИ и к первым входам блока коммутаторов, вторые выходы блока вычисления синдрома ошибки подключены к вторым входам дешифратора и к вторым входам первого блока элементов ИЛИ, выходы дешифратора подключены к входам второго блока элементов ИЛИ, при этом первый выход дешифратора подключен к второму входу коммутатора, а вторые выходы подключены к вторым входам блока коммутаторов, выход второго блока элементов ИЛИ через инвертор подключен к первому входу элемента И, второй вход которого подключен к выходу первого блока элементов ИЛИ, выход элемента И является выходом сигнала «ошибка», выходы коммутатора подключены к вторым входам корректора, выходы блока коммутаторов подключены к вторым входам блока корректоров, выходы корректора и блока корректоров подключены к вторым входам блока элементов И, выходы которого являются информационными выходами устройства.

Недостатком устройства является невозможность обнаруживать и корректировать одиночные ошибки при считывании информации с его инверсных выходов, которая необходима для представления отрицательного числа в дополнительном коде, используемого при выполнении арифметико-логическим устройством процессора операции вычитания, деления, умножения при наличии разных знаков у множимого и множителя.

Задачей изобретения является повышение отказоустойчивости устройства хранения информации за счет обнаружения и коррекции одиночных ошибок при считывании информации с прямых и инверсных выходов устройства на основе корректирующего кода, у которого проверочные разряды имеют одинаковые значения для прямых и инверсных значений информационных разрядов.

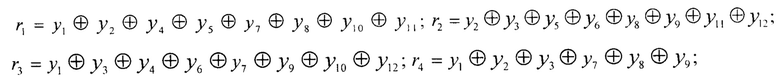

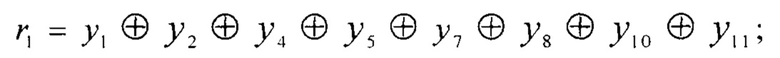

Сущность изобретения заключается в том, что устройство хранения и считывания информации, содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, корректор, первый блок элементов И, выходы которого являются выходами устройства, первый блок элементов ИЛИ, элемент И, выход которого является выходом устройства «ошибка» вход установки в нулевое состояние, вход записи, адресные входы, информационные входы, вход считывания прямых значений информационных разрядов, вход синхронизации, подключенные соответственно с первого по шестой входам узла памяти отличающееся тем, что он дополнительно содержит второй блок элементов И, третий блок элементов И, второй блок элементов ИЛИ, вход считывание инверсных значений информационных разрядов, причем входной блок кодирования, при записи информации в узел памяти, для двенадцати информационных разрядов, формирует значения проверочных разрядов по правилу:

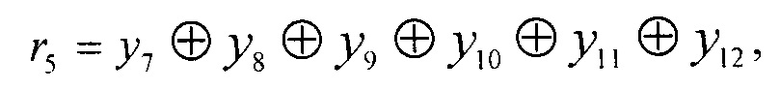

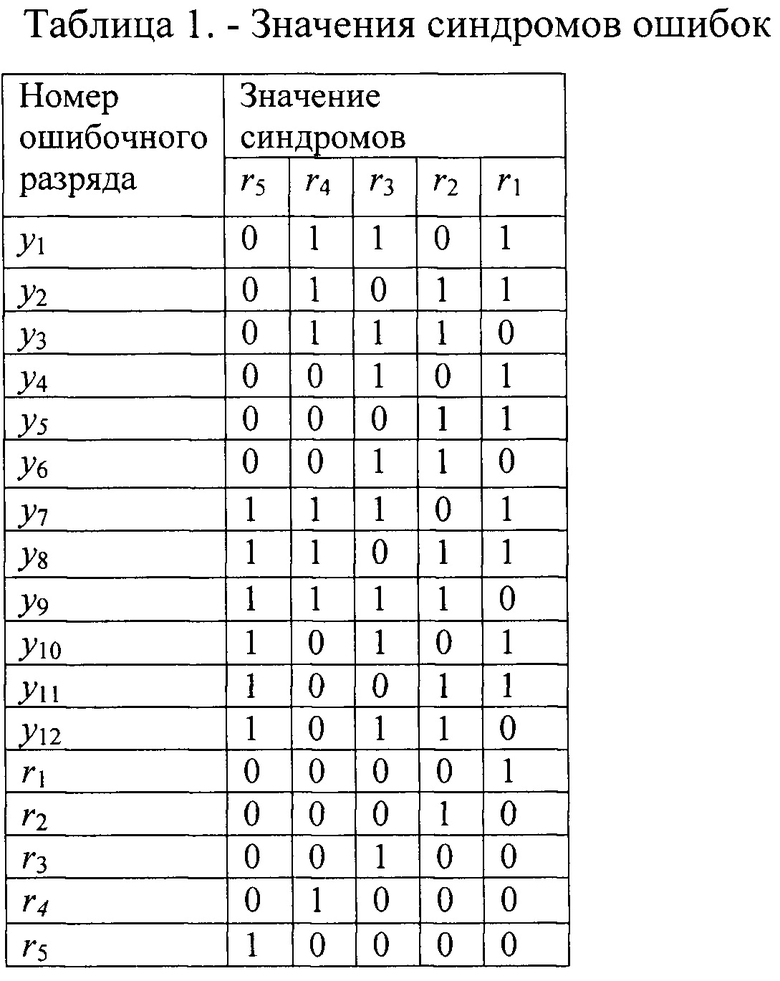

выходной блок кодирования, при считывании информации с узла памяти, формирует значения проверочных разрядов по правилу:

выходной блок кодирования, при считывании информации с узла памяти, формирует значения проверочных разрядов по правилу:

вход считывание инверсных значений информационных разрядов подключен к седьмому входу узла памяти и к первому входу второго блока элементов И, второй вход которого подключен к первым выходам узла памяти, а выходы подключены к первым входам второго блока элементов ИЛИ, вход считывание прямых значений информационных разрядов подключен к первому входу третьего блока элементов И, вторые входы которого подключены к вторым выходам узла памяти, а выходы подключены к первым входам корректора и к входам выходного блока кодирования, третьи выходы узла памяти подключены к вторым входам корректора и к первым входам блока вычисления синдрома ошибки вторые входы которого подключены к выходам входного блока кодирования, а выходы подключены к входам дешифратора и к входам первого блока элементов ИЛИ, выходы дешифратора подключены к третьим входам корректора, выходы которого подключены к первым входа первого блока элементов И, выход первого блока элементов ИЛИ подключен к первому входу элемента И, второй вход элемента И и второй вход первого блока элементов И подключены к входу синхронизации.

вход считывание инверсных значений информационных разрядов подключен к седьмому входу узла памяти и к первому входу второго блока элементов И, второй вход которого подключен к первым выходам узла памяти, а выходы подключены к первым входам второго блока элементов ИЛИ, вход считывание прямых значений информационных разрядов подключен к первому входу третьего блока элементов И, вторые входы которого подключены к вторым выходам узла памяти, а выходы подключены к первым входам корректора и к входам выходного блока кодирования, третьи выходы узла памяти подключены к вторым входам корректора и к первым входам блока вычисления синдрома ошибки вторые входы которого подключены к выходам входного блока кодирования, а выходы подключены к входам дешифратора и к входам первого блока элементов ИЛИ, выходы дешифратора подключены к третьим входам корректора, выходы которого подключены к первым входа первого блока элементов И, выход первого блока элементов ИЛИ подключен к первому входу элемента И, второй вход элемента И и второй вход первого блока элементов И подключены к входу синхронизации.

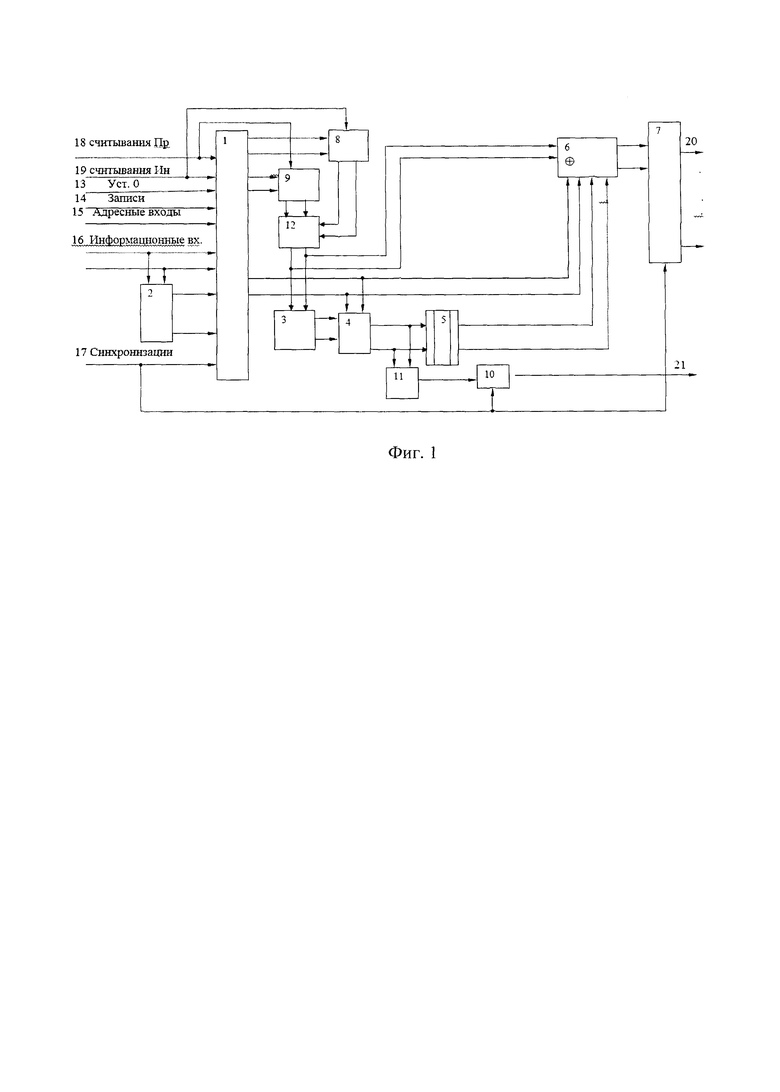

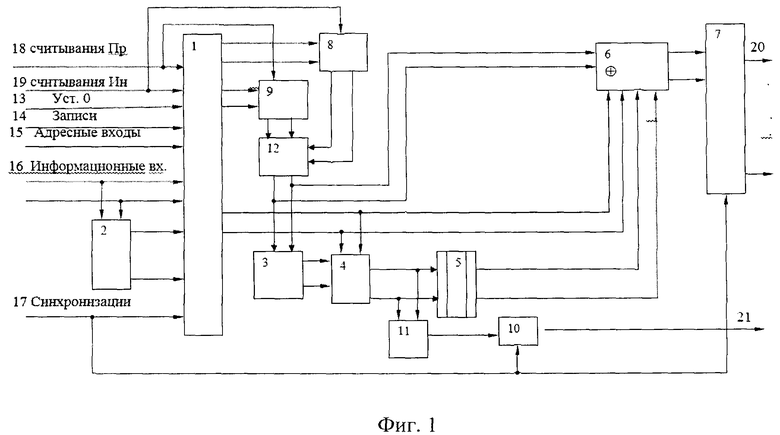

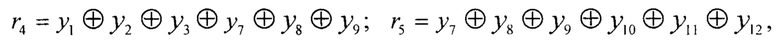

Устройство хранения и считывания информации с коррекцией одиночных ошибок (фиг.1) содержит узел 1 памяти, входной блок 2 кодирования, выходной блок 3 кодирования, блок 4 вычисления синдрома ошибки, дешифратор 5, корректор 6, первый блок 7 элементов И, второй блок 8 элементов И, третий блок 9 элементов И, элемент 10 И, первый блок 11 элементов ИЛИ, второй блок 12 элементов ИЛИ, вход 13 установки в нулевое состояние, вход 14 записи, адресные входы 15, информационные входы 16, вход 17 синхронизации, вход 18 считывания прямых значений информационных разрядов, вход 19 считывание инверсных значений информационных разрядов, выходы 20 устройства, выход 21 «ошибка».

Вход 13 установки в нулевое состояние, вход 14 записи, адресные входы 15, информационные входы 16, вход 17 синхронизации, вход 18 считывания прямых значений информационных разрядов, подключены соответственно с первого по шестой входам узла 1 памяти, входной блок 2 кодирования, при записи информации в узел памяти, для двенадцати информационных разрядов, формирует значения проверочных разрядов по правилу:

r1=y1⊕y2⊕y4⊕y5⊕y7⊕y8⊕y10⊕y11; r2=y2⊕y3⊕y5⊕y6⊕y8⊕y9⊕y11⊕y12; r3=y1⊕y3⊕y4⊕y6⊕y7⊕y9⊕y10⊕y12; r4=y1⊕y2⊕y3⊕y7⊕y8⊕y9; r5=y7⊕y8⊕y9⊕y10⊕y11⊕y12, выходной блок 3 кодирования, при считывании информации с узла памяти, формирует значения проверочных разрядов по правилу:

вход 19 считывание инверсных значений информационных разрядов подключен к седьмому входу узла 1 памяти и к первому входу второго блока 8 элементов И, второй вход которого подключен к первым выходам узла 1 памяти, а выходы подключены к первым входам второго блока 12 элементов ИЛИ, вход 18 считывание прямых значений информационных разрядов подключен к первому входу третьего блока 9 элементов И, вторые входы которого подключены к вторым выходам узла 1 памяти, а выходы подключены к первым входам корректора 6 и к входам выходного блока 3 кодирования, третьи выходы узла 1 памяти подключены к вторым входам корректора 6 и к первым входам блока 4 вычисления синдрома ошибки вторые входы которого подключены к выходам входного блока 3 кодирования, а выходы подключены к входам дешифратора 5 и к входам первого блока 11 элементов ИЛИ, выходы дешифратора 5 подключены к третьим входам корректора 6, выходы которого подключены к первым входа первого блока 7 элементов И, выход первого блока элементов ИЛИ подключен к первому входу элемента 10 И, второй вход элемента 10 И и второй вход первого блока 7 элементов И подключены к входу 17 синхронизации.

вход 19 считывание инверсных значений информационных разрядов подключен к седьмому входу узла 1 памяти и к первому входу второго блока 8 элементов И, второй вход которого подключен к первым выходам узла 1 памяти, а выходы подключены к первым входам второго блока 12 элементов ИЛИ, вход 18 считывание прямых значений информационных разрядов подключен к первому входу третьего блока 9 элементов И, вторые входы которого подключены к вторым выходам узла 1 памяти, а выходы подключены к первым входам корректора 6 и к входам выходного блока 3 кодирования, третьи выходы узла 1 памяти подключены к вторым входам корректора 6 и к первым входам блока 4 вычисления синдрома ошибки вторые входы которого подключены к выходам входного блока 3 кодирования, а выходы подключены к входам дешифратора 5 и к входам первого блока 11 элементов ИЛИ, выходы дешифратора 5 подключены к третьим входам корректора 6, выходы которого подключены к первым входа первого блока 7 элементов И, выход первого блока элементов ИЛИ подключен к первому входу элемента 10 И, второй вход элемента 10 И и второй вход первого блока 7 элементов И подключены к входу 17 синхронизации.

Узел 1 памяти, в данном случае, представляет собой статическое полупроводниковое оперативное устройство памяти и предназначен для хранения кодовых слов: YK=y1y2y3y4y5y6 y7 y8y9, y10y11y12r1r2r3,r4,r5, полученных при кодировании исходной информации. Для считывания прямых значений информационных разрядов по указанному адресу, подается сигнал на открытие элементов второго блока 8 элементов И, а для считывания инверсных значений информационных разрядов, подается сигнал на открытие элементов третьего блока 9 элементов И. Считываемые прямые и инверсные значения информационных разрядов поступают на входы выходного блока 3 кодирования через второй блок 12 элементов ИЛИ.

Входной блок 2 кодирования предназначен для формирования значений проверочных разрядов r1, r2, r3, r4, r5 при записи значений информационных разрядов в узле 1 памяти, путем сложения по mod2 информационных символов в соответствии с правилом:

r1=y1⊕y2⊕y4⊕y5⊕y7⊕y8⊕y10⊕y11;

r2=y2⊕y3⊕y5⊕y6⊕y8⊕y9⊕y11⊕y12;

r3=y1⊕y3⊕y4⊕y6⊕y7⊕y9⊕y10⊕y12;

r4=y1⊕y2⊕y3⊕y7⊕y8⊕y9;

r5=y7⊕y8⊕y9⊕y10⊕y11⊕y12,

Выходной блок 3 кодирования предназначен формирования значений проверочных разрядов при считывании значений информационных разрядов из узла 1 памяти, путем сложения по mod2 информационных символов в соответствии с правилом:

Для рассматриваемого кода, в отличии от известных алгебраических линейных кодов, проверочные разряды имеют одинаковые значения для прямых и инверсных значений информационных разрядов.

Блок 4 вычисления синдрома ошибки предназначен для обнаружения ошибки в кодовом слове при считывании информации с узла 1 памяти путем сложения по mod2 значений проверочных разрядов r1, r2, r3, r4, r5, считываемых выходов узла 1 памяти, соответственно с значениями проверочных разрядов r1C, r2C, r3C, r4C, r5C,сформированных на выходах выходного блока 3 кодирования.

Нулевой результат суммы свидетельствует об отсутствии ошибки, и ее наличии в противном случае.

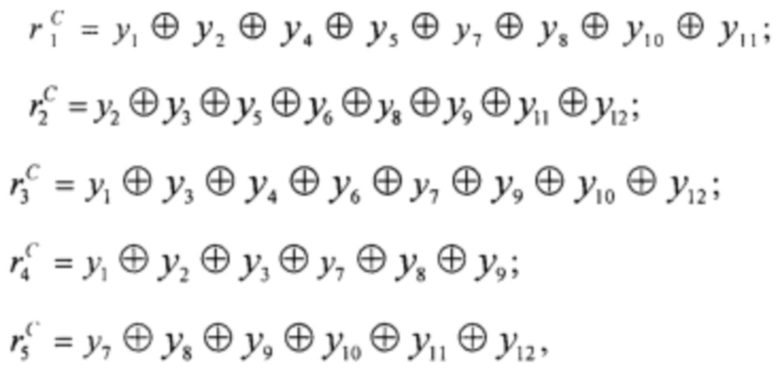

Значения синдромов ошибок для рассматриваемого кода представлены в таблице 1.

Сигналы с выходов блок 4 вычисления синдрома ошибки поступают на вход дешифратора 5 и объединены в один выход первым элементом 11 ИЛИ, значение сигнала на данном выходе поступает первый вход элемента 10 И.

При возникновении одиночной ошибки, на выходе дешифратора 5, соответствующего номеру ошибочного разряда, формируется единичное значение сигнала. В результате сложения по mod2 в корректоре 6 значения ошибочного разряда с единичным значением сигнала, поступающим с дешифратора 5, получим скорректированное значение ошибочного разряда.

Считывание выходной информации с выходов 20 устройства проводится при поступлении сигнала с входа 17 синхронизации на второй вход блока 7 элементов И и второй вход элемента 10 И.

Устройство работает следующим образом. Перед началом работы устройства, на вход 13 "Установки в нулевое состояние" подается единичный сигнал, который переводит элементы памяти в узле 1 памяти в нулевое состояние.

При записи информации в узел 1 памяти, подается единичный сигнал на вход 14 записи, адресные входы 15 и информационные входы 16. Например, имеем 12-разрядное слово памяти (нумерация информационных разрядов осуществляется с права на лево): A=000000001 100. В результате кодирования, поступающей информации входным блоком 2 кодирования, в узле 1 памяти запишется кодовый набор:AK= 000000001100 01011.

При выполнении операции инвертирования получим кодовый набор: AKИ=1111111110011 01011. Проверочные разряды инверсного кодового набора соответствуют полученному результату.

При считывании информации с узла 1 памяти и отсутствия в ней ошибки, на выходе, блока 4 вычисления синдрома ошибки получим нулевое значение синдрома ошибки. В этом случае, считываемая из узла 1 памяти информация, поступает на выходы 20 устройства без коррекции.

Допустим, произошла одиночная ошибка в 12-том информационном разряде, тогда, после кодирования считываемой информации выходным блоком 3 кодирования, получим значения проверочных разрядов: АK=1*00000001100 11101.

В результате поразрядного сложения по mod2 в блоке 4 вычисления синдрома ошибки переданных значений проверочных разрядов: 01011 с значениями проверочных разрядов: 11101, сформированных выходным блоком 3 кодирования, получим значение синдрома ошибки: 10110, которое соответствует возникновению ошибки в 12-ом информационном разряде.

В этом случае, на 12-ом выходе дешифратора 5 появится единичное значение сигнала, который обеспечит исправление значения данного в корректоре 6.

При поступлении импульса синхронизации, разрешается выдача информации на выходе первого блока 7 элементов И, и сигнала на выходе элемента 10И, свидетельствующего о возникновении ошибки.

Аналогичным образом устройство работает при записи, считывании и коррекции произвольных кодовых наборов.

Таким образом, в предлагаемом устройстве хранения и считывания информации осуществляется повышение его отказоустойчивости, за счет обнаружения и коррекции одиночных ошибок при считывании информации с прямых и инверсных выходов узла памяти, на основе корректирующего кода, у которого проверочные разряды имеют одинаковые значения для прямых и инверсных значений информационных разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С ПОВЫШЕННОЙ КОРРЕКТИРУЮЩЕЙ СПОСОБНОСТЬЮ | 2024 |

|

RU2829012C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК И ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2024 |

|

RU2826822C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2637426C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2621284C1 |

| КОНТРОЛИРУЕМОЕ УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ | 2015 |

|

RU2618388C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОДИНОЧНЫХ И ДВОЙНЫХ ОШИБОК | 2017 |

|

RU2659479C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| ОТКАЗОУСТОЙЧИВАЯ ЭВМ | 2018 |

|

RU2704325C1 |

| РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК В ДУБЛИРУЕМЫХ КАНАЛАХ | 2022 |

|

RU2826990C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

Изобретение относится к области вычислительной техники и может быть использовано для хранения и считывания информации с коррекцией одиночных ошибок. Техническим результатом является повышение отказоустойчивости устройства за счет обнаружения и коррекции одиночных ошибок при считывании информации с прямых и инверсных выходов устройства на основе корректирующего кода. Устройство содержит узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, корректор, первый блок элементов И, второй блок элементов И, третий блок элементов И, элемент И, первый блок элементов ИЛИ, второй блок элементов ИЛИ, вход установки в нулевое состояние, вход записи, адресные входы, информационные входы, вход синхронизации, вход считывания прямых значений информационных разрядов, вход считывание инверсных значений информационных разрядов, выходы устройства, выход «ошибка». 1 ил., 1 табл.

Устройство хранения и считывания информации с коррекцией одиночных ошибок, содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, корректор, первый блок элементов И, выходы которого являются выходами устройства, первый блок элементов ИЛИ, элемент И, выход которого является выходом устройства «ошибка» вход установки в нулевое состояние, вход записи, адресные входы, информационные входы, вход считывания прямых значений информационных разрядов, вход синхронизации, подключенные соответственно с первого по шестой входам узла памяти отличающееся тем, что он дополнительно содержит второй блок элементов И, третий блок элементов И, второй блок элементов ИЛИ, вход считывание инверсных значений информационных разрядов, причем входной блок кодирования, при записи информации в узел памяти, для двенадцати информационных разрядов, формирует значения проверочных разрядов по правилу:

выходной блок кодирования, при считывании информации с узла памяти, формирует значения проверочных разрядов по правилу:

выходной блок кодирования, при считывании информации с узла памяти, формирует значения проверочных разрядов по правилу:

вход считывание инверсных значений информационных разрядов подключен к седьмому входу узла памяти и к первому входу второго блока элементов И, второй вход которого подключен к первым выходам узла памяти, а выходы подключены к первым входам второго блока элементов ИЛИ, вход считывание прямых значений информационных разрядов подключен к первому входу третьего блока элементов И, вторые входы которого подключены к вторым выходам узла памяти, а выходы подключены к первым входам корректора и к входам выходного блока кодирования через второй блок элементов ИЛИ, третьи выходы узла памяти подключены к вторым входам корректора и к первым входам блока вычисления синдрома ошибки вторые входы которого подключены к выходам входного блока кодирования, а выходы подключены к входам дешифратора и к входам первого блока элементов ИЛИ, выходы дешифратора подключены к третьим входам корректора, выходы которого подключены к первым входа первого блока элементов И, выход первого блока элементов ИЛИ подключен к первому входу элемента И, второй вход элемента И и второй вход первого блока элементов И подключены к входу синхронизации.

вход считывание инверсных значений информационных разрядов подключен к седьмому входу узла памяти и к первому входу второго блока элементов И, второй вход которого подключен к первым выходам узла памяти, а выходы подключены к первым входам второго блока элементов ИЛИ, вход считывание прямых значений информационных разрядов подключен к первому входу третьего блока элементов И, вторые входы которого подключены к вторым выходам узла памяти, а выходы подключены к первым входам корректора и к входам выходного блока кодирования через второй блок элементов ИЛИ, третьи выходы узла памяти подключены к вторым входам корректора и к первым входам блока вычисления синдрома ошибки вторые входы которого подключены к выходам входного блока кодирования, а выходы подключены к входам дешифратора и к входам первого блока элементов ИЛИ, выходы дешифратора подключены к третьим входам корректора, выходы которого подключены к первым входа первого блока элементов И, выход первого блока элементов ИЛИ подключен к первому входу элемента И, второй вход элемента И и второй вход первого блока элементов И подключены к входу синхронизации.

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОДИНОЧНЫХ И ДВОЙНЫХ ОШИБОК | 2017 |

|

RU2659479C1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297032C2 |

| US 20130111303 A1, 02.05.2013 | |||

| CN 101281481 B, 16.06.2010 | |||

| US 4646304 A1, 24.02.1987. | |||

Авторы

Даты

2024-04-01—Публикация

2023-05-16—Подача