Известны асинхронные сумматоры Двух двоично-кодированных чисел, содержащие регистры-сумматоры исходных чисел и полусумматоры.

Предлагаемый сумматор отличается от известных тем, что он содержит линию разбиения на группы разрядов двух слов, получаемых на выходах полусумматоров, состоящую из последовательно соединенных схем «И - ИЛИ, при этом вторые входы элементов «И и «ИЛИ соединены соответственно с выходами «сумма и «перенос полусумматора данного разряда, входы которого соединены с единичными выходами триггеров данного разряда регистров исходных чисел, выход «сумма полусумматоров соединен также со входами схемы «неравнозначности данного разряда, второй вход которой соединен с выходом элемента «И, один вход которого соединен с выходом элемента «ИЛИ соседнего младщего разряда и «линия разбиения, а второй вход соединен с выходом схемы «конца разбиения, один вход которой соединен с шиной «начало суммирования, а остальные - выходами всех элементов «И линии разбиения.

Это позволяет повысить быстродействие сумматора.

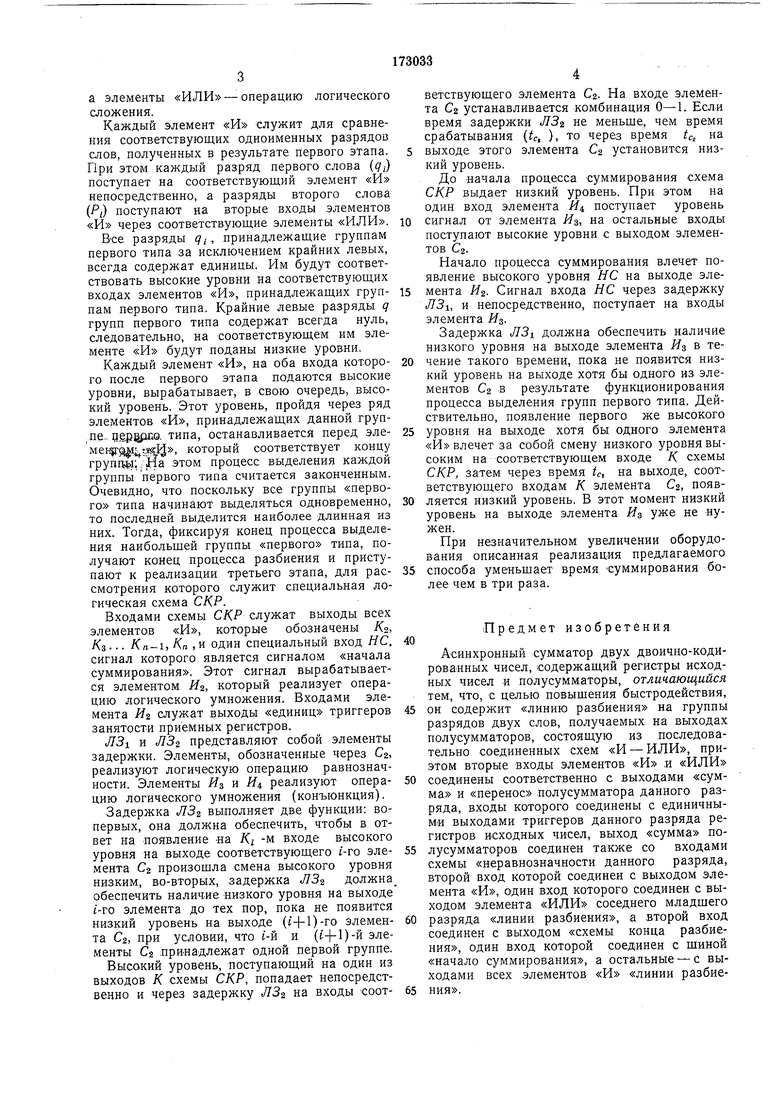

Схема сумматора содержит два приемных регистра: один состоит из триггеров TI, а второй - из триггеров Га, при этом крайние правые триггеры выполняют специальную функцию и называются триггерами занятости. Одновременно с засылкой слагаемого в регистр соответствующий триггер занятости «заполнит единицу.

Соответственно триггер занятости находится в «нулевом состоянии, когда соответствующий регистр пуст.

Поскольку непосредственный процесс суммирования начинается после того как оба слагаемых поступили в приемные регистры, то признаком начала суммирования может служить «единичное состояние обоих триггеров занятости.

Первый этап получения результата заключается в образования двух новых слов из исходных слагаемых и реализуется на полусумматорах, обозначенных на схеме через Стил. Выход «сумма каждого полусумматора выдает /-и разряд первого слова, а выход «перенос того же полусумматора выдает (гЧ-1)-й разряд второго слова. После осуществления первого этапа автоматически начинает реализовываться второй этап.

Второй этап реализуется цепочкой чередующихся элементов (см. на фиг. 1, это элементы «И и «ИЛИ), причем элементы «И реализуют операцию логического умножения,

а элементы «ИЛИ - операцию логического сложения.

Каждый элемент «И служит для сравнения соответствующих одноименных разрядов слов, полученных в результате первого этапа. При этом каждый разряд первого слова (9/) поступает на соответствующий элемент «И непосредственно, а разряды второго слова (PI) поступают на вторые входы элементов «И через соответствующие элементы «ИЛИ.

Все разряды qi, принадлежащие группам первого типа за исключением крайних левых, всегда содержат единицы. Им будут соответствовать высокие уровни на соответствующих входах элементов «И, принадлежащих группам первого типа. Крайние левые разряды q групп первого типа содержат всегда нуль, следовательно, на соответствующем им элементе «И будут поданы низкие уровни.

Каждый элемент «И, на оба входа которого после первого этапа подаются высокие уровни, вырабатывает, в свою очередь, высокий уровень. Этот уровень, пройдя через ряд элементов «И, принадлежащих данной груп,пе.. це|)йрц;о. типа, останавливается перед элеменр { щУ, который соответствует концу групцф ;;Йа этом процесс выделения каждой группы первого типа считается законченным. Очевидно, что поскольку все группы «первого типа начинают выделяться одновременно, то последней выделится наиболее длинная из них. Тогда, фиксируя конец процесса выделения наибольщей группы «первого типа, получают конец процесса разбиения и приступают к реализации третьего этапа, для рассмотрения которого служит специальная логическая схема СКР.

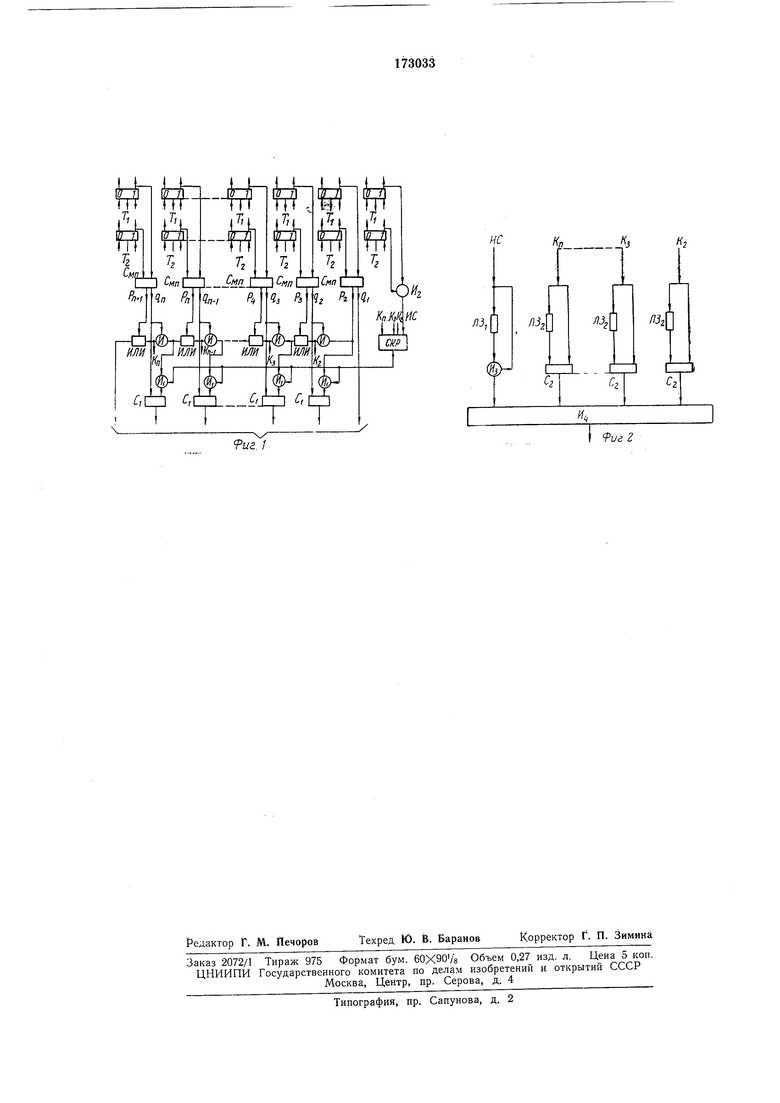

Входами схемы СКР служат выходы всех элементов «И, которые обозначены Kzt Дз... /Ся-,/(п , и один специальный вход ЯС, сигнал которого является сигналом «начала суммирования. Этот сигнал вырабатывается элементом Яа, который реализует операцию логического умножения. Входами элемента HZ служат выходы «единиц триггеров занятости приемных регистров.

Л31 и ЛЗг представляют собой элементы задержки. Элементы, обозначенные через Са, реал.изуют логическую операцию равнозначности. Элементы Яз и И реализуют операцию логического умножения (конъюнкция).

Задержка Л32 выполняет две функции: вопервых, она должна обеспечить, чтобы в ответ на цоявление «а KI -м входе высокого уровня на выходе соответствующего г-го элемента Са нроизошла смена высокого уровня низким, во-вторых, задержка ЛЗ должна обеспечить наличие низкого уровня на выходе {-го элемента до тех пор, пока не появится низкий уровень на выходе (i-|-l)-ro элемента Са, при условии, что t-й и (1-)-1)-й элементы Са принадлежат одной первой группе.

ветствующего элемента С. На входе элемента Са устанавливается комбинация 0-1. Есл-и время задержки ЛЗ не меньще, чем время срабатывания (tc, ), то через время tc на выходе этого элемента Са установится низкий уровень.

До Начала процесса -суммирования схема СКР выдает низкий уровень. При этом на один вход элемента И поступает уровень

сигнал от элемента Яз, на остальные входы поступают высокие уровни с выходом элементов Cz.

Начало процесса суммирования влечет появление высокого уровня НС на выходе элемента Яа. Сигнал входа НС через задержку ЛЗ, и непосредственно, поступает на входы элемента Яз.

Задержка i/73i должна обеспечить наличие низкого уровня на выходе элемента Яз в течение такого времени, пока не появится низкий уровень на выходе хотя бы одного из элементов Са :В результате функционирования процесса выделения групп первого типа. Действительно, появление первого же высокого

уровня на выходе хотя бы одного элемента «И влечет за собой смену низкого уровня высоким на соответствующем входе К схемы СКР, затем через время tc, на выходе, соответствующего входам К элемента Са, появляется низкий уровень. В этот момент низкий уровень на выходе элемента Яз уже не нужен.

При незначительном увеличении оборудования описанная реализация предлагаемого

способа уменьщает время суммирования более чем в три раза.

|Предмет изобретения

40

Асинхронный сумматор двух двоично-кодированных чисел, содержащий регистры исходных чисел и полусумматоры, отличающийся тем, что, с целью повыщения быстродействия,

он содержит «линию разбиения на группы разрядов двух слов, получаемых на выходах полусумматоров, состоящую из последовательно соединенных схем «И - ИЛИ, приэтом вторые входы элементов «И и «ИЛИ

соединены соответственно с выходами «сумма и «перенос полусумматора данного разряда, входы которого соединены с единичныМ.И выходами триггеров данного разряда регистров исходных чисел, выход «сумма полусумматоров соединен также со входами схемы «неравнозначности данного разряда, второй вход которой соединен с выходом элемента «И, один вход которого соединен с выходом элемента «ИЛИ соседнего младщего

разряда «линии разбиения, а второй вход соединен с выходом «схемы конца разбиения, один вход которой соединен с щиной «начало суммирования, а остальные -с выходами всех элементов «И «линии разбиелз.

9veZ

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Генератор случайных чисел | 1987 |

|

SU1495788A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Процессорный элемент | 1980 |

|

SU881757A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| Устройство для измерения индикаторной мощности поршневых машин | 1978 |

|

SU777522A2 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Демодулятор широтно-импульсного модулированного сигнала | 1984 |

|

SU1265988A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

Даты

1965-01-01—Публикация