1

Изобретение относится к вычислительной технике и может быть использовано при построении параллельных процессоров и однородных вычислительных систем, предназначенных для групповой обработки больших массивов информации .

Известен процессорный элемент, представляющий собой последовательность одноразрядных ячеек ассоциативной памяти, объединенных горизонтальными шинами разрешения записи и разрешения считывания информации, а также шиной совпадения содержимого этих ячеек с кодом опроса, подаваемым по шинам опроса 1.

Недостатком такого процессорного элемента является его низкое быстродействие при выполнении арифметических и логических операций, которое обусловлено тем, что арифметические и логические операции над словами в процессорном элементе выполняются . последовательно поразрядно(последовательно разряд за разрядом).причем обработка каждого разряда требует нескольких машинных тактов опросазаписи. Кроме того, в данном процессорном элементе для хранения промежуточных результатов операций требуются дополнительные аппаратурные затраты.

Известен ассоциативный матричный модуль, в котором обрабатываемые данные находятся в ассоциативном запоминающем устройстве, содержащем 25% по 256 разрядов и соединенным с тремя 5-разрядными регистрами X, У, М. Регистры X и У имеют логическую надстройку, способную выполнять любую из 16 логических операций над двумя одноразрядными двоичными переменными. Выполнение операций обработки данных заключается в одновременном считывании i-ых и/или j-ых разрядов каждого слова данных в соответствующие разряды регистров X и/или У, параллельной обработкой считываемых разрядов с помощью логической надстройки и записи результатов в одноименные разряды слов ассорциативных ЗУ 2,

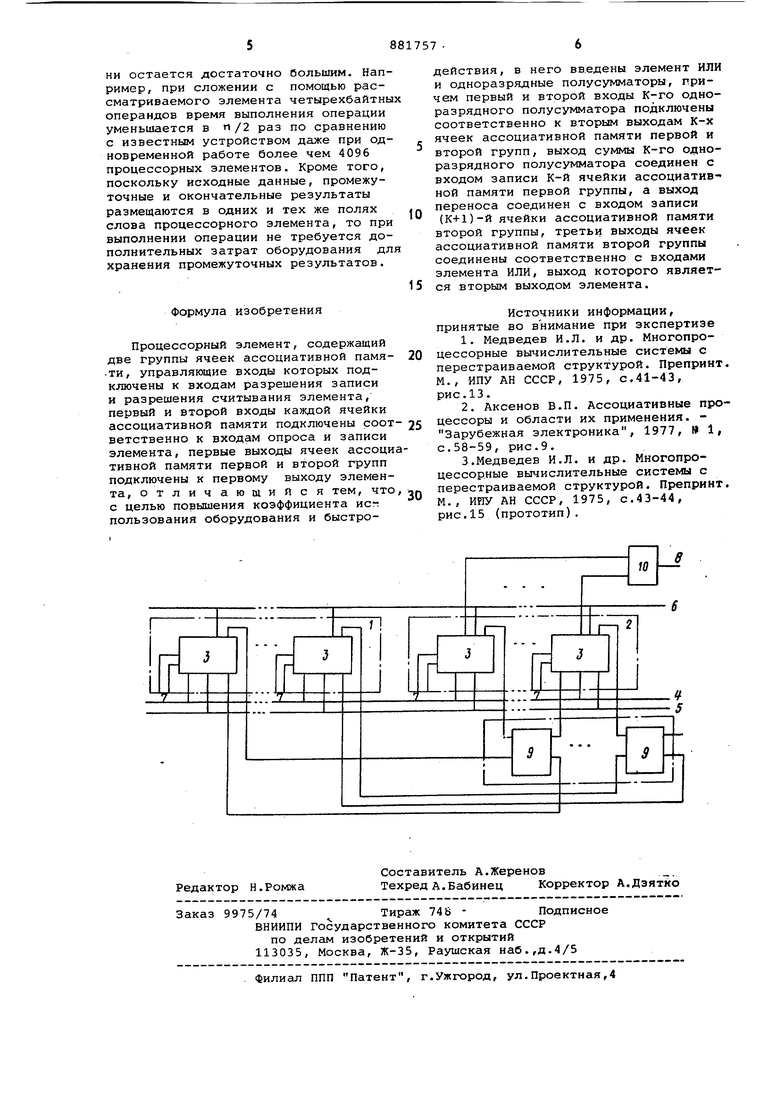

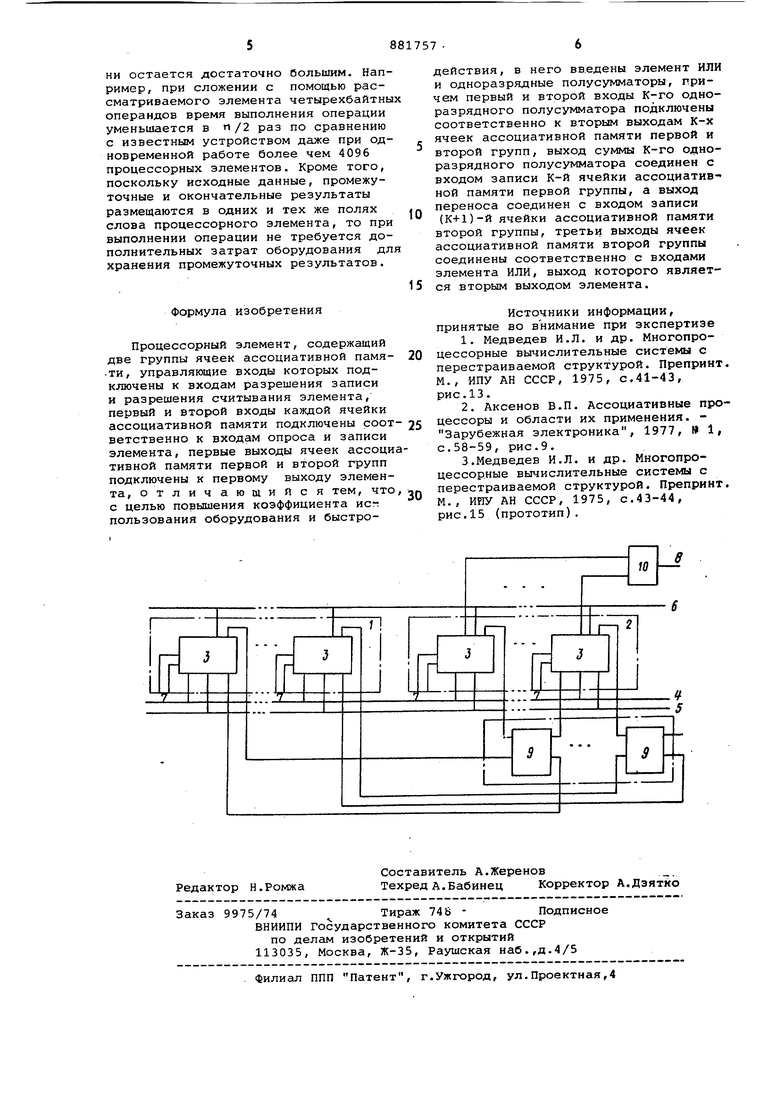

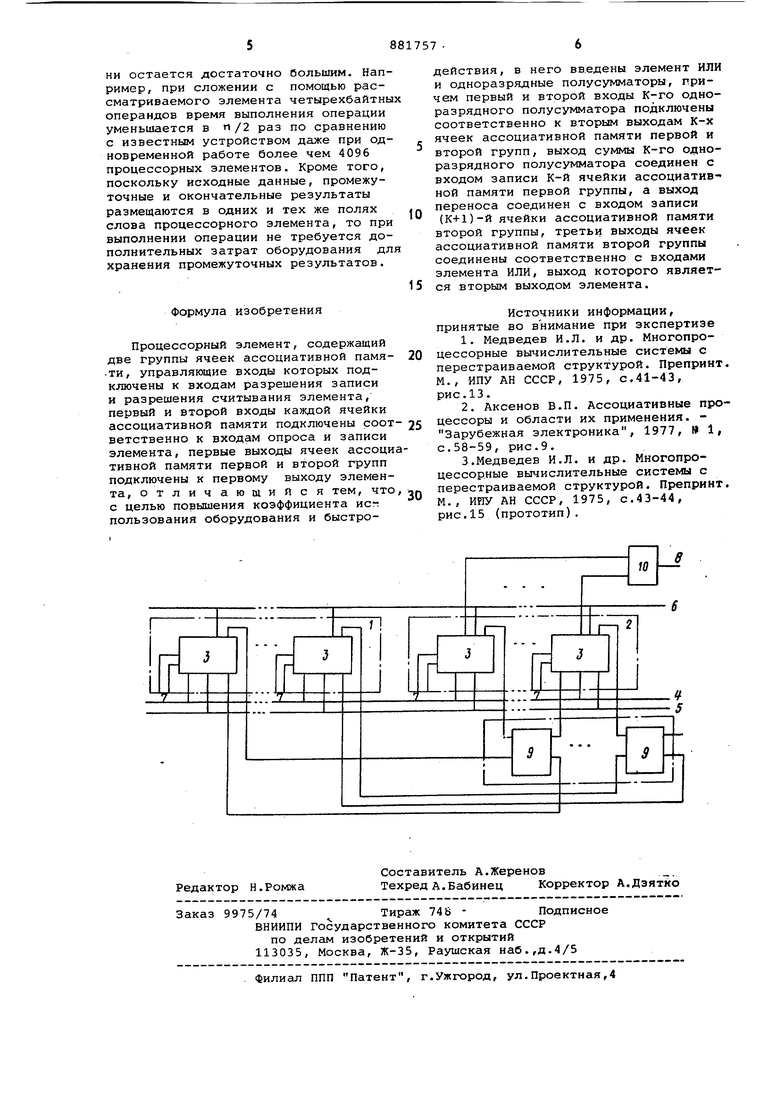

Для такого процессорного элемента характерно низкое быстродействие, обусловленное последовательной поразрядной пересылкой данных в обрабатывающее устройство и обратно, последовательной поразрядной обработкой данных, а для выполнения арифметических одноразрядных операций требуется несколько машинных тактов. Наиболее близким по технической сущности к изобретению является эле. мент, оснащенный одноразрядным комбинационным сумматором, в котором комбинационный сумматор выполняет как свои обычные функции арифметического устройства, так и функции устройства выборки по. содержанию. В этом процессорном элементе строка ассоциативных ячеек Ламяти разделяется на две группы, где хранятся операнды А и В. Выходы совпадения ячеек каждой группы объединяются собственными шинами совпадения(МС1, МС2), которые подключаются на входы комбинационного сумматора, третий вход которого соединен со схемой запоминания переноса. Входы разрешения записи всех ячеек через шину разрешения записи РЗ подключены к выходу суммы сумматора. Арифметические и логические операции в указанном процессорном элементе выполняются последовательно поразрядно при помощи микроопераций опрос-запись.Опрос одноименныхi-x разрядов обоих операндов на единичное значение осуществляется одновременно, в резуль Tafe чего на шине РЗ появляется сиг нал, равный результату суммирования ,+П, а в схему запоминания переноса заносится результат П, где а ,Ь- - содержимое 1-ых разрядов слагаемых, П - значение переноса из предыдущего разряда 3 Однако низкое.быстродействие элемента связано с последовательным поразрядным выполнением операций (х тя одноразрядные операции выполняют ся за один такт, число тактов равно разрядности операндов). Дополнитель .ные затраты оборудования связаны с тем, что для хранения результатов операции необходимо иметь дополните ную свободную зону. Цель изобретения - повышение коэ фициента использования оборудования и быстродействия. Поставленная цель достигается те что в процессорный элемент, содержащий две группы ячеек ассоциативной памяти, управляющие входы кото рых подключены к входам разрешения записи и разрешения считывания элемента, первый и второй входы каждой ассоциативной памяти подключены соответственно к входам опроса и записи элемента, первые выходы ячеек ассоциативной памяти первой и второй групп подключены к первому выходу элемента, введены элемент ИЛ и одноразрядные полусумматоры, прич первый и второй входы К-го одноразрядного полусумматора подключены со ответственно к вторым выходам К-Х ек ассоциативной памяти первой и в оП групп,выходы суммы К-го одноразядного полусумматора соединен с вхоом записи К-й ячейки ассоциативной амяти первой группы, а выход переноа соединен с входом записи (К+1)-и чейки ассоциативной памяти второй руппы, третьи выходы ячеек ассоциаивной памяти второй группы соединены оответственно с входами элемента ИЛИ-, выход которого является вторым выходом элемента. На чертеже представлена схема элемента. Элемент содержит группы 1 и 2 ячеек 3 ассоциативной памяти, входы 4 разрешения записи элемента,вход 5 разрешения считывания элемента,первый выход 6 элемента входы 7 опроса и записи элемента, второй выход 8 элемента, одноразрядные полусумматоры 9, элемент ИЛИ 10. Процессорный элемент работает следующим образом. Операции выборки по содержанию и ассоциативной обработки выполняются таким же образом, как и в известном устройстве. При выполнении операции арифметического сложения один операнд (например. А) помещается в первую группу 1 ячеек 3 ассоциативной памяти, а второй операнд (например, в ) - во вторую группу 2 ячеек 3 ассоциативной памяти. Операция арифметического сложения выполняется по шагам поразрядно параллельно (одновременно) над всеми разрядами операндов. После первого шага выполнения операции в ячейках 3 ассоциативной памяти первой группы 1 формируется результат А., а в ячейках второй группы В 2. Соответственно на каком-то j -м шаге выполнения операции формируются промежуточные результаты Aj Aj.f +Bj.., ; Bj(Aj. В )-2 Через 6 шагов выполнения операции (6 - длина максимальной цепочки, пе-о реноса, образовавшейся при сложении двух операндов) в ячейках 3 ассоциативной памяти первой группы 1 сформируется результат арифметического суммирования. Определение окончания формирования двоичной суммы в процессорном элементе производится элементом ИЛИ 10, который вырабатывает нулевой сигнал только при формировании промежуточного результата В 0, что свидетельствует о получении окончательного результата в ячейках первой группы. Поскольку средняя длина цепочки переноса, возникающей при сложении двух П -разрядных чисел равна logvn, то для сложения двух операндов в одном процессорном элементе в среднем требуется 1од2п тактов, При одновременном выполнении операций в нескольких процессорных элементах время выполнения операции увеличивается, однако выигрыш во време

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный процессорный элемент | 1982 |

|

SU1057938A1 |

| Ассоциативный процессорный элемент | 1980 |

|

SU879593A1 |

| Ассоциативный процессорный модуль | 1981 |

|

SU1015390A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| АССОЦИАТИВНОЕ ПАРАЛЛЕЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕУСТРОЙСТВО | 1970 |

|

SU288414A1 |

| Процессорный модуль | 1978 |

|

SU700863A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU924754A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Авторы

Даты

1981-11-15—Публикация

1980-01-30—Подача