Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах экспресс-обработки измерительной информации.

Целью изобретения является расширение функциональных возможностей путем определения среднего значения выборочного размаха знакопеременных сигналов.

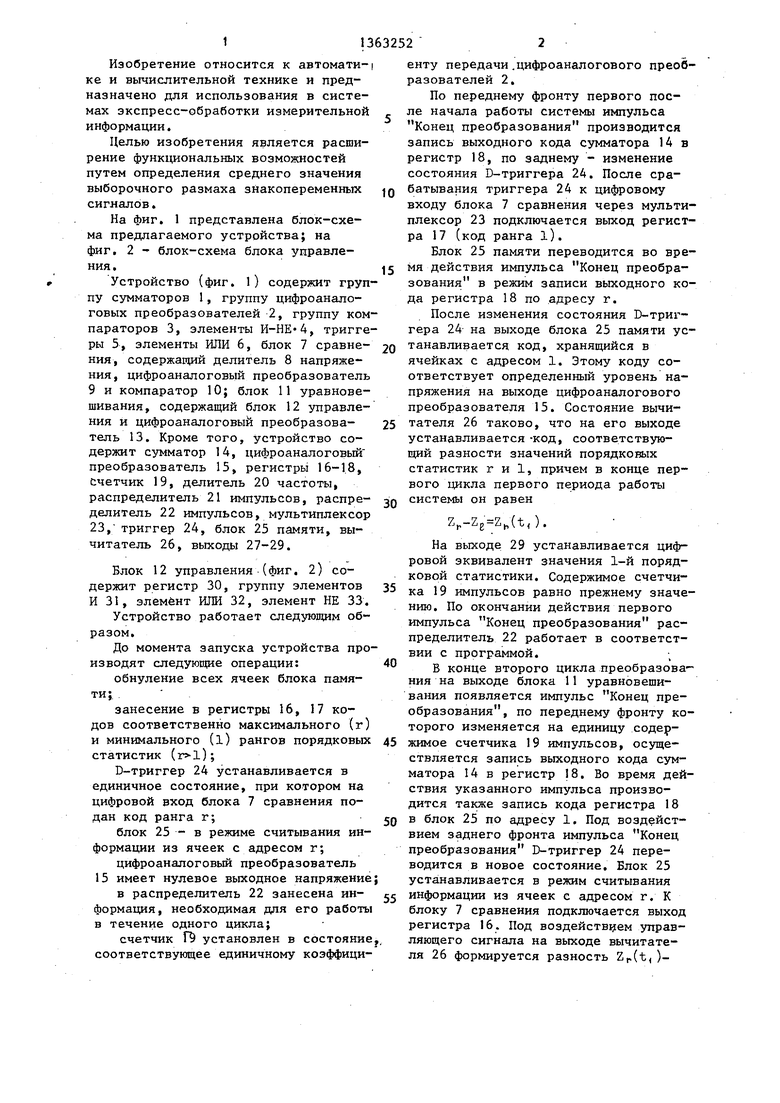

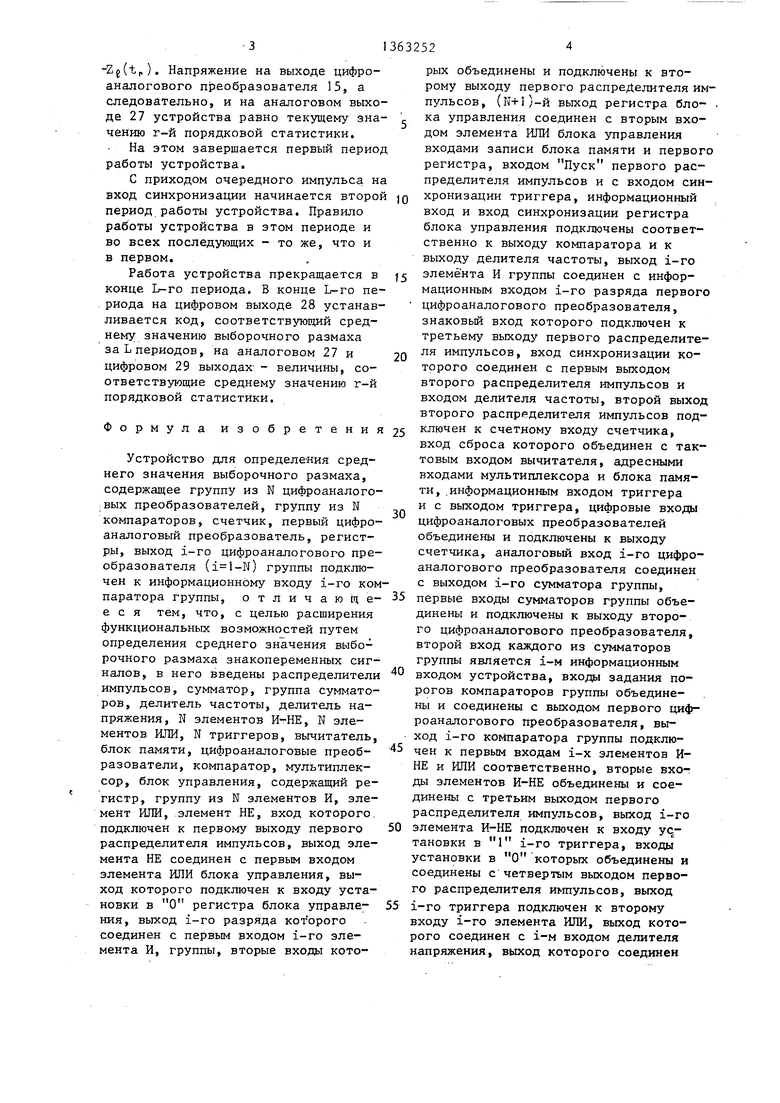

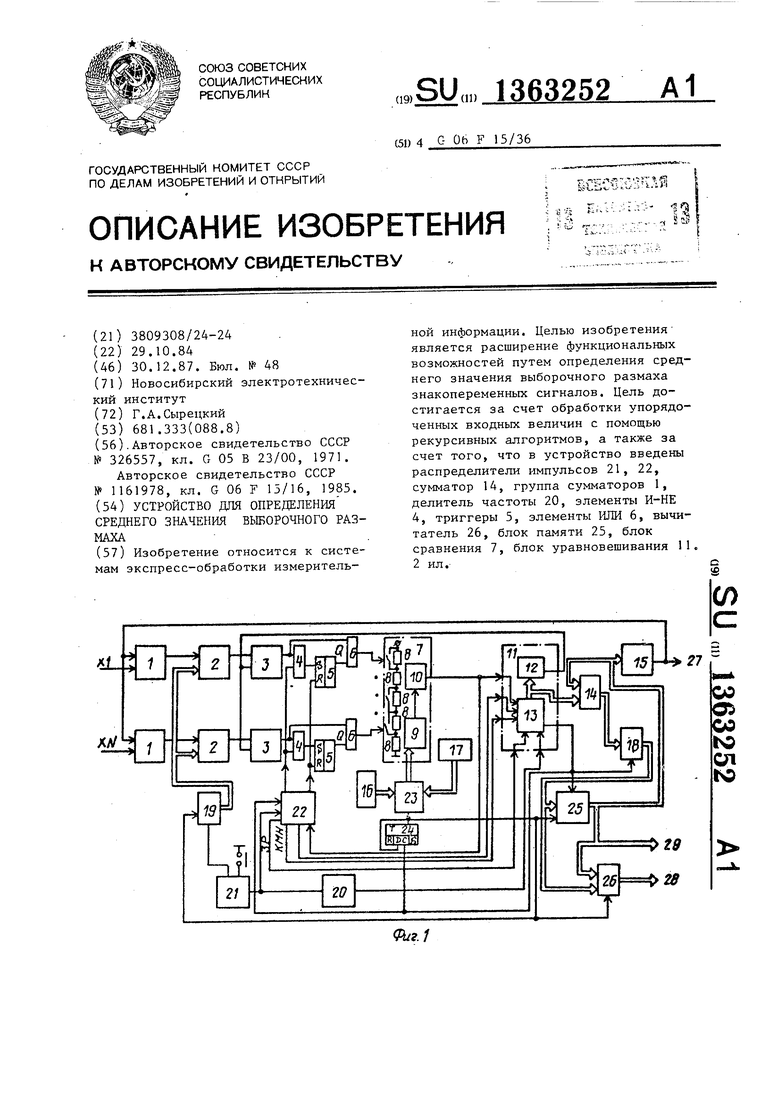

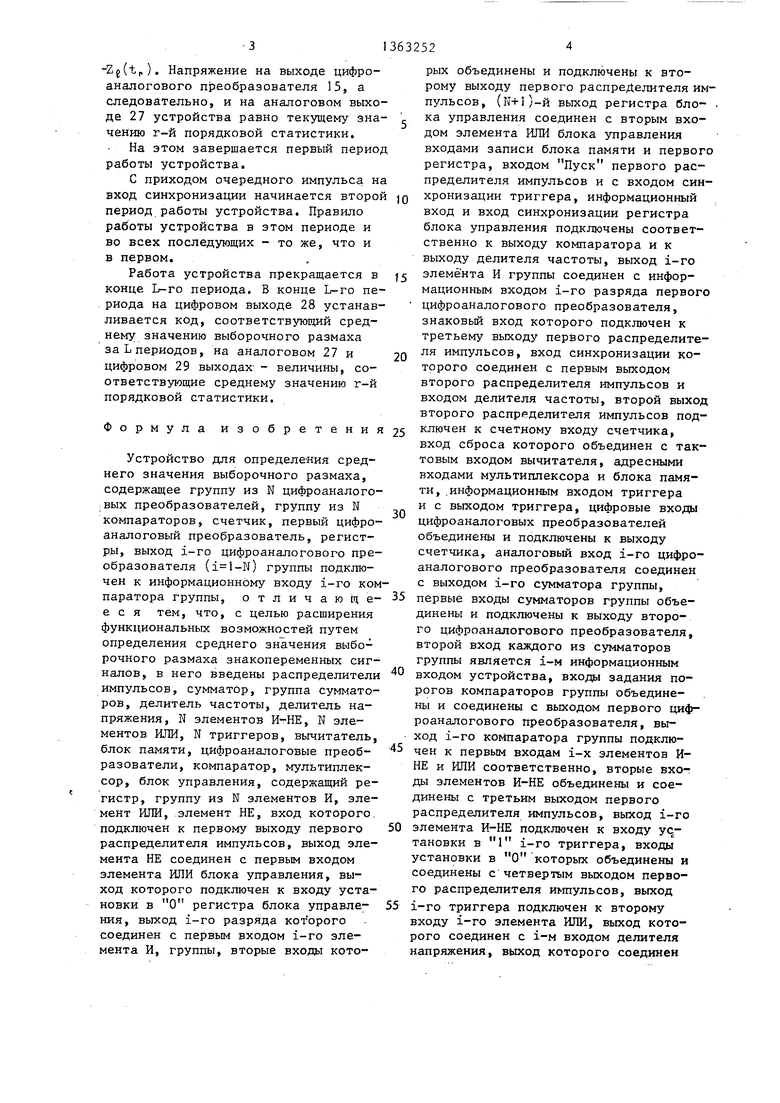

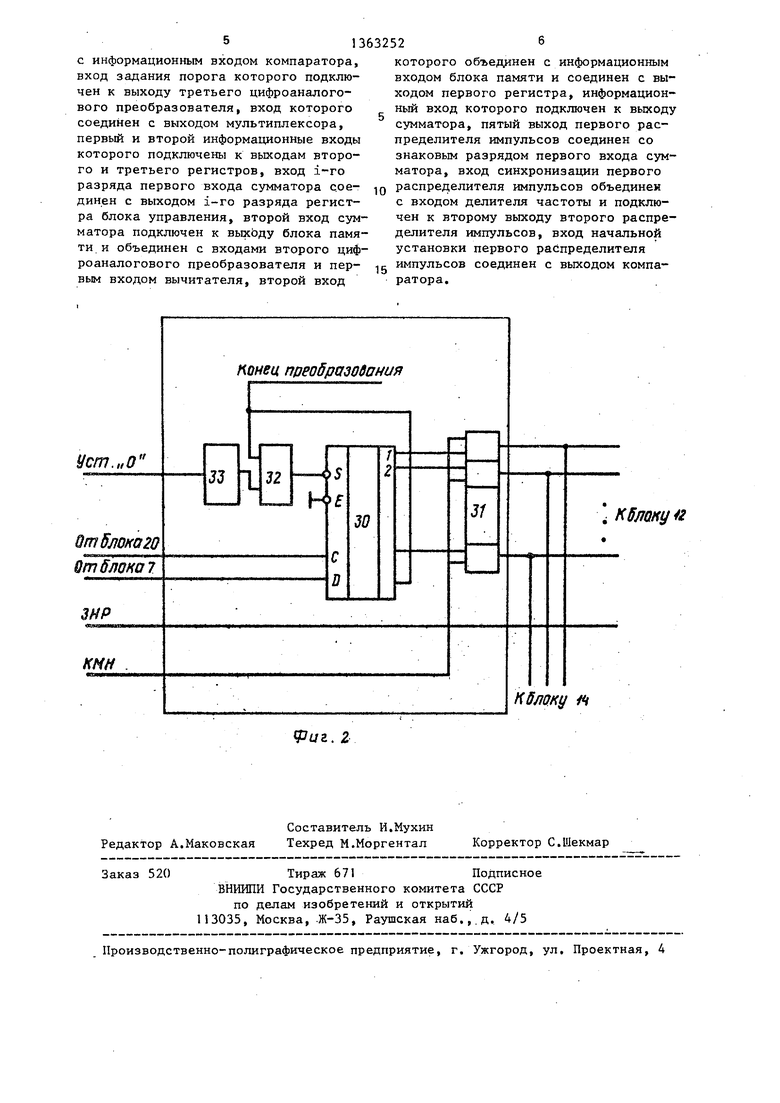

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг, 2 - блок-схема блока управления .

Устройство (фиг, 1) содержит группу сумматоров 1, группу цифроанало- говых преобразователей 2, группу компараторов 3, элементы И-НЕ 4, триггеры 5, элементы ИЛИ 6, блок 7 сравне- ния, содержащий делитель 8 напряжения, цифроаналоговый преобразователь 9 и компаратор 10; блок 11 уравновешивания , содержащий блок 12 управления и цифроаналоговый преобразова- тель 13, Кроме того, устройство содержит сумматор 14, цифроаналоговый преобразователь 15, регистры 16-1.8, счетчик 19, делитель 20 частоты, распределитель 21 импульсов, распре- делитель 22 импульсов, мультиплексор 23, триггер 24, блок 25 памяти, вы- читатель 26, выходы 27-29,

Блок 12 управления (фиг, 2) содержит регистр 30, группу элементов И 31, элемент ИЛИ 32, элемент НЕ 33,

Устройство работает следующим образом.

До момента запуска устройства производят следующие операции:

обнуление всех ячеек блока памяти;. . .

занесение в регистры 16, 17 кодов соответственно максимального (г) и минимального (l) рангов порядковых статистик ();

D-триггер 24 устанавливается в единичное состояние, при котором на цифровой вход блока 7 сравнения подан код ранга г;

блок 25 - в режиме считывания информации из ячеек с адресом г;

цифроаналоговый преобразователь 15 имеет нулевое выходное напряжение

в распределитель 22 занесена ин- формация, необходимая для его работы в течение одного цикла;

счетчик Г5 установлен в состояние соответствующее единичному коэффициенту передачи.цифроаналогового преобразователей 2,

По переднему фронту первого после начала работы системы импульса Конец преобразования производится запись выходного кода сумматора 14 в регистр 18, по заднему - изменение состояния D-триггера 24, После срабатывания триггера 24 к цифровому входу блока 7 сравнения через мультиплексор 23 подключается выход регистра 17 (код ранга 1),

Блок 25 памяти переводится во время действия импульса Конец преобразования в режим записи выходного кода регистра 18 по адресу г.

После изменения состояния D-триггера 24 на выходе блока 25 памяти устанавливается код, хранящийся в ячейках с адресом 1. Этому коду соответствует определенный уровень напряжения на выходе цифроаналогового преобразователя 15, Состояние вычи- тателя 26 таково, что на его выходе устанавливается -код, соответствующий разности значений порядковых статистик г и 1, причем в конце первого Цикла первого периода работы системы он равен

На выходе 29 устанавливается цифровой эквивалент значения 1-й порядковой статистики. Содержимое счетчика 19 импульсов равно прежнему значению. По окончании действия первого импульса Конец преобразования распределитель 22 работает в соответствии с программой,

В конце второго цикла преобразова ния на выходе блока 11 уравновешивания появляется импульс Конец преобразования, по переднему фронту которого изменяется на единицу содержимое счетчика 19 импульсов, осуществляется запись выходного кода сумматора 14 в регистр 18, Во время действия указанного импульса производится также запись кода регистра 18 в блок 25 по адресу 1, Под воздействием заднего фронта импульса Конец преобразования D-триггер 24 переводится в новое состояние. Блок 25 устанавливается в режим считывания информации из ячеек с адресом г, К блоку 7 сравнения подключается выход регистра 16. Под воздейств1 ем управляющего сигнала на выходе вычитате- ля 26 формируется разность Zf(tt )-Zg(tp). Напряжение на выходе цифро- аналогового преобразователя 15, а следовательно, и на аналоговом выходе 27 устройства равно текущему зна- чению г-й порядковой статистики.

На этом завершается первый период работы устройства.

С приходом очередного импульса на вход синхронизации начинается второй период работы устройства. Правило работы устройства в этом периоде и во всех последующих - то же, что и в первом.

Работа устройства прекращается в конце L-ro периода, В конце L-ro периода на цифровом выходе 28 устанавливается код, соответствующий среднему значению выборочного размаха заLпериодов, на аналоговом 27 и цифровом 29 выходах - величины, соответствующие среднему значению г-й порядковой статистики.

Формула изобретения

Устройство для определения среднего значения выборочного размаха, содержащее группу из N цифроаналого- :вых преобразователей, группу из N компараторов, счетчик, первый цифро- аналоговый преобразователь, регистры, выход i-ro цифроаналогового преобразователя () группы подключен к информационному входу i-ro компаратора группы, о т л и ч а ю щ е- вся тем, что, с целью расширения функциональных возможностей путем определения среднего значения выборочного размаха знакопеременных сигналов, в него введены распределители импульсов, сумматор, группа сумматоров, делитель частоты, делитель напряжения, N элементов И-НЕ, N элементов ИЛИ, N триггеров, вычитатель, блок памяти, цифроаналоговые преоб- разователи, компаратор, мультиплексор, блок управления, содержащий регистр, группу из N элементов И, элемент ИЛИ, элемент НЕ, вход которого, подключен к первому выходу первого распределителя импульсов, выход элемента НЕ соединен с первым входом элемента ИЛИ блока управления, выход которого подключен к входу установки в О регистра блока управле- ния, выход 1-го разряда кот орого соединен с первым входом i-ro элемента И, группы, вторые входы кото

,

о

5 0

5

г. 5

0

рых объединены и подключены к второму выходу первого распределителя импульсов, (N+I)-й выход регистра бло- . ка управления соединен с вторым входом элемента ИЛИ блока управления входами записи блока памяти и первого регистра, входом Пуск первого распределителя импульсов и с входом синхронизации триггера, информационный вход и вход синхронизации регистра блока управления подключены соответственно к выходу компаратора и к выходу делителя частоты, вьпсод i-ro элемента И группы соединен с информационным входом i-ro разряда первого цифроаналогового преобразователя, знаковьй вход которого подключен к третьему выходу первого распределителя импульсов, вход синхронизации которого соединен с первым выходом второго распределителя импульсов и входом делителя частоты, второй выход второго распределителя импульсов подключен к счетному входу счетчика, вход сброса которого объединен с тактовым входом вычитателя, адресными входами мультиплексора и блока памяти, .информационным входом триггера и с выходом триггера, цифровые входы цифроаналоговых преобразователей объединены и подключены к выходу счетчика, аналоговый вход i-ro цифро- аналогового преобразователя соединен с выходом i-ro сумматора группы, первые входы сумматоров группы объединены и подключены к выходу второго цифроаналогового преобразователя, второй вход каждого из сумматоров группы является i-м информационным входом устройства, входы задания порогов компараторов группы объединены и соединены с выходом первого цифроаналогового преобразователя, вьг- ход i-ro компаратора группы подключен к первьм входам i-x элементов И- НЕ и ИЛИ соответственно, вторые входы элементов И-НЕ объединены и соединены с третьим выходом первого распределителя импульсов, выход i-ro элемента И-НЕ подключен к входу установки в 1 i-ro триггера, входы установки в О которых объединены и соединены с четвертым выходом первого распределителя иьтульсов, выход

i-ro триггера подключен к второму входу i-ro элемента ИЛИ, выход которого соединен с i-м входом делителя напряжения, выход которого соединен

с информационным входом компаратора, вход задания порога которого подключен к выходу третьего цифроаналого- вого преобразователя, вход которого соединен с выходом мультиплексора, первый и второй информационные входы которого подключены к вькодам второго и третьего регистров, вход 1-го разряда первого входа сумматора соединен с выходом i-ro разряда регистра блока управления, второй вход сумматора подключен к выхЬду блока памяти и объединен с входами второго циф- роаналогового преобразователя и первым входом вычитателя, второй вход

понец преобразобания

. „О

33

1

J2

Ф5

К5

От блока 20

Qm 5лона 7

97цг. Z

Редактор А.Маковская

Составитель И.Мухин Техред М.Моргентал

Заказ 520Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, .Ж-35, Раушская наб.,.д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

которого объединен с информационным входом блока памяти и соединен с выходом первого регистра, информационный вход которого подключен к выходу сумматора, пятый выход первого распределителя импульсов соединен со знаковьм разрядом первого входа сумматора, вход синхронизации первого распределителя импульсов объединен с входом делителя частоты и подключен к второму выходу второго распределителя импульсов, вход начальной установки первого распределителя импульсов соединен с выходом компаратора.

30

31

i К5лону г

КОлоку л

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения корреляционной функции | 1984 |

|

SU1363255A1 |

| Устройство для определения автокорреляционной функции | 1984 |

|

SU1363254A1 |

| Устройство для определения текущей оценки среднего значения | 1984 |

|

SU1363251A1 |

| Устройство для определения функций плотности вероятностей | 1984 |

|

SU1363253A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

Изобретение относится к системам экспресс-обработки измерительной информации. Целью изобретения является расширение функциональных возможностей путем определения среднего значения выборочного размаха знакопеременных сигналов. Цель достигается за счет обработки упорядоченных входных величин с помощью рекурсивных алгоритмов, а также за счет того, что в устройство введены распределители импульсов 21, 22, сумматор 14, группа сумматоров 1, делитель частоты 20, элементы И-НЕ 4, триггеры 5, элементы ИЛИ 6, вычи- татель 26, блок памяти 25, блок сравнения 7, блок уравновешивания 11. 2 ил. с (С 27 00 а ел tS9 28

| 0 |

|

SU326557A1 | |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для вычисления текущей оценки среднего значения | 1983 |

|

SU1161978A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1984-10-29—Подача