СП

о

СО СО СО СО

Изобретение относится к вычислительной технике и может быть использовано для преобразования десятичных чисел в двоичные.

Целью изобретения является упрощение преобразователя

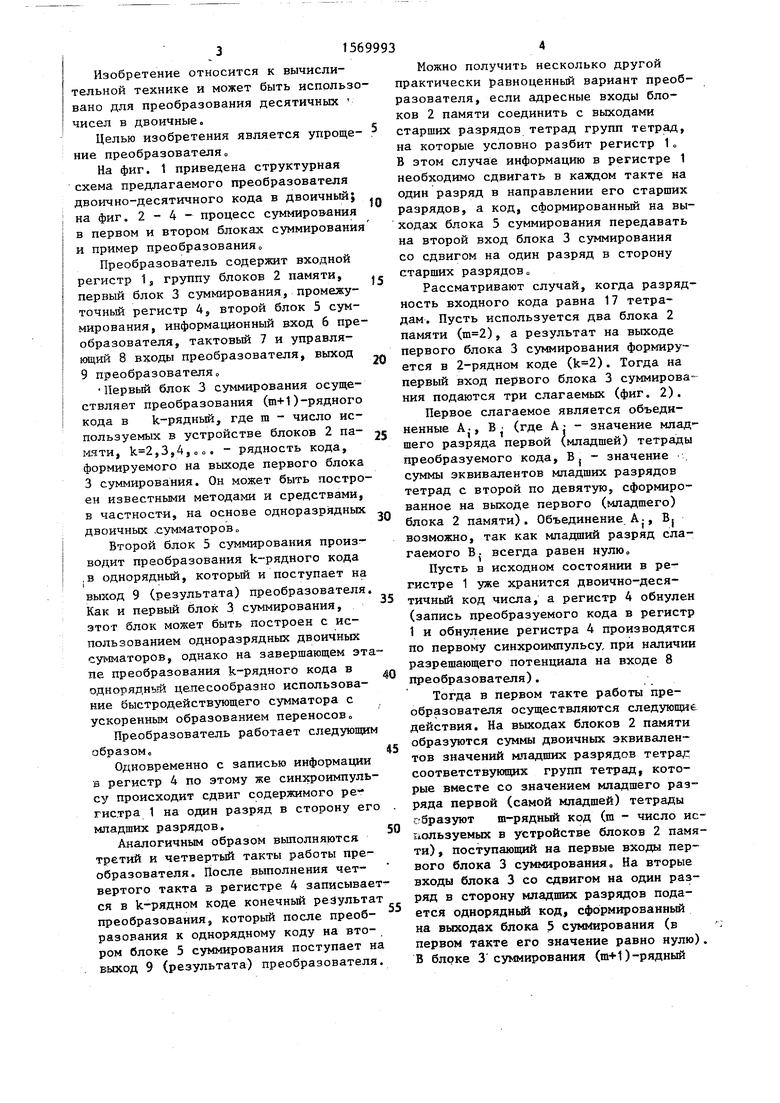

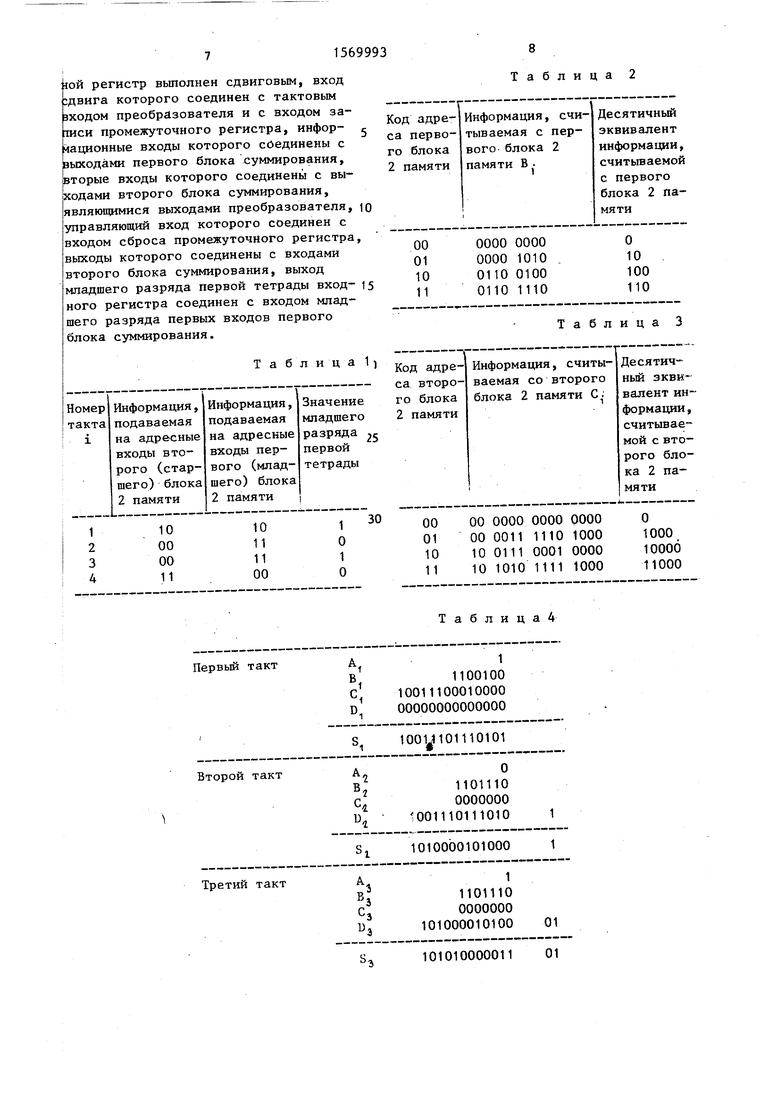

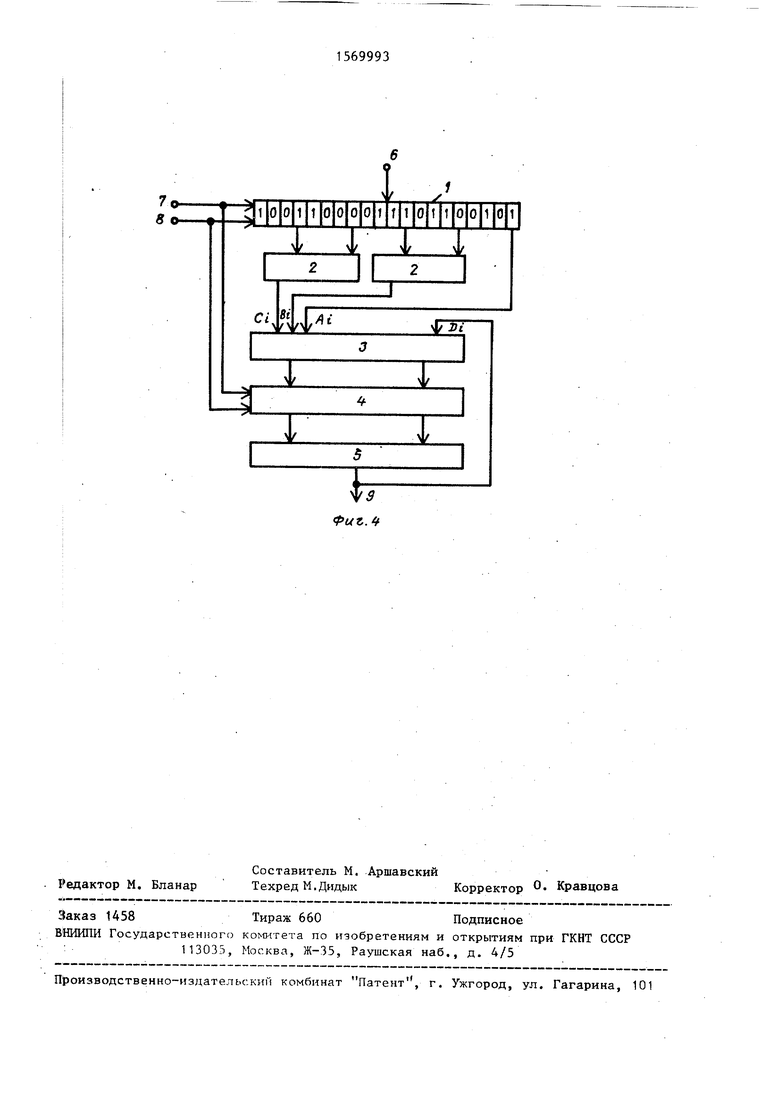

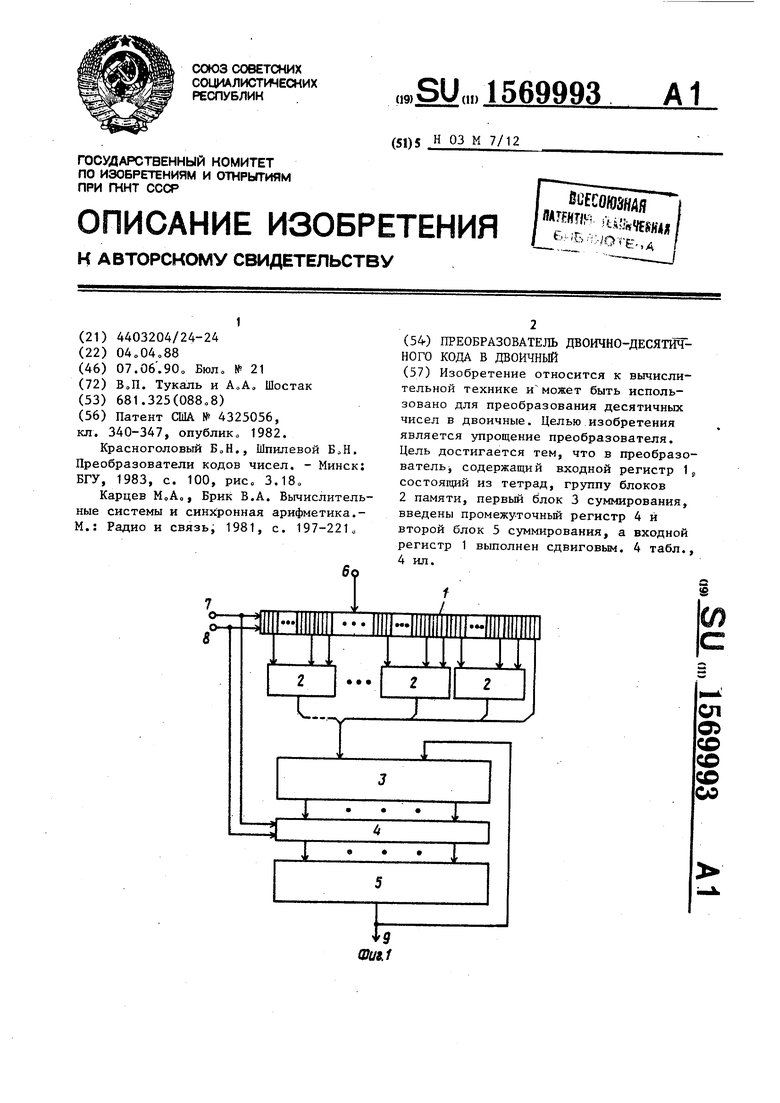

На фиг. 1 приведена структурная схема предлагаемого преобразователя двоично-десятичного кода в двоичный; на фиг. 2 - 4 - процесс суммирования в первом и втором блоках суммирования и пример преобразования.

Преобразователь содержит входной регистр 1, группу блоков 2 памяти, первый блок 3 суммирования, промежуточный регистр 4, второй блок 5 суммирования, информационный вход 6 преобразователя, тактовый 7 и управляющий 8 входы преобразователя, выход 9 преобразователя

Первый блок 3 суммирования осуществляет преобразования (ш+1)-рядного кода в k-рядный, где m - число используемых в устройстве блоков 2 памяти, ,3,4,0.. - рядность кода, формируемого на выходе первого блока 3 суммирования. Он может быть построен известными методами и средствами, в частности, на основе одноразрядных двоичных сумматоров

Второй блок 5 суммирования производит преобразования k-рядного кода в однорядный, который и поступает на выход 9 (результата) преобразователя Как и первый блок 3 суммирования, этот блок может быть построен с использованием одноразрядных двоичных сумматоров, однако на завершающем этапе преобразования k-рядного кода в однорядный целесообразно использование быстродействующего сумматора с ускоренным образованием переносов

Преобразователь работает следующим образом.

Одновременно с записью информации в регистр 4 по этому же синхроимпульсу происходит сдвиг содержимого регистра 1 на один разряд в сторону ег младших разрядов.

Аналогичным образом выполняются третий и четвертый такты работы преобразователя. После выполнения четвертого такта в регистре 4 записываеся в k-рядном коде конечный результа преобразования, который после преобразования к однорядному коду на втором блоке 5 суммирования поступает н выход 9 (результата) преобразователя

0

5

0

5

.Q

0

5

45

50

55

Можно получить несколько другой практически равноценный вариант преобразователя, если адресные входы блоков 2 памяти соединить с выходами старших разрядов тетрад групп тетрад, на которые условно разбит регистр 1„ В этом случае информацию в регистре 1 необходимо сдвигать в каждом такте на один разряд в направлении его старших разрядов, а код, сформированный на выходах блока 5 суммирования передавать на второй вход блока 3 суммирования со сдвигом на один разряд в сторону старших разрядов„

Рассматривают случай, когда разрядность входного кода равна 17 тетрадам. Пусть используется два блока 2 памяти (), а результат на выходе первого блока 3 суммирования формируется в 2-рядном коде (). Тогда на первый вход первого блока 3 суммирова ния подаются три слагаемых (фиг. 2).

Первое слагаемое является объединенные А-, В (где А: - значение младшего разряда первой (младшей) тетрады преобразуемого кода, В( - значение суммы эквивалентов младших разрядов тетрад с второй по девятую, сформированное на выходе первого (младшего) блока 2 памяти). Объединение А-, В, возможно, так как младший разряд слагаемого В всегда равен нулю.

Пусть в исходном состоянии в регистре 1 уже хранится двоично-десятичный код числа, а регистр 4 обнулен (запись преобразуемого кода в регистр 1 и обнуление регистра 4 производятся по первому синхроимпульсу, при наличии разрешающего потенциала на входе 8 преобразователя).

Тогда в первом такте работы преобразователя осуществляются следующие действия. На выходах блоков 2 памяти образуются суммы двоичных эквивалентов значений младших разрядов тетрадт соответствующих групп тетрад, которые вместе со значением младшего разряда первой (самой младшей) тетрады -бразуют m-рядный код (т - число используемых в устройстве блоков 2 памяти) , поступающий на первые входы первого блока 3 суммирования. На вторые входы блока 3 со сдвигом на один разряд в сторону младших разрядов подается однорядный код, сформированный на выходах блока 5 суммирования (в первом такте его значение равно нулю). В блоке 3 суммирования (т+1)-рядный

код преобразуется в k-рядный, который по приходу второго синхроимпульса с разрешения потенциала на входе 7 преобразователя записывается в регистр 4 „

Одновременно с записью информации в регистр 4 по этому же синхроимпульс происходит сдвиг информации в регистре 1 на один разряд в сторону его младших разрядов. На этом первый такт преобразования заканчивается

Во втором такте работы преобразователя одновременно с чтением следующих ЦПОИЧНЫУ эквивалентов из блоков 2 памяти происходит преобразование k-ряд- ного кода в однорядный вторым блоком 5 суммирования. Результат этого преобразования подается на второй вход первого блока 3 суммирования., По окон чании переходного процесса в блоке 3 и по приходу третьего синхроимпульса с разрешения потенциала на входе 7 преобразователя результат преобразования записывается в регистр 4,,

Второе слагаемое С - значение суммы эквивалентов младших разрядов тетрад с десятой по семнадцатую, сформированное на выходе второго (старшего) блока 2 памяти,

Третье слагаемое D. равно результату (S ), формируемому на выходе второго блока 5 суммирования, но сдвинутому в сторону младших разрядов на один разряд относительно слагаемых, подаваемых на первый вход первого блока 3 суммирования, т.е. D-

S,,/2 (в

На фиг. значения:

первом такте S

0).

2 приняты следующие обо

х е {о,1},

45

где i - номер такта работы устройства (i 1,2,3,4); (i-1) - предыдущий такт работы устройства.

Следовательно первый блок 3 суммирования является преобразователем

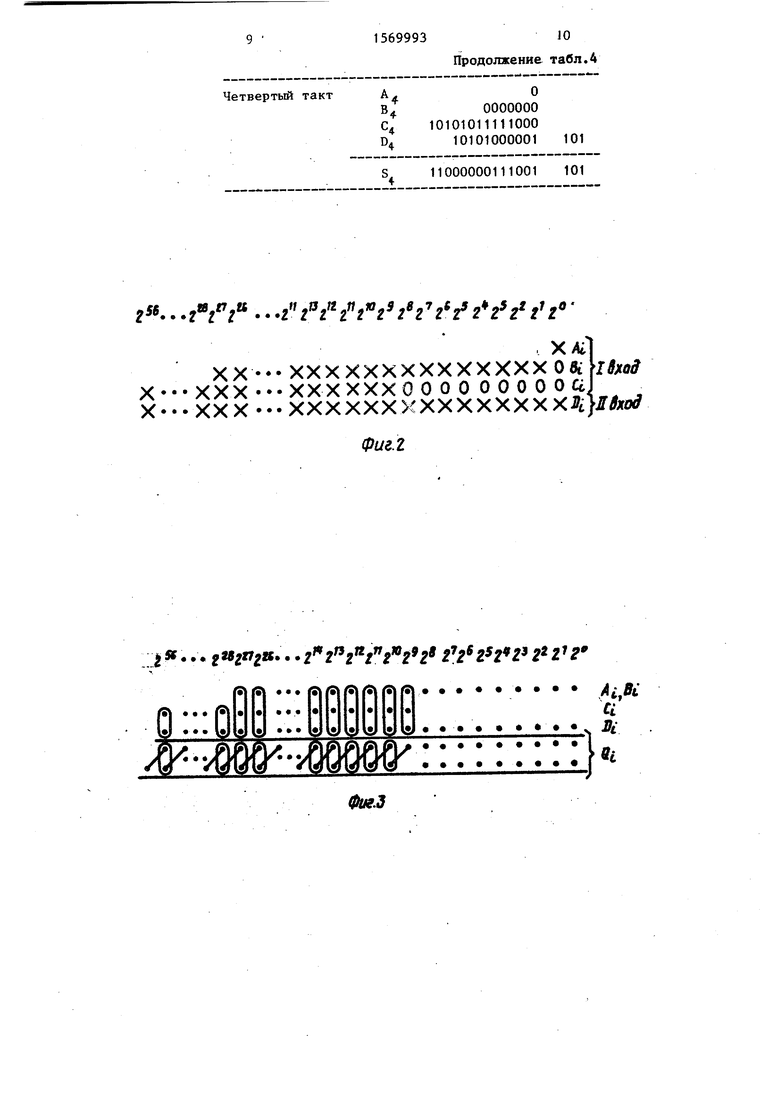

3-рядного кода в 2-рядный. Процесс преобразования 3-рядного кода в 2- рядный показан на фиг. 3, где . - двоичный разряд массива слагаемых, обрабатываемых в блоке 3; : - одноразрядный двоичный полусумматор; } - одноразрядный двоичный сумматор; Q. - промежуточный результат, сформированный на выходе первого блока 3 суммирования в 2-рядном коде; / - результат, формируемый на выходе одноразряд- ля, °н содержит второй блок суммиро50

55

Преобразователь двоично-десятично го кода в двоичный, содержащий входной регистр, состоящий из группы те рад, группу блоков памяти и первый блок суммирования, первые входы которого соединены с выходами блоков памяти группы в соответствии с весами двоичных эквивалентов, адресные входы блоков памяти группы соединены с выходами младших разрядов соответствующих тетрад входного регистра, информационные входы которого являются информационными входами преобразователя, управляющий вход которого соединен с входом записи входного регист ра,

отличающийся тем, что, с целью упрощения преобразовате5

д

0 5

0

5

0

5

ля, °н содержит второй блок суммиро0

5

матора (точка вверху является суммой одноразрядного двоичного сумматора или полусумматора; точка внизу - переносом одноразрядного сумматора или полусумматора).

Пример. Преобразование двоично-десятичного кода 1001 1000 0111

01100101 (2, 98765 (,„) в двоичный код. Предполагают, что используются два блока 2 памяти и результат на выходе первого блока 3 суммирования формируется в 2-рядном коде.

В регистре 1 (фиг„ 4) преобразуемого кода указано значение исходно : . кода, а на шинах отмечена их разрядность .

Значение разрядов, подаваемые в i-м такте на адресные входы первого и второго блоков 2 памяти, и значения младшего разряда первой тетрады приведены в табл. 1 .,

Суммы двоичных эквивалентов значений младших разрядов второй и третьей тетрад, записанные в первом блоке 2, памяти, и четвертой и пятой тет рад, записанные во втором блоке 2 памяти, приведены в табл. 2 и 3 соотве ственно.

Процесс преобразования в устройстве двоично-десятичного кода 1001 1000

01110110 0101 в двоичный код приведен в табл. 4j

Промежуточный этап формирования 2-рядного кода в табл. 4 опущен (Фиг. 3).

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный, содержащий входной регистр, состоящий из группы те рад, группу блоков памяти и первый блок суммирования, первые входы которого соединены с выходами блоков памяти группы в соответствии с весами двоичных эквивалентов, адресные входы блоков памяти группы соединены с выходами младших разрядов соответствующих тетрад входного регистра, информационные входы которого являются информационными входами преобразователя, управляющий вход которого соединен с входом записи входного регистра,

отличающийся тем, что, с целью упрощения преобразовате

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1649672A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1658387A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1662004A1 |

| Преобразователь двоичнодесятичного кода в двоичный | 1977 |

|

SU656052A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

Изобретение относится к вычислительной технике и может быть использовано для преобразования десятичных чисел в двоичные. Целью изобретения является упрощение преобразователя. Цель достигается тем, что в преобразователь, содержащий входной регистр 1, состоящий из тетрад, группу блоков 2 памяти, первый блок 3 суммирования, введены промежуточный регистр 4 и второй блок 5 суммирования, а входной регистр 1 выполнен сдвиговым. 4 табл., 4 ил.

ного двоичного сумматора или полусумвания, промежуточный регистр, а входПервый такт

1

1100100

10011100010000 00000000000000

101010000011

01

9

--.

XAl XXX XXXXXXXXXXX 0 ft

ххххххо о о о ооооои4

XXX ХХХХХХ ХХХХХХО

Фиг.2

IЯ... g982&2« 2 2пгпгпгю292 2 2 252II2

156999310

Продолжение табл.4

Вбход

О

в о-ч

:

:

9 ut.

| Патент США № 4325056, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Красноголовый Б0Н., Шпилевой Б„Н | |||

| Преобразователи кодов чисел | |||

| - Минск: БГУ, 1983, с | |||

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

| Вычислительные системы и синхронная арифметика.- М.: Радио и связь, 1981, с | |||

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

Авторы

Даты

1990-06-07—Публикация

1988-04-04—Подача