Изобретение относится к вычислительной технике и может быть использовано как средство контроля и отладки цифровых устройств и микропроцессорных систем.

Цель изобретения - повышение достоверности контроля.

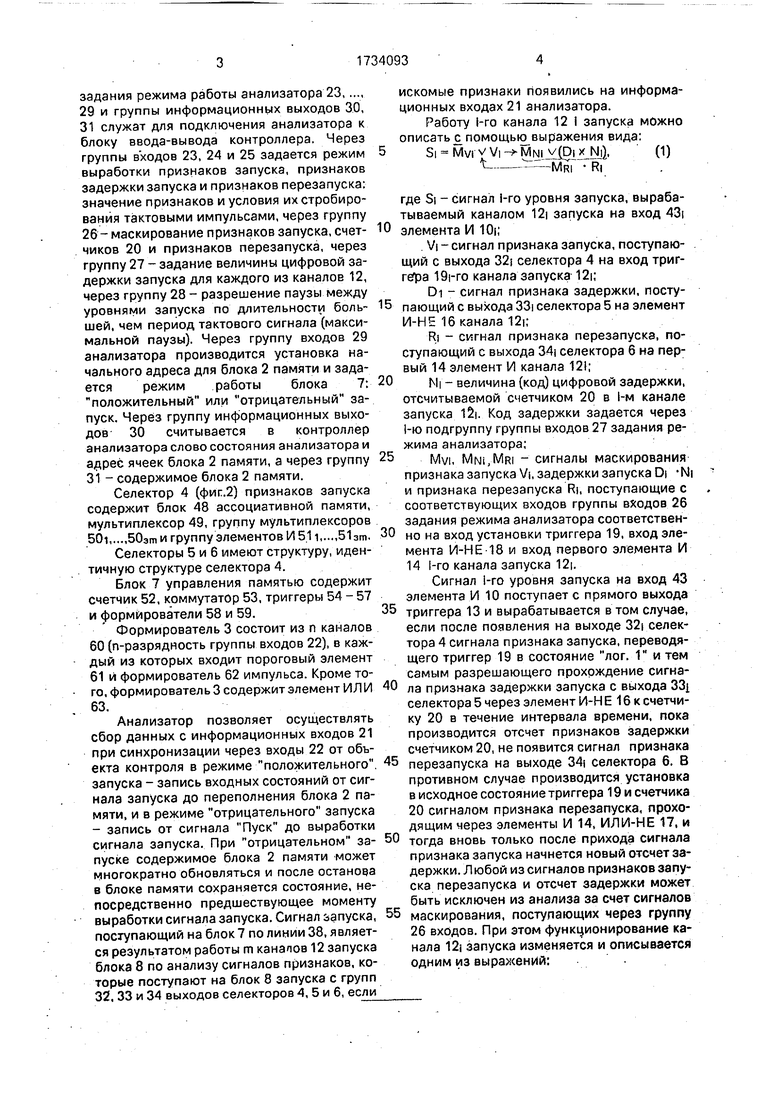

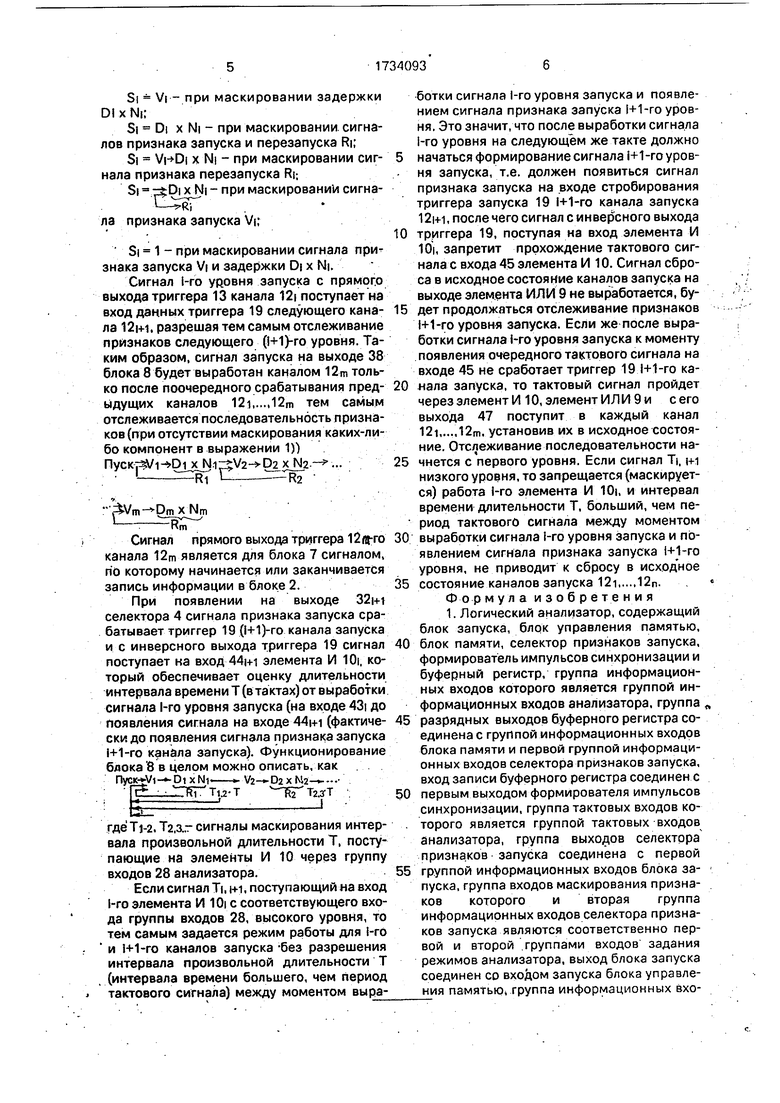

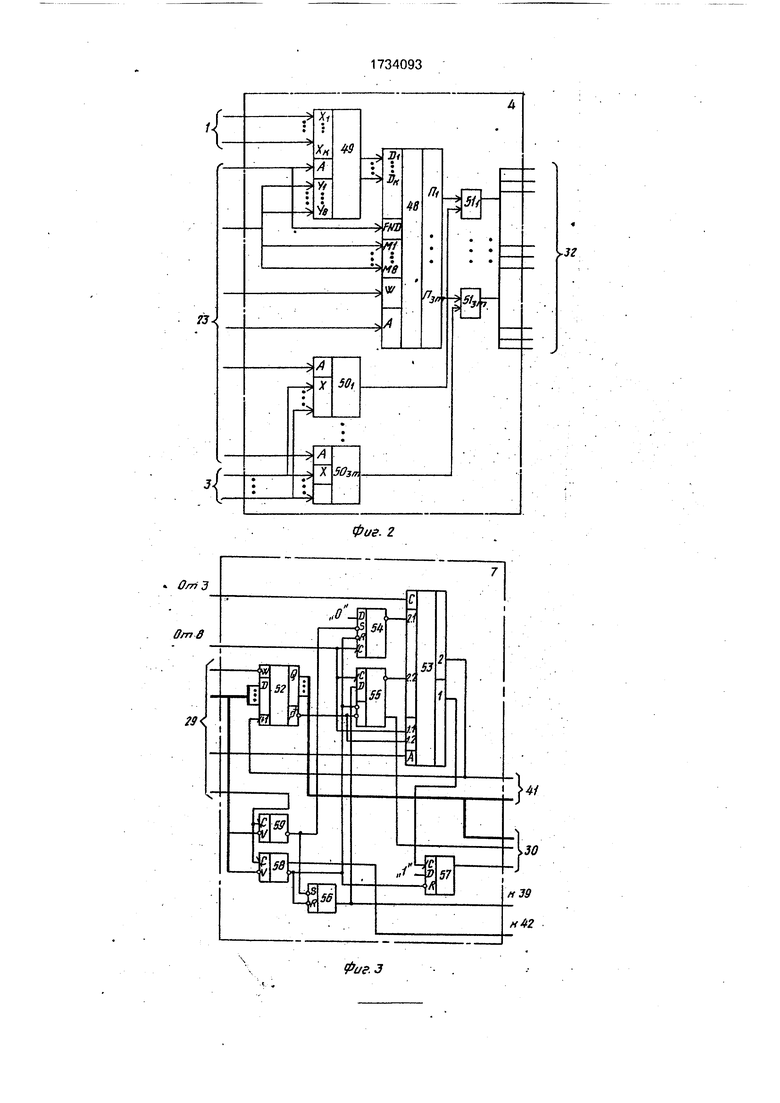

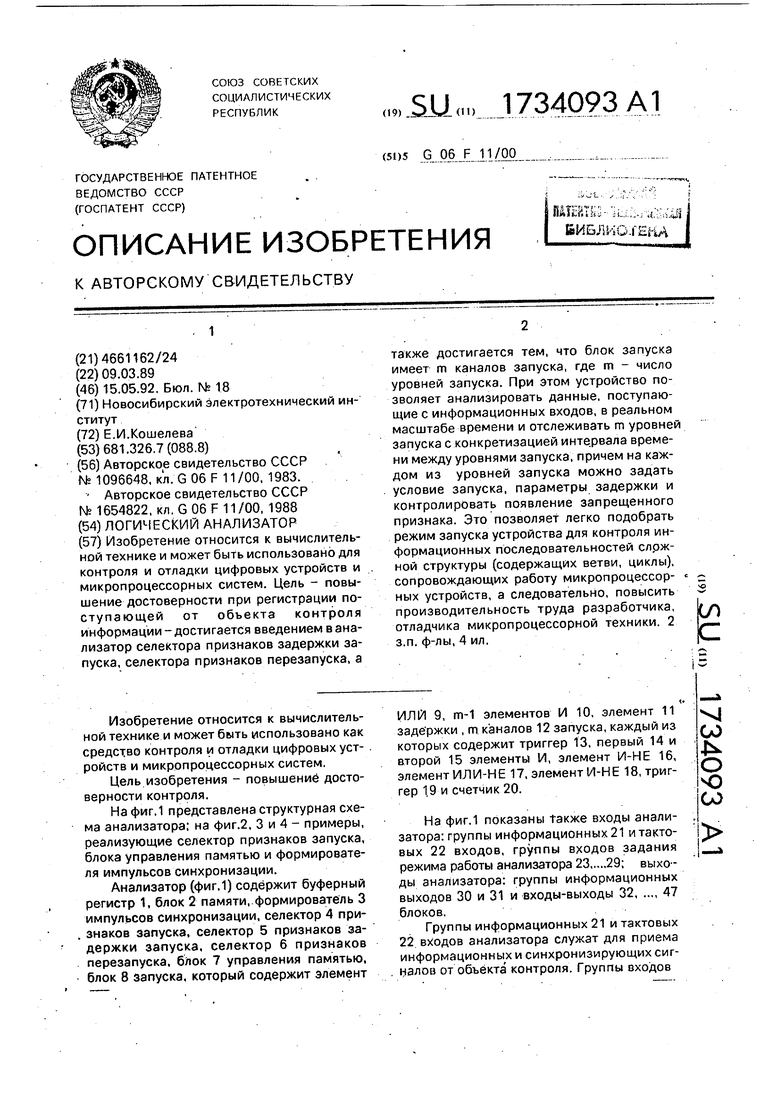

На фиг.1 представлена структурная схема анализатора; на фиг.2, 3 и 4 - примеры, реализующие селектор признаков запуска, блока управления памятью и формирователя импульсов синхронизации.

Анализатор (фиг,1) содержит буферный регистр 1, блок 2 памяти, формирователь 3 импульсов синхронизации, селектор 4 при- . знаков запуска, селектор 5 признаков задержки запуска, селектор 6 признаков перезапуска, блок 7 управления памятью, блок 8 запуска, который содержит элемент

ИЛИ 9, т-1 элементов И 10, элемент 11 задержки , m каналов 12 запуска, каждый из которых содержит триггер 13, первый 14 и второй 15 элементы И, элемент И-НЕ 16, элемент ИЛ И-НЕ 17, элемент И-НЕ 18, триггер 19 и счетчик 20.

На фиг.1 показаны Также входы анализатора: группы информационных 21 и тактовых 22 входов, группы входов задания режима работы анализатора 2329; выходы анализатора: группы информационных выходов 30 и 31 и входы-выходы 32, ..,, 47 блоков.

Группы информационных 21 и тактовых 22 входов анализатора служат для приема информационных и синхронизирующих сигналов от объекта контроля. Группы входов

х|

СО

Јь

о о со

задания режима работы анализатора 23

29 и группы информационных выходов 30, 31 служат для подключения анализатора к блоку ввода-вывода контроллера. Через группы входов 23, 24 и 25 задается режим выработки признаков запуска, признаков задержки запуска и признаков перезапуска: значение признаков и условия ихстробиро- вания тактовыми импульсами, через группу 26 - маскирование признаков запуска, счетчиков 20 и признаков перезапуска, через группу 27 - задание величины цифровой задержки запуска для каждого из каналов 12, через группу 28 - разрешение паузы между уровнями запуска по длительности большей, чем период тактового сигнала (максимальной паузы). Через группу входов 29 анализатора производится установка начального адреса для блока 2 памяти и задается режим работы блока 7: положительный или отрицательный запуск. Через группу информационных выходов 30 считывается в контроллер анализатора слово состояния анализатора и адрес ячеек блока 2 памяти, а через группу 31 - содержимое блока 2 памяти.

Селектор 4 (фиг.2) признаков запуска содержит блок 48 ассоциативной памяти, мультиплексор 49, группу мультиплексоров 50i50зт и группу элементов И 511,...,51зт.

Селекторы 5 и 6 имеют структуру, идентичную структуре селектора 4.

Блок 7 управления памятью содержит счетчик 52, коммутатор 53, триггеры 54 - 57 и формирователи 58 и 59.

Формирователь 3 состоит из п каналов

60(n-разрядность группы входов 22), в каждый из которых входит пороговый элемент

61и формирователь 62 импульса. Кроме того, формирователь 3 содержит элемент ИЛИ 63.

Анализатор позволяет осуществлять сбор данных с информационных входов 21 при синхронизации через входы 22 от объекта контроля в режиме положительного запуска - запись входных состояний от сигнала запуска до переполнения блока 2 памяти, и в режиме отрицательного запуска - запись от сигнала Пуск до выработки сигнала запуска. При отрицательном запуске содержимое блока 2 памяти может многократно обновляться и после останова в блоке памяти сохраняется состояние, непосредственно предшествующее моменту выработки сигнала запуска. Сигнал запуска, поступающий на блок 7 по линии 38, является результатом работы m каналов 12 запуска блока 8 по анализу сигналов признаков, которые поступают на блок 8 запуска с групп 32. 33 и 34 выходов селекторов 4, 5 и 6, если

искомые признаки появились на информационных входах 21 анализатора.

Работу i-ro канала 12 i запуска можно описатьЈпомощыр выражения вида:

Si Mvi VV|- MNiYlDi Njl.О)

Ri

t

где Si - сигнал i-го уровня запуска, вырабатываемый каналом 12| запуска на вход 43i

элемента И 10i;

Vi - сигнал признака запуска, поступающий с выхода 32| селектора 4 на вход триггера 19|-го канала запуска 12i;

DI - сигнал признака задержки, постулающий с выхода 33 селектора 5 на элемент И-НЕ 16 канала 12к

Ri - сигнал признака перезапуска, поступающий с выхода 34j селектора 6 на первый 14 элемент VI канала 121;

М| - величина (код) цифровой задержки, отсчитываемой счетчиком 20 в 1-м канале запуска 12|. Код задержки задается через 1-ю подгруппу группы входов 27 задания режима анализатора;

MVI, MNI,MRI - сигналы маскирования признака запуска Vj, задержки запуска DI -Ni и признака перезапуска RI, поступающие с соответствующих входов группы входов 26 задания режима анализатора соответственно на вход установки триггера 19, вход элемента И-НЕ 18 и вход первого элемента И 14 1-го канала запуска 12|.

Сигнал 1-го уровня запуска на вход 43 элемента И 10 поступает с прямого выхода

триггера 13 и вырабатывается в том случае, если после появления на выходе 32| селектора 4 сигнала признака запуска, переводящего триггер 19 в состояние лог. 1 и тем самым разрешающего прохождение сигнала признака задержки запуска с выхода 33| селектора 5 через элемент И-Н Е 16 к счетчику 20 в течение интервала времени, пока производится отсчет признаков задержки счетчиком 20, не появится сигнал признака

перезапуска на выходе 34| селектора 6. В противном случае производится установка в исходное состояние триггера 19 и счетчика 20 сигналом признака перезапуска, проходящим через элементы И 14, ИЛ И-НЕ 17, и

тогда вновь только после прихода сигнала

признака запуска начнется новый отсчет задержки. Любой из сигналов признаков запуска перезапуска и отсчет задержки может быть исключен из анализа за счет сигналов маскирования, поступающих через группу 26 входов. При этом функционирование канала 12j запуска изменяется и описывается одним из выражений:

Si Vi - при маскировании задержки DIxNi;

Si Di x Ni - при маскировании сигналов признака запуска и перезапуска RI;

Si x NI - при маскировании сигнала признака перезапуска RI;

Si - при маскировании сигнаL- кГ

па признака запуска VLSI 1 - при маскировании сигнала признака запуска Vi и задержки DI x NI.

Сигнал 1-го уровня запуска с прямого выхода триггера 13 канала 12| поступает на вход данных триггера 19 следующего канала 12н-1. разрешая тем самым отслеживание признаков следующего (i+1)-ro уровня. Таким образом, сигнал запуска на выходе 38 блока 8 будет выработан каналом 12т только после поочередного срабатывания предыдущих каналов 12i12m тем самым

отслеживается последовательность признаков (при отсутствии маскирования каких-либо компонент в выражении 1)) nycK7Wi- Di x N2 ... :

2

V,

m

Rm

Сигнал прямого выхода триггера 12щто канала 12т является для блока 7 сигналом, по которому начинается или заканчивается запись информации в блоке 2.

При появлении на выходе 32i+t селектора 4 сигнала признака запуска срабатывает триггер 19 (1+1)-го канала запуска и с инверсного выхода триггера 19 сигнал поступает на вход 44i+i элемента И 10i, который обеспечивает оценку длительности интервала времени Т (втактах) от выработки сигнала 1-го уровня запуска (на входе 43i до появления сигнала на входе 44|+1 (фактически до появления сигнала признака запуска i+1-го канала запуска). Функционирование блока 8 в целом можно описать, как nycK- Vi-4-Di x . N2--- -ТЯГТи-Т -fiTTz.

ш

rfleTj-2, Т2,з.,- сигналы маскирования интервала произвольной длительности Т, поступающие на элементы И 10 через группу входов 28 анализатора.

Если сигнал Ti, 1+1, поступающий на вход 1-го элемента И 10i с соответствующего входа группы входов 28, высокого уровня, то тем самым задается режим работы для 1-го и 1+1 -го каналов запуска -без разрешения интервала произвольной длительности Т (интервала времени большего, чем период тактового сигнала) между моментом выработки сигнала 1-го уровня запуска и появлением сигнала признака запуска f+1-ro уровня. Это значит, что после выработки сигнала 1-го уровня на следующем же такте должно начаться формирование сигнала i+1-го уровня запуска, т.е. должен появиться сигнал признака запуска на входе стробирования триггера запуска 19 i+1-го канала запуска 12|-ц, после чего сигнал с инверсного выхода

0 триггера 19, поступая на вход элемента И 10i, запретит прохождение тактового сигнала с входа 45 элемента И 10. Сигнал сброса в исходное состояние каналов запуска на выходе элемента ИЛИ 9 не выработается, бу5 дет продолжаться отслеживание признаков I+1-го уровня запуска. Если же после выработки сигнала 1-го уровня запуска к моменту появления очередного тактового сигнала на входе 45 не сработает триггер 19 l+1-ro ка0 нала запуска, то тактовый сигнал пройдет через элемент И 10, элемент ИЛИ 9 и с его выхода 47 поступит в каждый канал 12i12m. установив их в исходное состояние. Отслеживание последовательности на5 чнется с первого уровня. Если сигнал Ti. 1+1 низкого уровня, то запрещается (маскируется) работа 1-го элемента И 10i, и интервал времени длительности Т, больший, чем пе- риод тактового сигнала между моментом

0 выработки сигнала 1-го уровня запуска и появлением сигнала признака запуска i+1-го уровня, не приводит к сбросу в исходное

5 состояние каналов запуска 12i12П.е

Формула изобретения 1. Логический анализатор, содержащий блок запуска, блок управления памятью,

0 блок памяти, селектор признаков запуска, формирователь импульсов синхронизации и буферный регистр, группа информационных входов которого является группой информационных входов анализатора, группа „

5 разрядных выходов буферного регистра соединена с группой информационных входов блока памяти и первой группой информационных входов селектора признаков запуска, вход записи буферного регистра соединен с

0 первым выходом формирователя импульсов синхронизации, группа тактовых входов которого является группой тактовых входов анализатора, группа выходов селектора признаков запуска соединена с первой

5 группой информационных входов блока запуска, группа входов маскирования признаков которого и вторая группа информационных входов селектора признаков запуска являются соответственно первой и второй группами входов задания режимов анализатора, выход блока запуска соединен со входом запуска блока управления памятью, группа информационных входов которого является третьей группой входов задания режимов анализатора, первая группа выходов блока управления памятью соединена с адресными входами блока памяти, управляющий вход которого подключен к первому выходу блока, управления памятью, группа выходов блока памяти и вторая группа выходов блока управления памятью образуют первую и вторую группы информационных выходов анализатора для считывания зарегистрированной информации и слова состояния анализатора соответственно, отличающийся тем, что, с целью повышения достоверности контроля, в него введены селектор признаков задержки запуска и селектор признаков перезапуска, а блок запуска содержит группу из (т-1) элементов И, элемент ИЛИ, элемент задержки и m каналов запуска (т - число уровней запуска), в каждый из которых входят первый триггер и второй триггер, счетчик, два элемента И, два элемента И-НЕ и элемент ИЛИ-НЕ, причем тактовый вход первого триггера 1-го канала запуска является 1-м входом первой группы информационных входов блока запуска, первые входы первых элементов И-НЕ m каналов запуска образуют вторую группу информационных входов блока запуска и подключены к группе выходов селектора признаков задержки запуска, первые входы первых элементов И m каналов запуска образуют третью группу информационных входов блока запуска и подключены к группе выходов селектора признаков перезапуска, вторые входы первый элементов И, первые входы вторых элементов И-НЕ-и установочные входы первых триггеров m каналов запуска образуют группу входов маскирования признаков блока запуска, информационный вход первого триггера первого канала запуска является входом разрешения блока запуска и подключен ко второму выходу блока управления памятью, тактовый вход которого и вход элемента задержки подключены к первому выходу формирователя импульсов синхронизации, выход элемента задержки соединен с первыми входами элементов И группы, выходы которых и третий выход блока управления памятью соединены со входами элемента ИЛИ, выход которого соединен с первыми входами элементов ИЛИ-НЕ m каналов запуска, прямой выход второго триггера 1-го канала запуска (J 1, т- - 1) соединен с информационным входом первого триггера, с первым входом второго элемента И, со вторым входом первого элемента И-НЕ (j+1)-ro канала запуска и со вторым входом j-ro элемента И группы, выход первого триггера (j+1)-ro канала запуска соединен с третьим входом j-ro элемента И группы, прямой выход второго триггера т- го канала запуска является выходом блока запуска, первые группы информационных

входов селектора признаков задержки запуска и селектора признаков перезапуска соответственно подключены к разрядным выходам буферного регистра, вторые группы информационных входов селектора при0 знаков задержки запуска и селекторов признаков перезапуска являются соответственно четвертой и пятой группами входов задания режимов анализатора, соответственно объединенные тактовые входы селек5 тора . признаков запуска, селектора признаков задержки запуска и селектора признаков перезапуска подключены к группе выходов формирователя импульсов синхронизации, входы данных счетчиков

0 являются входами задания задержки запуска блока запуска и образуют шестую группу входов задания режимов анализатора, четвертые входы элементов И группы являются входами разрешения максимальной

5 задержки запуска блока запуска и образуют восьмую группу входов задания режимов анализатора, в каждом Г-м канале запуска блока запуска выход первого элемента И соединен с вторым входом элемента ИЛИ0 НЕ, выход которого соединен с входом установки счетчика и входами сброса второго триггера и первого триггера, прямой выход которого соединен с вторым входом второго элемента И с третьим входом первого эле5 мента И-НЕ, выход которого соединен со счетным входом счетчика, выход переполнения которого соединен с вторым входом второго элемента Й-НЕ, выход которого соединен с третьим входом второго элемен0 та И, выход которого соединен с установочным входом второго триггера, инверсный выход которого соединен с третьим входом первого элемента И.

2. Анализатор по п.1, о т л и ч а.ю щи й5 ся тем, что блок управления памятью содержит счетчик, коммутатор, четыре триггера и два формирователя импульсов, причем инверсный выход первого формирователя импульсов соединен с инверсными входами

0 сброса первого, второго, третьего и четвертого триггеров, инверсный выход второго формирователя импульсов соединен с инверсными установочными входами первого и третьего триггеров, информационный

5 вход первого триггера подключен к шине логического нуля, инверсные выходы первого и второго триггеров соединены с первой группой информационных входов коммутатора, первый выход которого соединен со счетным входом счетчика и является первым

выходом блока, тактовые входы первого и второго триггеров и первый вход второй группы информационных входов коммутатора объединены и образуют вход запуска блока, инверсный выход переполнения счетчика соединен с вторым инверсным входом сброса второго триггера и с вторым входом второй группы информационных входов коммутатора, второй выход которого соединен с тактовым входом четвертого триггера, информационный вход которого подключен к шине логической единицы, тактовый вход коммутатора является тактовым входом блока, вход разрешения и группа информационных входов счетчика, управля- ющий вход коммутатора, входы разрешения и объединенные тактовые входы первого и второго формирователей импульсов образуют группу информационных входов блока, группа разрядных выходов счетчика являет- ся первой группой выходов блока, прямой выход второго триггера, группа разрядных выходов счетчика и выход четвертого триггера образуют вторую группу выходов блока, выход третьего триггера, соединенный с информационным входом второго триггера, и прямой выход первого формирователя импульсов являются соответственно вторым и третьим выходами блока,

3. Анализатор по п.1, отличающий с я тем, что селектор признаков запуска содержит блок ассоциативной памяти, мультиплексор, группу из m мультиплексоров и группу из m элементов И, причем первая группа информационных входов мультиплексора образует первую группу информационных входов селектора, соответственно объединенные информационные входы мультиплексоров группы образуют группу тактовых входов селектора, группы адресных входов, входов маскирования и входов записи, блока ассоциативной памяти, вторая группа информационных входов и адресный вход мультиплексора.соединенный с входом разрешения блока ассоциативной памяти, образуют вторую группу информационных входов селектора, группа выходов мультиплексора соединена с группой информационных входов блока ассоциативной памяти, выходы которого соединены с первыми входами элементов И группы, вторые входы которых подключены соответственно к выходам мультиплексоров группы, выходы элементов И группы образуют группу выходов селектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Многофункциональное устройство для логической обработки бинарных изображений | 1983 |

|

SU1136179A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| Устройство для обмена данными | 1989 |

|

SU1700562A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и отладки цифровых устройств и микропроцессорных систем. Цель - повышение достоверности при регистрации поступающей от объекта контроля информации - достигается введением в анализатор селектора признаков задержки запуска, селектора признаков перезапуска, а также достигается тем, что блок запуска имеет m каналов запуска, где m - число уровней запуска. При этом устройство позволяет анализировать данные, поступающие с информационных входов, в реальном масштабе времени и отслеживать m уровней запуска с конкретизацией интервала времени между уровнями запуска, причем на каждом из уровней запуска можно задать условие запуска, параметры задержки и контролировать появление запрещенного признака. Это позволяет легко подобрать режим запуска устройства для контроля информационных последовательностей слрж- ной структуры (содержащих ветви, циклы), сопровождающих работу микропроцессор- « ных устройств, а следовательно, повысить производительность труда разработчика, отладчика микропроцессорной техники. 2 з.п. ф-лы, 4 ил. (Л С

2в

29 30 Л

фиг 4

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

Авторы

Даты

1992-05-15—Публикация

1989-03-09—Подача