Изобретение относится к вычислительной технике, в частности устройствам умножения, и может быть использовано при построении арифметических устройств электронных вычислительных машин.

Цель изобретения - расширение функциональных возможностей за счет выполнения операции умножения при вводе n-разрядного множимого и п-раз- рядного множителя с произвольных 1-х разрядов (i 1,2,...,п).

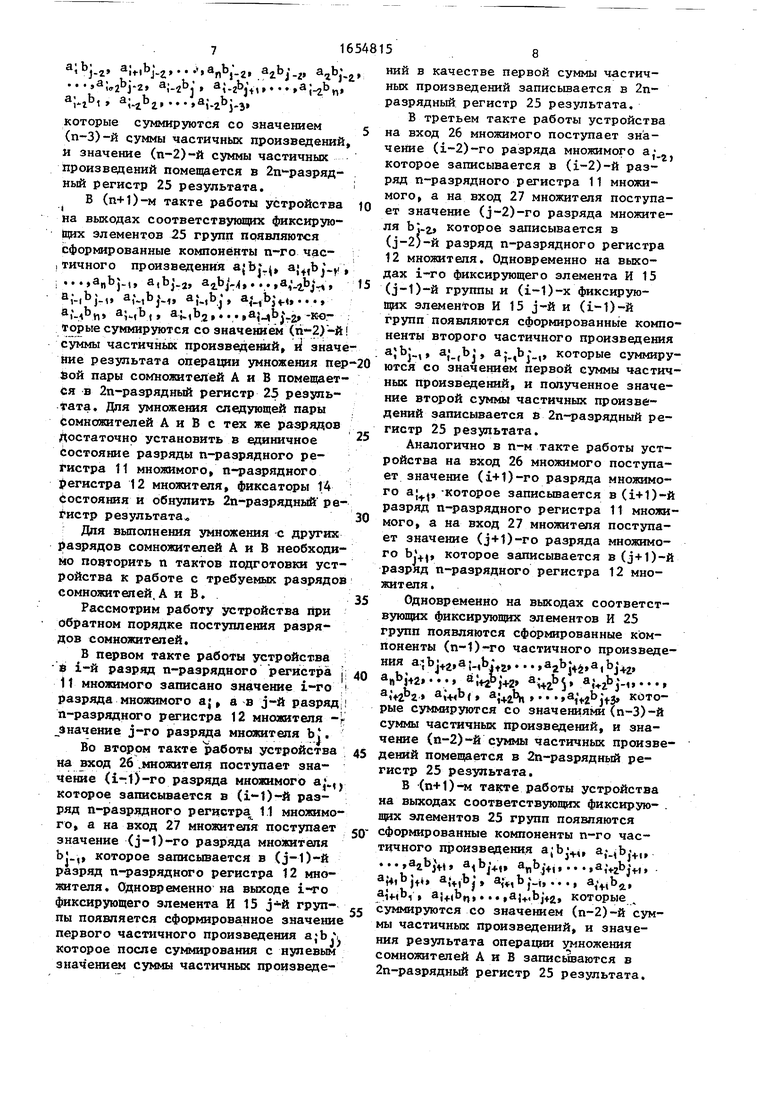

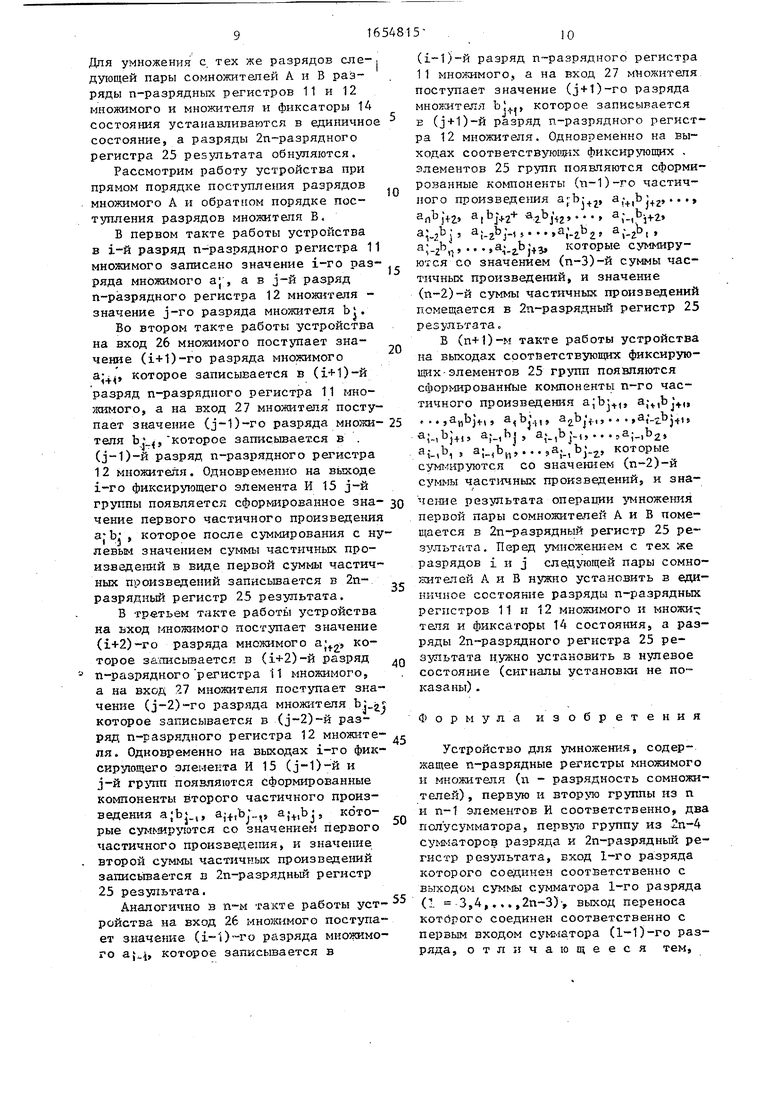

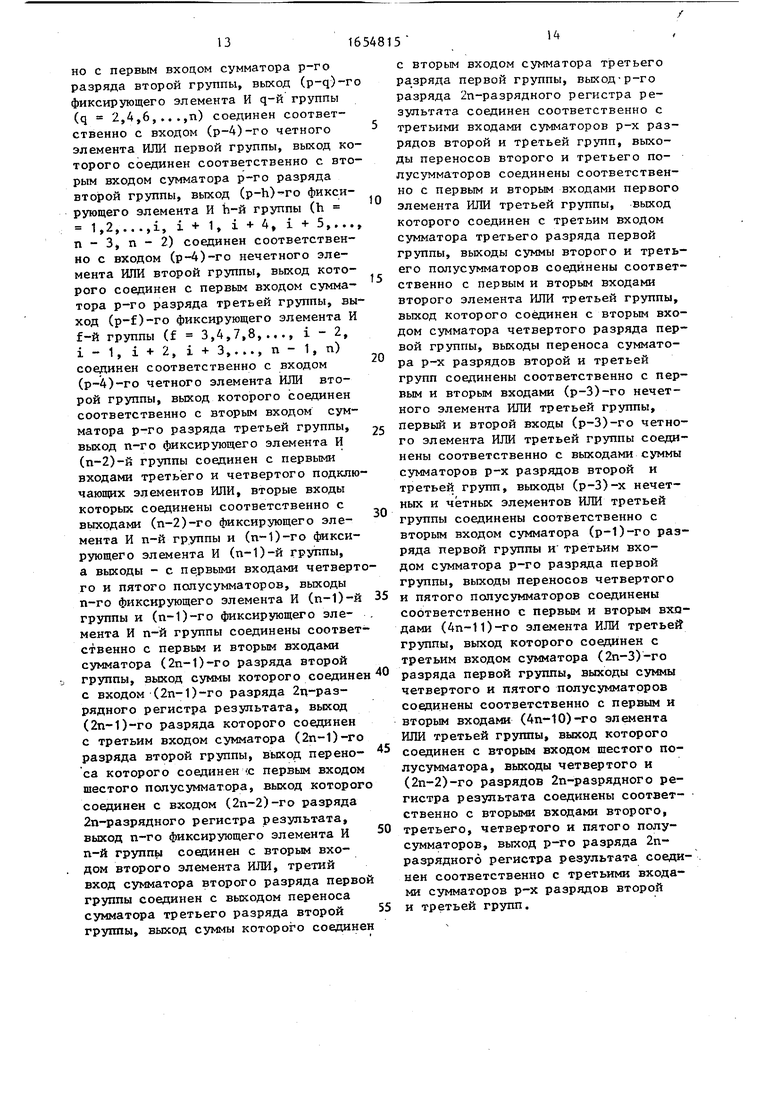

На чертеже изображена схема устройства.

Устройство для умножения содержит два элемента 1 и 2 запрета, первый

n-разрядный кольцевой реверсивный регистр 3, фиксатор 4 множимого, второй кольцевой реверсивньй регистр 5, фиксатор 6 множителя, два элемента И 7 и 8, две группы из п элементов И 9 и 10, n-разрядный регистр 11 множимого, n-разрядный регистр 12 множителя, п групп из п формирующих элементов И 13, п групп из п фиксаторов 14 состояния, п групп из п фиксирующих элементов И 15, первую группу элементов ИЛИ 16, четыре подключающих элемента ИЛИ 17.1-17.4, вторую группу элементов ИЛИ 18, шесть полусумматоров 19.1-19,6, вторую группу из 2п-5 сумматоров 20 разряда,

о ел

4ь 00

СП

третью группу из 2п-7 сумматоров 21 разряда, два элемента ИЛИ 22.1 и 22.2, третью группу элементов ИЛИ 23, первую группу из 2п-4 сумматоров 24 разряда, 2п-разрядный регистр 25 результата, входы множимого 26 и множителя 27 устройства.

Фиксаторы 4 и 6 множимого и множителя, фиксаторы 14 состояния, разря- ды n-разрядных кольцевых реверсивных регистров 1 и 2, n-разрядных регистров 11 и 12 множимого и множителя, 2п-разрядного регистра 25 результата построены на двойных триггерах (RS или IK).

В исходном состоянии п-разрядные кольцевые реверсивные регистры 3 иг 5 и 2п-разрядный регистр 25 результата обнулены. Фиксатор 4 множимого, фик- сатор 6 множителя, разряды п-разряд- ного регистра 11 множимого, разряды п разрядного регистра 12 множителя и фиксаторы 14 состояния установлены в единичное состояние.

Допустим, что множимое и множитель В соответственно равны:

А - fa,aJ,a,(,...,a;atV,...,an.1art

В b,bz,...bjbj4, .....Ь.Ь.

Если разряды сомножителя А или В поступают в прямом порядке, т.е.

}.atai-M a2alan a -4а -f

--- .

bjbjV, , ...Ьц,. . ., сдвиг в соответствующих п-разрядных кольцевых регистрах 3 или 5 выполняется от старших к младшим разрядам этих регистров.

Если разряды сомножителя А или В поступают в обратном порядке, т.е.

а;а| ч « a2aiaft a;+za H

bjbjM,..o, b2b,bn,...,b1-nbjV, ,

в соответствующих n-разрядных кольцевых реверсивных регистрах 3 или 5 сдвиг выполняется от младших к стар шим разрядам этих регистров.

Подготовка устройства к работе длится п тактов, на (п+1)-м такте начинается обработка разрядов сомножителей, также поступающих через входы 26 и 27 множимого и множителя, т.е. (п+1)-й такт является первым тактом работы устройства.

Так как в исходном состоянии фиксаторы 4 и 6 множимого и множителя

0

С

0

5

0 5

находятся в единичном состоянии, то снимаемые с их инверсных выходов нулевые значения разрешают прохожде-, ние информации через первый 1 и второй 2 элементы запрета и блокируют ее прохождение через первый 7 и второй 8 элементы И.

При подготовке устройства к работе единичный сигнал в i-м разряде кода записывается в n-й разряд первого n-разрядного кольцевого реверсивного регистра 1 и сбрасывает О в фиксатор 4 множимого.

В результате единичный сигнал с инверсного выхода фиксатора 4 множимого блокирует первый элемент 1 запрета и разрешает прохождение информации через первый элемент И 7. Так как код имеет одно единичное значение, то поступление остальных нулевых разрядов кода до сдвига его единичного значения в i-й разряд первого n-разрядного кольцевого реверсивного регистра 1 не оказывает влияния на разряды п-разрядного регистра 11 множимого. Такую же функцию, но для множителя, выполняют второй элемент 2 запрета, второй элемент И 8 и фиксатор 6 множителя, который сбрасывается в нулевое состояние, когда единичный сигнал в j-м разряде кода записывается в n-й разряд второго п-раз- рядного кольцевого реверсивного регистра 2. Таким образом, и управляющая информация, и разряды сомножителей поступают в устройство через одни и те же входы 26 и 27 множимо- - го и множителя.

Запись единичной информации в разряд n-разрядного регистра 11 множимого или в разряд n-разрядного pe-f гистра 12 множителя производится через вход установки в О данного разряда . В результате записанная информация фиксируется в данном разряде и снимается с инверсного выхода разряда, поддерживаясь на протяжении всего времени выполнения операции умножения над данной парой множимого А и множителя В,

Работа формирующих элементов И 13, фиксаторов 14 состояния и фиксирующих элементов И 15 заключается в формировании и одноразовом использовании для суммирования соответствующей данному формирующему элементу И 13 компоненты частичного произведения. Последующий сброс в О соответствующего

51

фиксатора 14 состояния после завершения суммирования сформированной - единичной компоненты частичного произведения блокирует фиксирующий элемент И 15, исключая его повторное суммирование. При этом не требуется сдвигов формируемых сумм частичных произведений.

Суммирование частичных произведений выполняется полусумматорами 19 сумматорами 20, 21 и 24 разрядов при помощи элементов ИЛИ 17, 18 и 23 первой, второй и третьей групп, четырех подключающих элементов ИЛИ 17 и первого и второго элементов ИЛИ 22.

При умножении с произвольных разрядов сомножителей в одном такте образуется не более двух частичных произведений с одним весом разрядов. Первая группа элементов ИЛИ 17, 2п-5 сумматоров 20 разрядов и вторая группа элементов ИЛИ 18, 2п-7 сумматоров 21 разрядов исключают соответственно потерю разряда с единичным значением при одновременном формировании двух частичных произведений с одним весом разрядов формирующими элементами И 13 соседних групп или формирующими элементами И 13 несоседних групп. Обе возможные ситуации объединяются третьей группой элементов ИЛИ 23 и сумматорами 24 разрядов. После выполнения умножения над парой сомножителей А и В результат операции умножения находится в 2п-разрядном регис ре 25 результата. Если умножение следующей пары сомножителей А и В выполняется с тех же разрядов i и j сомножителей, то перед поступлением разрядов сомножителей разряды п-раз- рядных регистров 11 и 12 множимого и множителя и фиксаторы 14 состояния устанавливаются в единичное состояние, а разряды 2п-разрядного регистр 25 результата обнуляются (сигналы установки не показаны).

Если умножение следующей пары множимого А и множителя В необходимо выполнить с других разрядов i j,

то необходимо повторить п тактов подготовки устройства к работе требуемых разрядов.

Рассмотрим работу устройства при прямом порядке поступления разрядов сомножит ел ей.

В первом такте работы устройства на вход 26 множимого поступает значение 1-го разряда множимого а;, ко

0

5

8

5

0 5

0

0

0

5

15 ,6

торое записывается в i-й разряд n-разрядного регистра 11 множимого. Одновременно на вход 27 множителя поступает значение j-ro разряда множителя bj, которое записывается в j-й разряд n-разрядного регистра 12 множит еля.

Во втором такте работы устройства на вход 26 множимого поступает значение (i-H)-ro разряда множимого а-+(, которое записывается в (п-И)-й разряд n-разрядного регистра 11 множимого, а на вход 27 множителя поступает значение (j-1)-ro разряда множителя, которое записывается в (j + D-й разряд n-разрядного регистра 12 множителя. На выходе 1-го фиксирующего элемента И 15 j-й группы появляется значение первого частичного произведения которое суммируется с нулевым значением суммы частичных произведений, и значение первой суммы частичных произведений помещается в 2п-разряд- ный регистр 25 результата.

В третьем такте работы устройства на вход 26 множимого поступает значение (i+2)-ro разряда множимого a;t2) которое записывается в (1+2)-й разряд n-разрядного. регистра 11 множимого, а на вход 27 множителя поступает значение (j+2)-ro разряда множителя, которое записывается в (j+2)-u разряд n-разрядного регистра 12 множителя . Одновременно на выходах 1-го фиксирующего элемента И 15 (j+1)-и группы и (i+1)-x фиксирующих элементов И 15 j-й и (j + D-й групп появляются сформированные компоненты второго частичного произведения ajb;+i, a;4)b:, и,, которые суммируются со значением первого частичного произведения, и значение второй суммы частичных произведений помещается в 2п-разрядный регистр 25 результата.

Аналогично в n-м такте работы устройства на вход 26 множимого поступает значение (i-l)-ro разряда множимого а;,, которое записывается в (1-1)-й разряд n-разрядного регистра 11 множимого, а на вход 27 множителя поступает.значение (j-1)-ro разряда множителя Ь., которое записывается в (j-l)-fi разряд n-разрядного регистра 12 множителя. Одновременно на выходах соответствующих фиксирующих элементов И 25 групп появляются сформированные компоненты (п-1)-го частичного произведения

a;bj-z a «bj-j anbi-2

a r2bj-2 a, -2bj , at-Zbj41

a2bJ-Z«

arzbi

а;Л.

at-zbj-3

,

аЛ.г,

n

которые суммируются со значением (п-З)-й суммы частичных произведений, и значение (п-2)-й суммы частичных произведений помещается в 2тг-раэряд- ный регистр 25 результата.

В (п+1)-м такте работы устройства на выходах соответствующих фиксирующих элементов 25 групп появляются сформированные компоненты n-го частичного произведения ajbj., .y ,

anbj-i, atbj-a

ai-ibj

a,-ibi-i а, а},Ь, а,Ь И,

ai -ibn aiMbt a -ib2aJ- bf-2 -которые суммируются со значением ()-й суммы частичных произведений и1 значеВ третьем такте работы устройства на вход 26 множимого поступает значение (i-2)-ro разряда множимого ) которое записывается в (х-2)-й разряд n-разрядного регистра 11 множимого, а на вход 27 множителя поступает значение (j-2)-ro разряда множителя bt.Ј, которое записывается в (j-2;-ft разряд n-разрядного регистра 12 множителя. Одновременно на выходах 1-го фиксирующего элемента И 15 (j-D-й группы и (i-1)-x фиксирующих элементов И 15 j-й и (1-1)-й групп появляются сформированные компоненты второго частичного произведения a;bj,, a;,bj, а,-.,Ь, которые суммируНие результата операции умножения пер-20 ются со значением первой суммы частичной пары сомножителей А и В помещается в 2п-разрядный регистр 25 реэуль- тата. Для умножения следующей пары Сомножителей А и В с тех же разрядов Достаточно установить в единичное состояние разряды n-разрядного регистра 11 множимого п-разрядного регистра 12 множителя, фиксаторы 14 Состояния и обнулить 2п-разрядныЙ регистр результата,

Для выполнения умножения с других разрядов сомножителей А и В необходимо повторить п тактов подготовки устройства к работе с требуемых разрядов Сомножителей. А и В.

Рассмотрим работу устройства при обратном порядке поступления разрядов сомножителей.

В первом такте работы устройства в 1-й разряд n-разрядного регистра , 11 множимого записано значение 1-го разряда множимого а{, а в j-й разряд n-разрядного регистра 12 множителя -г значение j-ro разряда множителя bj.

Во втором такте работы устройства на вход 26.множителя поступает значение (i-l)-ro разряда множимого а,} которое записывается в (1-1)-й разряд п-разрлдного регистра 11 множимого, а на вход 27 множителя поступает значение (j-0-го разряда множителя Ь|,, которое записывается в (j-l)-ft разряд n-разрядного регистра 12 множителя. Одновременно на выходе 1-го

25

30

35

40

ных произведений, и полученное значение второй суммы частичных произведений записывается в 2п-раэрядный регистр 25 результата.

Аналогично в n-м такте работы устройства на вход 26 множимого поступает значение (i-H)-ro разряда множимого а;, -которое записывается в(1+1)-й разряд n-разрядного регистра 11 множимого, а на вход 27 множителя поступает значение (j+0-го разряда множимого b. +j, которое записывается в (j-H)-ft разряд n-разрядного регистра 12 множителя.

Одновременно на выходах соответствующих фиксирующих элементов И 25 групп появляются сформированные компоненты (п-1)-го частичного произведения a-,bj+2,a ;.,b;ty..., a2b,a

1 bj+2

а„Ь,2,..., а;, ангЬ5 aiVtbj-i 3iV2bjt3 которые суммируются со значениями (п-З)-й суммы частичных произведений, и значение (п-2)-й суммы частичных произве- 45 дений помещается в 2п-разрядный регистр 25 результата.

В (п+1)-м такте работы устройства на выходах соответствующих фиксирующих элементов 25 групп появляются сформированные компоненты n-го частичного произведения а;Ь,,

50

...,aabjftt,

anbj +«

a.4ibj a,4,b, ai«bi aj4.,bn,. ..paj.bj+a, которые

a.4ibj a,4,b, ai«bi aj4.,bn,. ..paj.bj+a, которые

фиксирующего элемента И 15 труп- 55 суммируются со значением (п-2)-й сумпы появляется сформированное значение первого частичного произведения а;Ь.. которое после суммирования с нулевым значением суммы частичных произведемы частичных произведений, и значения результата операции умножения сомножителей А и В записываются в 2п-разрядный регистр 25 результата.

S

ний в качестве первой суммы частичных произведений записывается в 2п- разрядный регистр 25 результата.

В третьем такте работы устройства на вход 26 множимого поступает значение (i-2)-ro разряда множимого ) которое записывается в (х-2)-й разряд n-разрядного регистра 11 множимого, а на вход 27 множителя поступает значение (j-2)-ro разряда множителя bt.Ј, которое записывается в (j-2;-ft разряд n-разрядного регистра 12 множителя. Одновременно на выходах 1-го фиксирующего элемента И 15 (j-D-й группы и (i-1)-x фиксирующих элементов И 15 j-й и (1-1)-й групп появляются сформированные компоненты второго частичного произведения a;bj,, a;,bj, а,-.,Ь, которые суммиру0 ются со значением первой суммы частич5

0

5

ных произведений, и полученное значение второй суммы частичных произведений записывается в 2п-раэрядный регистр 25 результата.

Аналогично в n-м такте работы устройства на вход 26 множимого поступает значение (i-H)-ro разряда множимого а;, -которое записывается в(1+1)-й разряд n-разрядного регистра 11 множимого, а на вход 27 множителя поступает значение (j+0-го разряда множимого b. +j, которое записывается в (j-H)-ft разряд n-разрядного регистра 12 множителя.

Одновременно на выходах соответствующих фиксирующих элементов И 25 групп появляются сформированные компоненты (п-1)-го частичного произведе

ния a-,bj+2,a ;.,b;ty..., a2b,a

1 bj+2

а„Ь,2,..., а;, ангЬ5 aiVtbj-i 3iV2bjt3 которые суммируются со значениями (п-З)-й суммы частичных произведений, и значение (п-2)-й суммы частичных произве- дений помещается в 2п-разрядный регистр 25 результата.

В (п+1)-м такте работы устройства на выходах соответствующих фиксирующих элементов 25 групп появляются сформированные компоненты n-го частичного произведения а;Ь,,

...,aabjftt,

anbj +«

a.4ibj a,4,b, ai«bi aj4.,bn,. ..paj.bj+a, которые

суммируются со значением (п-2)-й суммы частичных произведений, и значения результата операции умножения сомножителей А и В записываются в 2п-разрядный регистр 25 результата.

Для умножения с тех же разрядов еле-, дующей пары сомножителей А и В разряды n-разрядных регистров 11 и 12 множимого и множителя и фиксаторы 14 состояния устанавливаются в единичное состояние, а разряды 2п-разрядного регистра 25 результата обнуляются.

Рассмотрим работу устройства при прямом порядке поступления разрядов множимого А и обратном порядке поступления разрядов множителя В.

В первом такте работы устройства в i-й разряд n-разрядного регистра 11 множимого записано значение 1-го разряда множимого а; , а в j-й разряд n-разрядного регистра 12 множителя - значение j-ro разряда множителя Ь .

Во втором такте работы устройства на вход 26 множимого поступает значение (i+1)-ro разряда множимого а-., которое записывается в (1-Н)-й

разряд n-разрядного регистра 11 множимого, а на вход 27 множителя поступает значение (j-1)-ro разряда множителя Ь , которое записывается в . (j-O-й разряд n-разряцного регистра 12 множителя. Одновременно на выходе 1-го фиксирующего элемента И 15 j-й группы появляется сформированное значение первого частичного произведения aj b- , которое после суммирования с нулевым значением суммы частичных произведений в виде первой суммы частичных произведений записывается в 2п- разрядный регистр 25 результата.

В третьем такте работы устройства на ьход множимого поступает значение (i+2)-ro разряда множимого ajtj, которое записывается в (1+2)-и разряд

n-разрядного регистра 11 множимого, а на вход 27 множителя поступает значение (j-2)-ro разряда множителя которое записывается в ()-& разряд n-разрядного регистра 12 множителя. Одновременно на выходах 1-го фиксирующего элемента И 15 (j-0-й и j-й групп появляются сформированные компоненты второго частичного произведения а;Ь,, а,, a-+)bj, которые суммируются со значением первого частичного произведения, и значение

второй суммы частичных произведений записывается в 2п-разрядный регистр 25 результата.

Аналогично в n-м такте работы устройства на вход 26 множимого поступает значение (1-м)го разряда множимого а{, которое записывается в

0

5

0

5

0

5

0

5

0

5

(1-1)-й разряд п разрядного регистра 1 1 мнохснмого, а на вход 27 множителя поступает значение (j + 1)-ro разряда мнолмтеля bL,, которое записывается Е (j+D-й разряд г-разрядного регистра 12 множителя. Одновременно на выходах соответствующих фиксирующих . элементов 25 групп появляются сформированные компоненты (ti-1)-ro частичного произведения , a,-+,b j+z,.. .,

алъ )Чг а а -ibj-t-2

а -2ЪI ai -abj-iа« -гъг а.-гьt

ai-2hri ai-ibj+3 которые суммируются со значением (п-З)-й суммы частичных произведений, и значение (п-2)-й суммы частичных произведений помещается в 2п-разрядный регистр 25 результата

В (п+1)-м такте работы устройства на выходах соответствующих фиксирующих элементов 25 групп появляются сформированн ые компоненты п-го частичного произведения ajb:,, a,4ibi4« ..,, .ju a2. -)ji и a -t°j-Hs a;.,b}+i, a;-,bj

ai-,bi

2

a,4.,bj -, .. .5a;,b ,,;...,., которые

суммируются со значением (п-2)-й суммы частичных произведений} и значение результата операции умножения первой пары сомножителей А и В помещается в 2п-разрядный регистр 25 результата. Перед умножением с тех же разрядов i и j следующей пары сомно- нителей А и В нужно установить в единичное состояние разряды п-разрядных регистров 11 и 12 множимого и множих теля и фиксаторы 14 состояния, а разряды 2п-разрядного регистра 25 результата нужно установить в нулевое состояние (сигналы установки не показаны) .

Формула изобретения

Устройство для умножения, содержащее n-разрядные регистры множимого и множителя (и - разрядность сомножителей) , первую и вторую группы из п и п-1 элементов И соответственно, два полусумматора, первую группу из 2п-4 сумматоров разряда и 2п-разрядный регистр результата, вход 1-го разряда которого соединен соответственно с выходом суммы сумматора 1-го разряда (- 3,4,...,2п-3) выход переноса котброго соединен соответственно с первым входом сумматора (1-1)-го разряда, отличающееся тем,

что, с целью расширения функциональных возможностей за счет выполнения операции умножения при вводе п-раз- рядного множимого и n-разрядного множителя с произвольных 1-х разрядов 5 (i 1,...,п), введены два п-разряд- ных кольцевых реверсивных регистра„ два элемента запрета, фиксаторы множимого и множителя, два элемента И, один элемент И в вторую группу элемен-О тов И, п групп из п формирующих элементов И, п групп из п фиксаторов состояния, п групп из п фиксирующих элементов И, п групп из п фиксаторов состояния, три группы из 4n-14, 4n-14 J5 и 4п-10 элементов ИЛИ, соответственно,,

2Q

четыре подключающих элемента ИЛИ-) -четыре полусумматора, вторую и третью группы из 2п-5 и 2п-7 сумматоров разряда соответственно и два элемента ИЛИ, выходы которых соединены соответственно с входами первого и 2п-го разрядов 2п-разрядного регистра результата, выходы которых соединены с первыми входами соответственно первого и второго элементов ИЛИ, вход множимого устройства соединен с прямым входом первого элемента запрета и первым входом первого элемента И, вто рой вход которого соединен с инверсным выходом фиксатора множимого и инверсным входом первого элемента запрета, выход которого соединен с входом установки в О фиксатора множимого и входом n-го разряда/первого n-разрядного кольцевого реверсивного регистра, выход 1-го разряда которого соединен соответственно с первым входом 1-го элемента И первой группы, выход первого элемента И соединен с объединенными вторыми входами элементов И первой группы, выходы которых соединены с входами установки в О соответствующих разрядов п-разряд- иого регистра множимого, вход множителя устройства соединен с прямым входом второго элемента запрета и первым входом второго элемента И выход которого соединен с .первым входом 1-го элемента И второй группы,; выход которого соединен с входом установки в О соответственно 1-го разряда n-разрядного регистра множителя, а второй вход - с выходом 1-го разряда второго кольцевого реверсивного регистра, вход n-го разряда которого соединен с выходом второго элемента запрета и выходом установки в О Фиксатора множителяs инверс

5 О 5

5

0

35

0 i 0

ный выход которого соединен с,инверсным входом второго элемента запрета и вторым входом второго элемента И, инверсный выход 1-го разряда п-раз- рядного регистра множимого соединен соответственно с первым входом 1-го фиксирующего элемента И j-й группы (j 1,2,...,п), вторые входы 1-х формирующих элементов И в каждой группе объединены и соединены соответственно с инверсным выходом 1-го разряда n-разрядного регистра множителя, выход 1-го формирующего элемента И j-й группы соединен соответственно с первым входом i-ro фиксирующего элемента И j-й группы и входом установки в О i-ro фиксатора состояния j-й группы, прямой выход которого соединен соответственно с вторым входом 1-го фиксирующего элемента И j-й группы, выход первого фиксирующего элемента И первой группы соединен со первым входом первого полусумматора, второй вход которого соединен с выходом второго разряда 2п-разрядного регистра результата, вход второго разряда которого соединен с выходом суммы сумматора второго разряда первой группы, выход переноса которо - го соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом переноса первого полусумматора, выход суммы которого соединен с вторым входом сумматора второго разряда первой группы, выходы второго фиксирующего элемента И первой группы и второго фиксирующего элемента И второй группы соединены соответственно с первым и вторым входами сумматора третьего разряда второй группы, третий вход которого соединен с выходом третьего разряда 2п-разрядного результата выход третьего фиксирующего элемента И первой группы соединен с первыми входа- ми первого и второго подключающих элементов ИЛИ, вторые входы которых соединены соответственно с выходами первого фиксирующего Элемента И треть- Q„ей группы и второго фиксирующего элемента И второй группы, а выходы - с первыми входами соответственно второго и третьего полусумматоров, выход (p-d)-ro фиксирующего элемента И d-й группы (р-разряд результата, р 5,6, ...,2n-3, d 1,3,5,...,п-1) соединен соответственно с входом (р-4)-го нечетного элемента ИЛИ первой группы, выход которого соединен соответствен5

5

но с первым вхоцом сумматора р-го разряда второй группы, выход (p-q)-ro фиксирующего элемента И q-й группы (q 2,4,6,...,п) соединен соответственно с входом (р-А)-го четного элемента ИЛИ первой группы, выход которого соединен соответственно с вторым входом сумматора р-го разряда второй группы, выход (p-h)-ro фиксирующего элемента И h-й группы (h 1,2,...,i, i + 1, i + 4, i + 5,..., n - 3, n - 2) соединен соответственно с входом (р-4)-го нечетного элемента ИЛИ второй группы, выход которого соединен с первым входом сумматора р-го разряда третьей группы, выход (p-f)-ro фиксирующего элемента И f-й группы (f 3,4,7,8,..., i - 2, i - 1, i + 2, i + 3,..., n - 1, n) соединен соответственно с входом (р-4)-го четного элемента ИЛИ второй группы, выход которого соединен соответственно с вторым входом сумматора р-го разряда третьей группы, выход n-го фиксирующего элемента И (п-2)-й группы соединен с первыми входами третьего и четвертого подключающих элементов ИЛИ, вторые входы которых соединены соответственно с выходами (п-2)-го фиксирующего элемента И n-й группы и (п-1)-го фиксирующего элемента И (п-1)-й группы, а выходы - с первыми входами четвертого и пятого полусумматоров, выходы n-го фиксирующего элемента И (п-1)-й группы и (п-1)-го фиксирующего элемента И n-й группы соединены соответственно с первым и вторым входами сумматора (2п-1)-го разряда второй группы, выход суммы которого соединен с входом (2п-1)-го разряда 211-разрядного регистра результата, выход (2п-1)-го разряда которого соединен с третьим входом сумматора (2п-1)-го разряда второй группы, выход переноса которого соединен с первым входом шестого полусумматора, выход которого соединен с входом (2п-2)-го разряда 2п-разрядного регистра результата, выход n-го фиксирующего элемента И n-й группы соединен с вторым входом второго элемента ИЛИ, третий вход сумматора второго разряда первой группы соединен с выходом переноса сумматора третьего разряда второй группы, выход суммы которого соединен

0

5

0

5

0

5

0

5

0

5

с вторым входом сумматора третьего разряда первой группы, выход-р-го разряда 2п-разрядного регистра результата соединен соответственно с третьими входами сумматоров р-х разрядов второй и третьей групп, выходы переносов второго и третьего полусумматоров соединены соответственно с первым и вторым входами первого элемента ИЛИ третьей группы, выход которого соединен с третьим входом сумматора третьего разряда первой группы, выходы суммы второго и третьего полусумматоров соединены соответственно с первым и вторым входами второго элемента ИЛИ третьей группы, выход которого соединен с вторым входом сумматора четвертого разряда первой группы, выходы переноса сумматора р-х разрядов второй и третьей групп соединены соответственно с первым и вторым входами (р-З)-го нечетного элемента ИЛИ третьей группы, первый и второй входы (р-З)-го четного элемента ИЛИ третьей группы соединены соответственно с выходами суммы сумматоров р-х разрядов второй и третьей групп, выходы (р-З)-х нечетных и четных элементов ИЛИ третьей группы соединены соответственно с вторым входом сумматора (р-1)-го разряда первой группы и третьим входом сумматора р-го разряда первой группы, выходы переносов четвертого и пятого полусумматоров соединены соответственно с первым и вторым входами (4п-11)-го элемента ИЛИ третьей группы, выход которого соединен с третьим входом сумматора (2п-3)-го разряда первой группы, выходы суммы четвертого и пятого полусумматоров соединены соответственно с первым и вторым входами (4п-10)-го элемента ИЛИ третьей группы, выход которого соединен с вторым входом шестого полусумматора, выходы четвертого и (2п-2)-го разрядов 2п-разрядного регистра результата соединены соответственно с вторыми входами второго, третьего, четвертого и пятого полусумматоров, выход р-го разряда 2п- разрядного регистра результата соединен соответственно с третьими входами сумматоров р-х разрядов второй и третьей групп.

/5

,25

927

lay 13.213.3 ;

9.1 11.1

SP

.,.г-Рая

шгтнПф/Я/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1444755A1 |

| Устройство для умножения | 1989 |

|

SU1735842A1 |

| Устройство для умножения | 1989 |

|

SU1658148A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

Изобретение относится к вычис- лительной технике и может быть использовано при построении арифметических устройств электронных машин. Цель изобретения - расширение функциональных возможностей за счет вы-, полнения операции умножения при вводе n-разрядного множимого и п-раз- рядного множителя произвольных 1-х разрядов (i 1,2,...,п)„ Устройство содержит два n-разрядных кольцевых реверсивных регистра, два элемента запрета, фиксаторы множимого и множителя, два элемента И, две группы из п элементов И, п-разрядные регистры множимого и множителя, п групп из п формирующих элементов И, п групп из п фиксаторов состояния, п групп из п фиксирующих элементов И, три группы элементов ИЛИ, четыре подключающих элемента .ИЛИ, шесть полусумматоров, три группы сумматоров разрядов, два элемента ИЛИ, 2 п-раз- рядный регистр результата. Устройство позволяет выполнять операцию умножения как при прямом, так и при обратном порядке расположения разрядов множимого и множителя, а также осуществлять суммирование частичных произведений при их произвольном формировании. 1 ил. § /)

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения | 1984 |

|

SU1203512A1 |

Авторы

Даты

1991-06-07—Публикация

1989-06-14—Подача