Изобретение относится к вычислительной технике и .может быть использовано при создании микроЭВМ, микроконтроллеров и других устройств на основе микропроцессоров.

Цель изобретения - повышение производительности при отладке программ

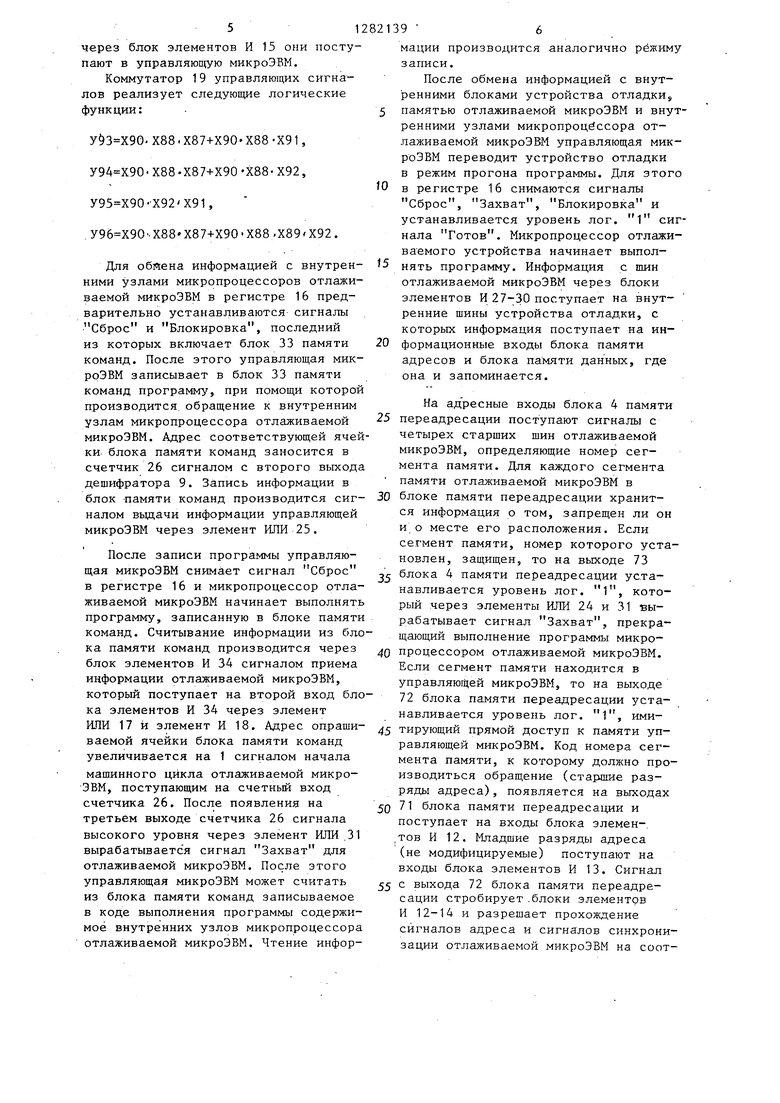

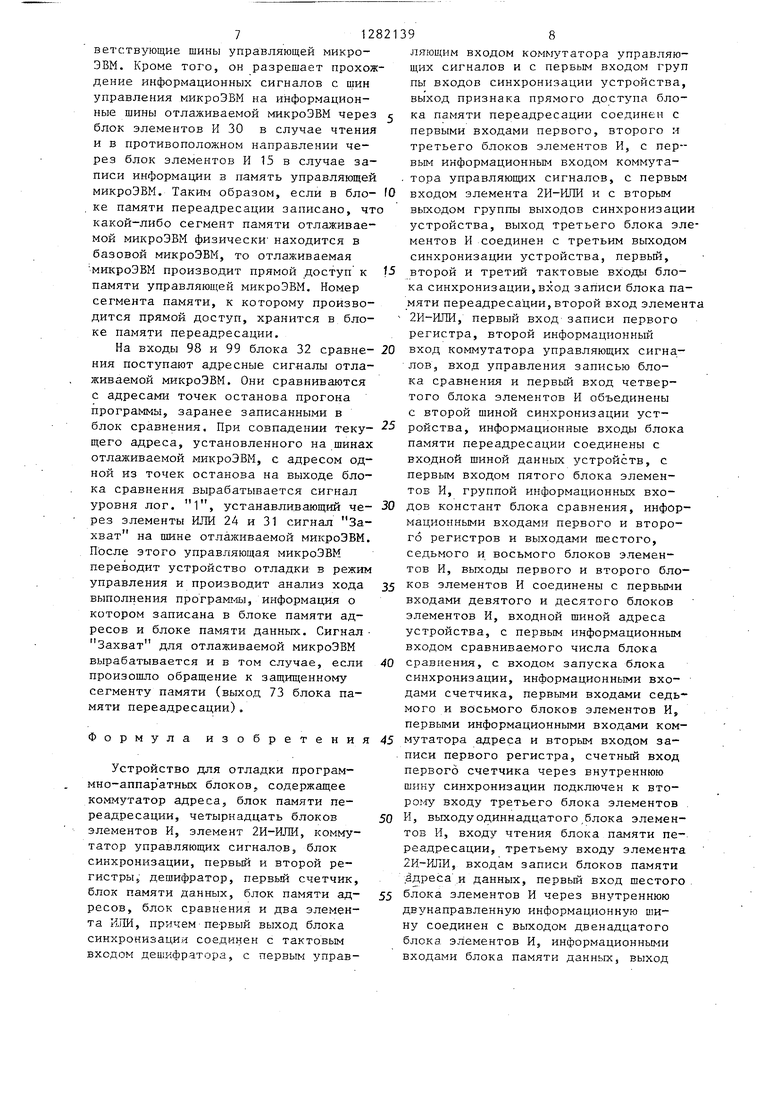

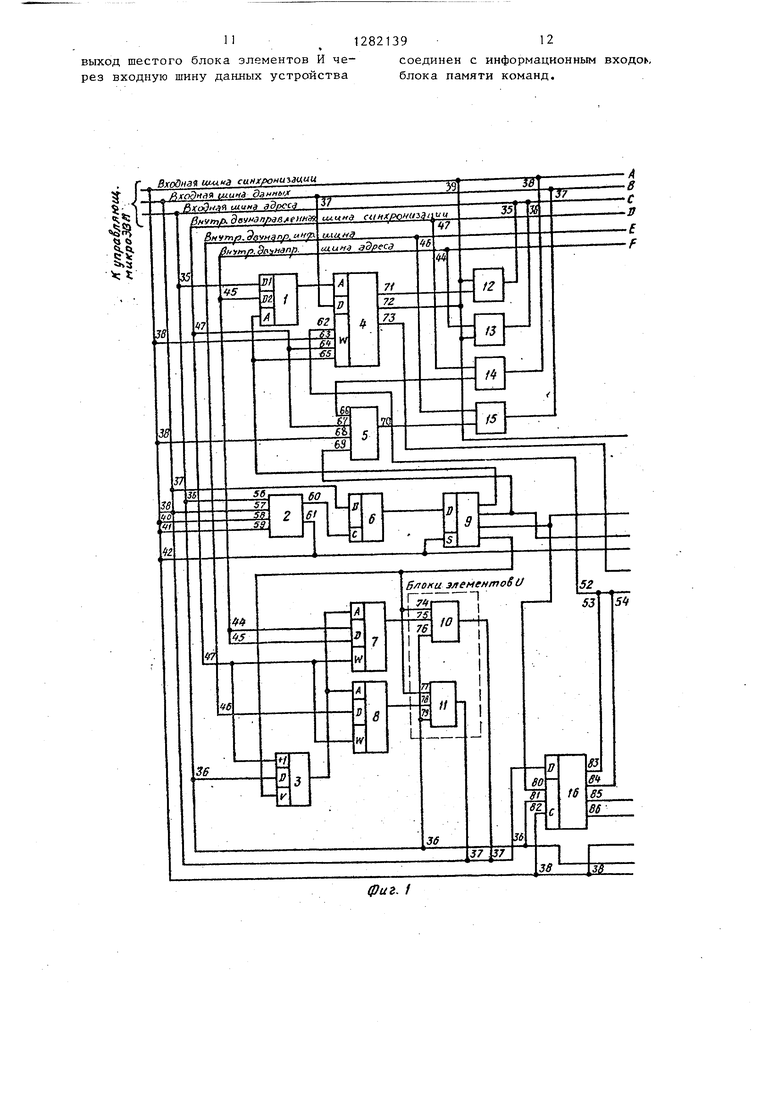

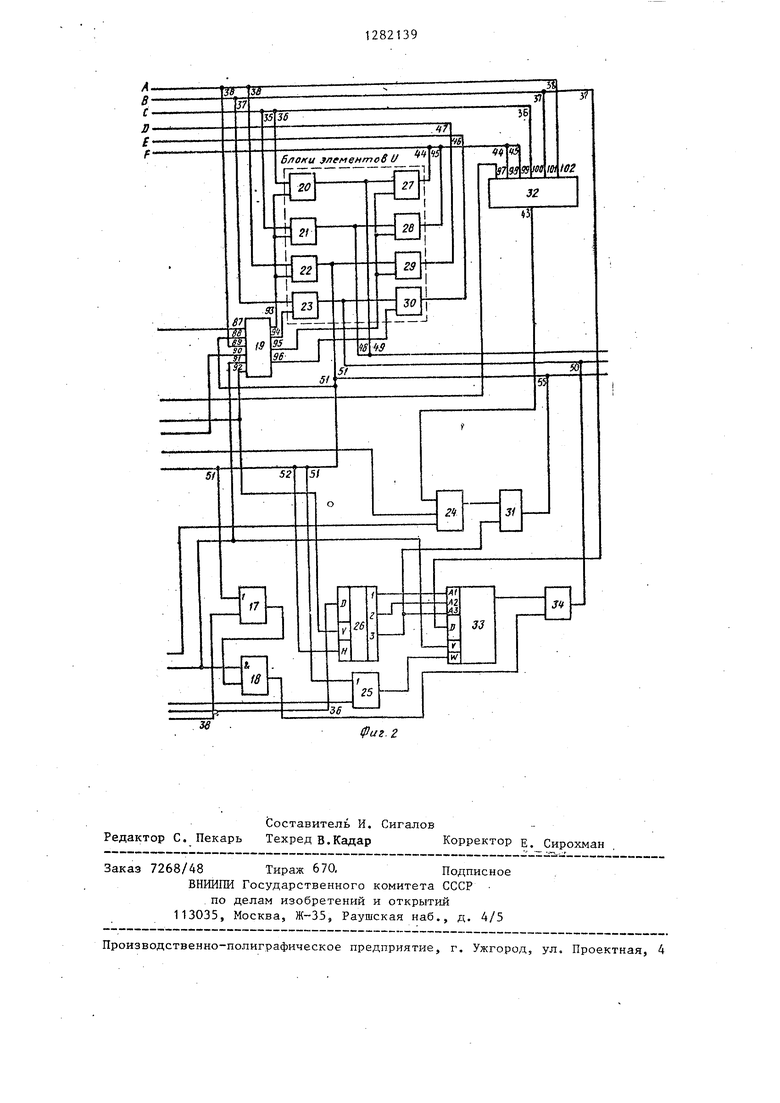

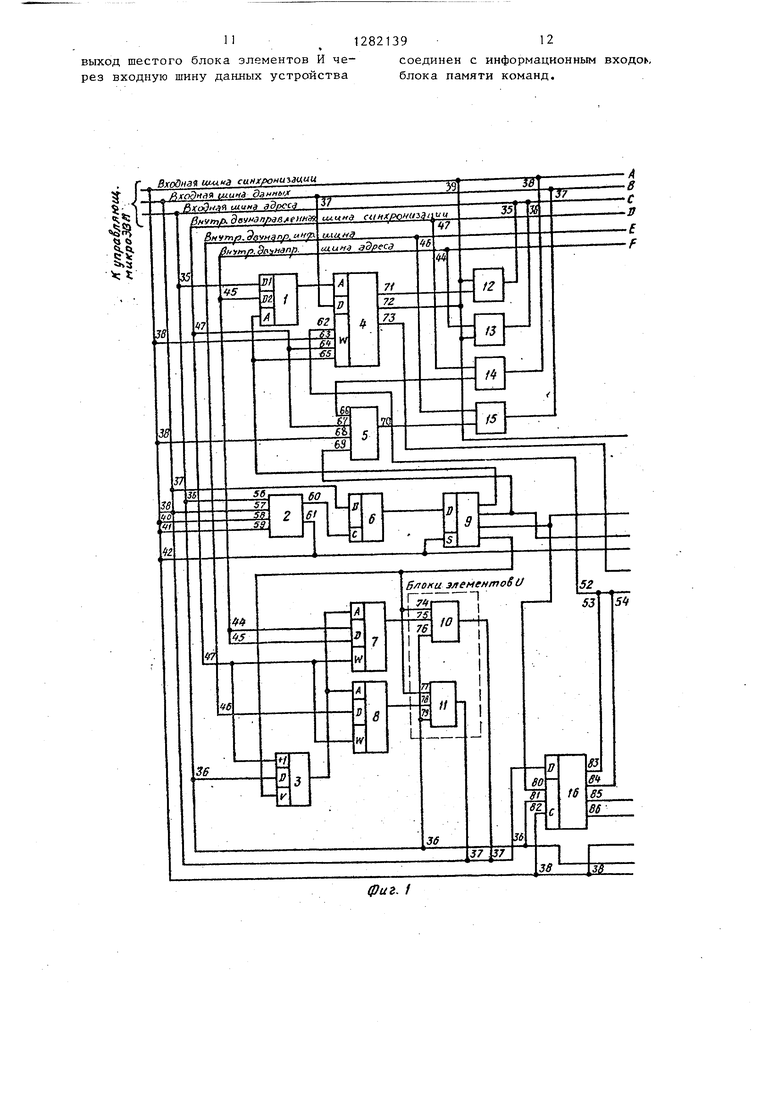

На фиг. 1 и 2 представлена структурная схема устройства для отладки программно-аппаратных блоков.

Устройство содержит коммутатор 1 адреса, блок 2 синхронизации, счетчик 3, блок 4 памяти переадресации, элемент 2И-ИЛИ 5, регистр 6, блок 7 памяти адресов, блок 8 памяти данных, дешифратор 9, блоки элементов И 10-15, регистр 16, элемент ИЛИ 17, элемент И 18, коммутатор 19 управляющих сигналов блоки элементов ,И 20-23, элементы ИЛИ 24 и 25, счетчик 26, блоки элементов И 27-30, элемент ИЛИ 31, блок 32 сравнения, блок 33 памяти команд, блок элементов И 34, адресные входы-выходы 35 и 36 устройства, информационные вхо- дытвыходы 37 устройства, входы-выходы 38 синхронизации устройств.а, выход 39 синхронизации устройства, входы 40 и 41 синхронизации устройства, выход 42 синхронизации устройства, i выход 43 блока сравнения, внутренние шины 44 и 45 адреса, внутреннюю шиРассмотрим работу устройства в режиме управления. В этом режиме работой устройства управляет блок 2 синхронизации. Для обращения к тому или иному блоку устройства отладки управляющая микроЭВМ устанавливает на входах 56 блока 2 синхронизации адрес, логически являющийся одним из портов вывода управляющей микррЭБМ, а на информационных входах регистра 6 - код блока, к которому производится обращение. При поступлении сигнала вьщачи информации, поступаю- щего на вход 57 блока синхронизации, на его выходе 60 появляется сигнал записи в регистр 6, После записи кода блок синхронизации начинает подсчет сигналов начала машинных циклов управляющей микроЭВМ (сигнал начала цикла поступает на вход 58). На седьмом цикле на вьиоде 61 блока 2 синхронизации появляется сигнал вклю чения дешифратора 9, поступающий одновременно через выход 42 синхрониза

ну 46 данных, внутреннюю шину 47 синхронизации, адресные, входы-выходы 48 35 ции на шину блокировки памяти и-пор- и 49 устройства, информационные вхо- тов. ввода-вывода управляющей микро- ды-выходы 50 устройства, входы-выхо- ЭВМ. При появлении сигнала включения

ды 51 синхронизации устройства, вход 52 синхронизации устройства, выходы 53-55 синхронизации устройства, входы 56-59 блока синхронизации, выходы 60 и 61 блока синхронизации, входы 62-65 записи блока памяти переадресации, входы 66-69 элемента 2И-ИЛИ,

40

дешифратора 9 на одном из его выходов появляется сигнал обращения к соответствующему блоку устройства.

Первый выход дешифратора 9 управляет загрузкой информации в блок 4 памяти переадресации. В этот блок завыход 70 элемента 2И-ШШ, выходы 71- 45 гружается информация о состоянии

73 блока памяти,входь 74-76 и 77-79 бло- каждого сегмента памяти, адресуемой

ков элеме1чтов И 10 и 11 соответственно,

входы 80-82 записи регистра 16 и его

выходы 83-86} входы 87-92 коммутатора

управляющих сигналов и его выходы 50

отлаживаемой микроЭВМ. При этом весь объем адресуемой памяти разбивается на 16 сегментов, определяемых четырьмя старшими разрядами адреса. Для каждого сегмента указывается защищен ли он (разрешено ли к нему обращение) , находится ли он в отлаживаемой микроэвм, находится ли он в управляющей микроЭВМ. В последнем случае указывается также, какой сегмент памяти управляющей микроЭВМ соответствует данному сегменту памяти отлаживаемой микроЭВМ. Информация

93-96 и входы 97-102 блока сравнения.

Устройство работает под управлением управляющей микроЭВМ, в качестве которой может быть использована микроэвм УВС-01, и обеспечивает отладку устройства, например, на основе микропроцессоров К580ИК80 или другого аналогичного типа.

0

5

Устройство для отладки микроЭВМ и микроконтроллеров может работать в одном из двух режимов: режиме управления и режиме прогона программы. В режиме управления управляющая мик- роЭВМ осуществляет обмен информацией с внутренними блоками устройства отладки, памятью и портами ввода-вывода отлаживаемой микроЭВМ, а также ее внутренними узлами.

Рассмотрим работу устройства в режиме управления. В этом режиме работой устройства управляет блок 2 синхронизации. Для обращения к тому или иному блоку устройства отладки управляющая микроЭВМ устанавливает на входах 56 блока 2 синхронизации адрес, логически являющийся одним из портов вывода управляющей микррЭБМ, а на информационных входах регистра 6 - код блока, к которому производится обращение. При поступлении сигнала вьщачи информации, поступаю щего на вход 57 блока синхронизации, на его выходе 60 появляется сигнал записи в регистр 6, После записи кода блок синхронизации начинает подсчет сигналов начала машинных циклов управляющей микроЭВМ (сигнал начала цикла поступает на вход 58). На . седьмом цикле на вьиоде 61 блока 2 синхронизации появляется сигнал вклю- чения дешифратора 9, поступающий одновременно через выход 42 синхрониза0

0

5 ции на шину блокировки памяти и-пор- тов. ввода-вывода управляющей микро- ЭВМ. При появлении сигнала включения

40

дешифратора 9 на одном из его выходов появляется сигнал обращения к соответствующему блоку устройства.

каждого сегмента памяти, адресуемой

0

5

отлаживаемой микроЭВМ. При этом весь объем адресуемой памяти разбивается на 16 сегментов, определяемых четырьмя старшими разрядами адреса. Для каждого сегмента указывается защищен ли он (разрешено ли к нему обращение) , находится ли он в отлаживаемой микроэвм, находится ли он в управляющей микроЭВМ. В последнем случае указывается также, какой сегмент памяти управляющей микроЭВМ соответствует данному сегменту памяти отлаживаемой микроЭВМ. Информация

312

записывается в блок памяти переадресации через входную шину данных. Адрес, по которому записывается эта информация, определяется адресом на четырех старших адресных шинах управляющей микроЭВМ, поступающим через коммутатор 1 на адресные входы блока 4 памяти переадресации. Запись в блок производится при подаче на вход 63 сигнала выдачи инфор- нации.

Третий выход дешифратора 9 управляет обращениями к блоку 32 сравнения и к регистру 16. Выбор каждого i-13 этих блоков производится в зависи мости от кода на трех младших адресных шинах управляющей микроЭВМ, подключенных к входу 100 блока 32 сравнения и входу 81 регистра 16. В блок 32 сравнения записываются адреса то- чек останова прогона программы. Эти адреса записываются в блок сравнения через входную шину данных, подключенную к входам 101 блока 32 сравнения. Запись производится при поступлении на вход 102 сигнала выдачи информации управляющей микроЭВМ.

В регистре 16 устанавливаются еле дующие сигналы, управляющие отлажи- ваемой микроэвм: Сброс (выход 83), Готов (выход 84), Захват (выход 85), Блокировка (выход 86). Назначение этих сигналов следующее: сигнал Сброс - это сигнал инициа- лизации, после поступления которого микропроцессор отлаживаемой микро- ЭВМ начинает обращение к нулевой ячейке памяти. Сигнал Готов высоким уровнем разрешает работу микро- процессора отлаживаемой микроЭБМ, а низким уровнем останавливает его. При низком уровне сигнала Готов микропроцессор останавливается в обращении к очередной ячейке памяти или порту ввода-вывода и не заканчивает это обращение до тех пор, пока уровень сигнала Готов не станет высоким. Сигнал Захват отключает микропроцессор отлаживаемой микро- ЭВМ от шин отлаживаемой микроЭВМ, позволяя тем самым осуществить прямой доступ к памяти последней. Сигнал Блокировка запрещает обращение к памяти и портам ввода-вывода отлаживаемой микроэвм и включает схему обращения к регистрам микропроцессора последней. З становка этих сиг- Нсшов производится через входную ши15

21

5

20

- 30 3540 45 50 55 394

ну данных, подключенную к информаци- онцым входам регистра 16, Установка производится при подаче на вход 82 сигнала выдачи информации управляющей микроэвм.

Четвертый выход дешифратора 9 уп- р авляет чтением из блоков памяти адресов и данных. В режиме управления из этих блоков считывается информация о ходе выполнения программ отлаживаемой микроэвм, записанная в эти блоки в режиме прогона программы. Эта информация включает состояния шин отлаживаемой микроЭВМ в каждом машинном цикле. Информация из блока памяти адресов считывается при подаче на вход 76 группы элементов И 10 кода адреса О, а информация из блока памяти данных считывается при подаче на вход 79 группы элементов И11 кода адреса 1, .

Второй выход дешифратора 9 управляет обращениями к памяти и портам ввода-вывода отлаживаемой микроЭВМ, а также обращениями к внутренним узлам микропроцессора последней. -Для обращения к памяти отлаживаемой микроЭВМ в регистре 16 предварительно устанавливается сигнал Захват, передающийся через элементы ИЛИ 24 и 31 на соответствующую шину отлаживаемой микроэвм. При поступлении этого сигнала микропроцессор последней отключается от шин и позволяет осуществить прямой доступ к памяти. Дешифратор 9 вырабатывает сигнал обращения к отлаживаемой микроЭВМ. При .этом, если производится запись в ее памятиJ адресные, информационные и управляющие сигналы управлякнцей микроЭВМ через блоки элементов И20-23, которые стробируются сигналами выходов 93 и 94 коммутатора 19 управляющих сигналов, через выходные шины поступают на соответствующие шины отлаживаемой микроЭВМ. Таким образом, информация из управляющей микроЭВМ записьшается в память отлаживаемой микроэвм. При чтении информации на памяти отлаживаемой микроЭВМ направление передачи адресных и управляющих сигналов остается таким же, как и в режиме записи, а направление передачи информационных сигналов изменяется на противоположное, Сигналы с информационных шин отлаживаемой микроЭВМ через блок элементов И 30 поступают на внутреннюю информационную . шину устройства отладки, а оттуда

через блок элементов И 15 они поступают в управляюпо ю микроЭВМ.

Коммутатор 19 управляющих сигналов реализует следующие логические функции:

. Х88.Х87+Х90 Х88-ХЭ1, У94 Х90-Х88.Х87+Х90Х88- Х92, У95 Х90--Х92 Х91, .Х88 Х87+Х90 Х88.Х89 Х92.

Для обйена информацией с внутренними узлами микропроцессоров отлаживаемой микроэвм в регистре 16 предварительно устанавливаются сигналы Сброс и Блокировка, последний из которых включает блок 33 памяти команд. После этого управляющая мик- роЭВМ записывает в блок 33 памяти команд программу, при помощи которой производится, обращение к внутренним узлам микропроцессора отлаживаемой микроэвм. Адрес соответствующей ячейки, блока памяти команд заносится в счетчик 26 сигналом с второго выхода дешифратора 9. Запись информации в блок -памяти команд производится сигналом вьщачи информации управляющей микроэвм через элемент ИЛИ 25.

После записи программы управляющая микроэвм снимает сигнал Сброс в регистре 16 и микропроцессор отлаживаемой микроэвм начинает выполнять программу, записанную в блоке памяти команд. Считывание информации из блока памяти команд производится через блок элементов И 34 сигналом приема информации отлаживаемой микроЭВМ, который поступает на второй вход блока элементов И 34 через элемент

На адресные входы блока 4 памяти 25 переадресации поступают сигналы с четырех старших щин отлаживаемой микроэвм, определяющие номер сегмента памяти. Для каждого сегмента памяти отлаживаемой микроЭВМ в блоке памяти переадресации хранится информация о том, запрещен ли он но месте его расположения. Если сегмент памяти, номер которого уста новлен, защищен, то на выходе 73 блока 4 памяти переадресации устанавливается уровень лог. 1, который через элементы ИЛИ 24 и 31 вырабатывает сигнал Захват, прекращающий выполнение программы микропроцессором отлаживаемой микроЭВМ. Если сегмент памяти находится в управляющей микроЭВН, то на выходе 72 блока памяти переадресации устанавливается уровень лог. 1, имиИЛИ 17 и элемент И 18. Адрес опраши- тирующий прямой доступ к памяти упваемой ячейки блока памяти команд увеличивается на 1 сигналом начала

машинного цикла отлаживаемой микро- ЭВМ, поступающим на счетный вход счетчика 26. После появления на третьем выходе счетчика 26 сигнала высокого уровня через элемент ИЛИ .31 вырабатываетс я сигнал Захват для отлаживаемой микроЭВМ. После этого управляющая микроЭВМ может считать из блока памяти команд записываемое в коде выполнения программы содержимое внутренних узлов микропроцессора отлаживаемой микроЭВМ. Чтение инфорравляющей микроЭВМ. Код номера сегмента памяти, к которому должно производиться обращение (старшие разряды адреса), появляется на выходах

50 71 блока памяти переадресации и поступает на входы блока элемен-. ,тов И 12. Младшие разряды адреса (не модифицируемые) поступают на входы блока элементов И 13. Сигнал

55 с выхода 72 блока памяти переадресации стробирует .блоки элементов И 12-14 и разрешает прохождение сигналов адреса и сигналов синхронизации отлаживаемой микроЭВМ на соот

мации производится аналогично режиму записи.

После обмена информацией с внутренними блоками устройства отладки,

памятью отлаживаемой микроЭВМ и внутренними узлами микропроцессора отлаживаемой микроэвм управляющая микроэвм переводит устройство отладки в режим прогона программы. Для этого

в регистре 16 снимаются сигналы Сброс, Захват, Блокировка и устанавливается уровень лог. 1 сигнала Готов. Микропроцессор отлаживаемого устройства начинает выполнять программу. Информация с шин отлаживаемой микроЭВМ через блоки элементов И 27-30 поступает на внутренние шины устройства отладки, с которых информация поступает на ин-

формационные входы блока памяти адресов и блока памяти данных, где она и запоминается.

На адресные входы блока 4 памяти переадресации поступают сигналы с четырех старших щин отлаживаемой микроэвм, определяющие номер сегмента памяти. Для каждого сегмента памяти отлаживаемой микроЭВМ в блоке памяти переадресации хранится информация о том, запрещен ли он но месте его расположения. Если сегмент памяти, номер которого установлен, защищен, то на выходе 73 блока 4 памяти переадресации устанавливается уровень лог. 1, который через элементы ИЛИ 24 и 31 вырабатывает сигнал Захват, прекращающий выполнение программы микропроцессором отлаживаемой микроЭВМ. Если сегмент памяти находится в управляющей микроЭВН, то на выходе 72 блока памяти переадресации устанавливается уровень лог. 1, ими

тирующий прямой доступ к памяти управляющей микроЭВМ. Код номера сегмента памяти, к которому должно производиться обращение (старшие разряды адреса), появляется на выходах

50 71 блока памяти переадресации и поступает на входы блока элемен-. ,тов И 12. Младшие разряды адреса (не модифицируемые) поступают на входы блока элементов И 13. Сигнал

55 с выхода 72 блока памяти переадресации стробирует .блоки элементов И 12-14 и разрешает прохождение сигналов адреса и сигналов синхронизации отлаживаемой микроЭВМ на соот71

ветствующие шины управляющей микро- ЭВМ. Кроме того, он разрешает проходение информационных сигналов с шин управления микроЭВМ на информационные шины отлаживаемой микроЭВМ чере блок элементов И 30 в случае чтени и в противоположном направлении через блок элементов И 15 в случае записи информации в память управляюще микроэвм. Таким образом, если в бло ке памяти переадресации записано, ч какой-либо сегмент памяти отлаживаемой микроэвм физически находится в базовой микроэвм, то отлаживаемая микроэвм производит прямой доступ к памяти управляющей микроЭВМ. Номер сегмента памяти, к которому производится прямой доступ, хранится в блоке памяти переадресации.

На входы 98 и 99 блока 32 сравне ния поступают адресные сигналы отлаживаемой микроэвм. Они сравниваются с адресами точек останова прогона программы, заранее записанными в блок сравнения. При совпадении теку щего адреса, установленного на шина отлаживаемой микроЭВМ, с адресом одной из точек останова на выходе блока сравнения вырабатывается сигнал уровня лог. 1, устанавливающий че рез элементы ИЛИ 24 и 31 сигнал Захват на шине отлаживаемой микроЭВМ После этого управляющая микроЭВМ переводит устройство отладки в режи управления и производит анализ хода выполнения програмг-ib, информация о котором записана в блоке памяти адресов и блоке памяти данных. Сигнал Захват для отлаживаемой микроЭВМ вырабатывается и в том случае, если произошло обращение к защищенному сегменту памяти (выход 73 блока памяти переадресации),

Формула изобретени

Устройство для отладки програм- мно-аппар атных блоков, содержащее комг утатор адреса, блок памяти переадресации, четырнадцать блоков элементов И, элемент 2И-ИЛИ, коммутатор управляющих сигналов, блок синхронизации, первый и второй ре- гистрЫ} дешифратор, первый счетчик, блок памяти данных, блок памяти ад- ресов, блок сравнения и два элемента ИЛИ, причем пе-рвый выход блока синхронизации соединен с тактовым входом дешифратора, с первым управ

8

ляющим входом коммутатора управляющих сигналов и с первым входом груп пы входов синхронизации устройства, вы ход признака прямого доступа блока памяти переадресации соединен с первыми входами первого, второго и третьего блоков элементов И, с первым информационным входом коммута- тора управляюш 1Х сигналов, с первым входом элемента 2И-ИПИ и с вторым выходом группы выходов синхронизации устройства, выход третьего блока элементов И соединен с третьим выходом синхронизации устройства, первый, второй и третий тактовые входы блока синхронизации,вход записи блока памяти переадресации,второй вход элемента 2И--ИЛИ, первый вход записи первого регистра, второй информационный вход коммутатора управляющих сигна- лов, вход управления записью блока сравнения и первый вход четвертого блока элементов И объединены с второй шиной синхронизации устройства, информационные входы блока памяти переадресации соединены с входной шиной данных устройств, с первым входом пятого блока элементов И, группой информационных входов констант блока сравнения, информационными входами первого и второго регистров и выходами шестого, седьмого и восьмого блоков элементов И, выходы первого и второго блоков элементов И соединены с первыми входами девятого и десятого блоков элементов И, входной шиной адреса устройства, с первым информационным входом сравниваемого числа блока сравненил, с входом запуска блока синхронизации, информационными входами счетчика, первыми входами седьмого и восьмого блоков элементов И, первыми информационными входами коммутатора адреса и вторым входом записи первого регистра, счетный вход первого счетчика через внутреннюю шику синхронизации подключен к вто- входу третьего блока элементов . И, выходу одиннадцатого ,блока элементов И, вход у чтения блока памяти пе-. реадресации, третьему входу элемента 2И-ИЛИ, входам записи блоков памяти адреса и данных, первый вход шестого, блока элементов И через внутреннюю вунаправленную информационную шину соединен с вьгходом двенадцатого блока элементов И, информационными входами блока памяти данных, выход

91

тринадцатого блока элементов И через внутреннюю двунаправленную шину адреса соединен с вторьм входом второго блока элементов И, выходом четырнадцатого блока элементов И, вхо дом за енения числа, вторым входом сравниваемого числа блока сравнения, вторыми информационными входами коммутатора адреса и информационными входами блока памяти -адреса, выход девятого блока элементов И через выходную шину адреса устройства соединен с выходом десятого блока элементов И, первым входом тринадцатого и четырнадцатого блоков элементов, вы- ходная информационная шина устройства подключена к выходу пятого блока элементов И и первому входу двенадцатого блока, элементов И, выходная шина синхронизации устройства соеди- нена с первым входом одиннадцатого блока элементов И, вторым управляющи входом коммутатора управляющих сигналов, первым и вторым информационными выходами первого регистра и тре Тьим входом записи блока памяти переадресации, выход коммутатора адреса соединен с адресным входом блока памяти переадресации, первый выход дешифратора соединен с управляюищ входом коммутатора адреса и входом обращения .блока памяти переадресации, второй выход дешифратора соединен с четвертым входом элемента ZH-fyiH и третьим информационным вхо- дом коммутатора управляющих сигналов, третий выход дешифратора соединен с входом управления записи констант блока сравнения и третьим входом записи первого регистра, инверс- ный выход дешифратора соединен с вторыми входами седьмого и восьмого блоков элементов И и входом записи счетчика, выход Которого соединен с адресными входами блоков памяти дан- ных и адресов, выходы которых соединены соответственно с третьими входами седьмого и восьмого блоков элементов И, тактовый выход блока синхронизации соединен с входом записи второго регистра, выход которого соединен с информационным входом дешифратора, второй выход блока памяти переадресации соединен с вторым входом первого блока элементов И, выход элемента 2И-ИЛИ соединен с вторым входом шестого блока элементов И, первый выход коммутатора управляющих сигналов соединен с вторыми входами

910.четвертого, девятого и десятого б.)Ю- ов элементов И, второй и третий выоды коммутатора управляющих сигнаов соединены с вторыми входами пятого и двенадцатого блоков элементов И соответственно, четвертый выход коммутатора управляющих.сигналов соеинен с вторыми входами одиннадцатого тринадцатого и четырнадцатого блоков

элементов И, выход блока сравнения соединен с первым входом первого элемента ИЛИ, выход которого, соединен с первым входом второго элемента ИЛИ, выход которого через вькод- ную шину синхронизадии соединен с выходом устройства, третий выход блока памяти переадресации подключен к второму входу первого элемента iiOH, отличающееся тем, что, с целью.повышения производительности, в негд введены пятнадцатый блок элементов И, второй счетчик, блок памяти команд, третий и четвертый элементы ИЛИ и элемент И, причем второй выход дешифратора . соединен с входом записи второго счетчика, входная шина адреса устройства соединена с информационными входами второго счетчика, выходная шина синхронизации соединена со счетным входом второго счетчика, с первыми входами третьего и четвертого элементов ИЛИ, вторая шина синхронизации устройства соединена с вторыми входами третьего и четвертого элементов ИЛИ, выходы третьего и четвертого элементов ИЛИ соединены соответственно с первым входом элемента И и входом записи блока памяти команд, выход которого соединен с первым входом пятнадцатого блока элементов И, выход элемента И соединен с вторым входом пятнадцатого блока элементов И; выход которого через выходную шину данных устройства подключен к выходу пятого блока элементов И, третий и четвертый вькоды первого регистра соединены соответственно с третьим входом первого элемента ИЛИ и вторым входом элемента И, четвертый выход первого регистра соединен с четвертым информационным входом коммутатора управляющих сигналов и входом обращения блока памя-. ти команд, выходы второго счетчика соединены с адресными входами блока памяти команд, выход старшего разряда второго счетчика соединен с вторым входом второго элемента ИЛИ,

11 , 1282139 12

выход шестого блока элементов И че- соединен с информационным входоь рез входную шину данных устройства блока памяти команд.

фиг. /

W

W

37

35

3S

Блохи :упементов и 4 20 27 Т

за

%

VSJ

фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1999 |

|

RU2214621C2 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

Изобретение относится к оЬла стй вычислительной техники и может быть использовано при создании микроЭВМ, микроконтроллеров и других устройств на основе микропроцессоров. Целью изобретения является повышение производительности при отладке программ. Устройство содержит коммутатор адреса, блок синхронизации, счетчики, блок памяти переадресации, элемент 2И-Ш1И, регистр, блок памяти- адресов, блок памяти данных, дешифратор, бло- ки элементов И, регистр, элементы ИЛИ, блок сравнения и блок памяти команд. В данном изобретении ориента- ция на конкретный микропроцессор производится программно, при этом за счет того, что при подключении к отлаживаемому устройству не требуется из последнего удалять микропроцессор, повышается производительность и достоверность отладки. 2 ил. (Л N5 00 ГчЭ 00 со

| Иванов Ю.В., Масленников Ю.А | |||

| Вопросы проектирования систем автоматизации разработки йрограмм для микроэвм | |||

| - УСИМ, 1978, № 5 | |||

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-07—Публикация

1984-02-14—Подача