10

15

20

5

11242965

Изобретение относится к вычислиельной технике и может быть испольовано при создании микроЭВМ,микроонтроллеров и других устройств на снове микропроцессоров.

Целью изобретения является расширение области использования и/ повышение достоверности отладки.

В предлагаемом устройстве ориентация на конкретный тип микропроцессора осуществляется программно, за счет чего достиг ается сокращение затрат аппаратуры.. Кроме того, поскольку для подключения к отлаживаемому устройству не требуется удалять из последнего микропроцессорj, повы- шается достоверность отладки и расширяется область использования устройства, при это оно может быть ис- польз.овано не только при разработке, но и для диагностики и контроля- при серийном производстве, а также при ремонте микропроцессорной техники.

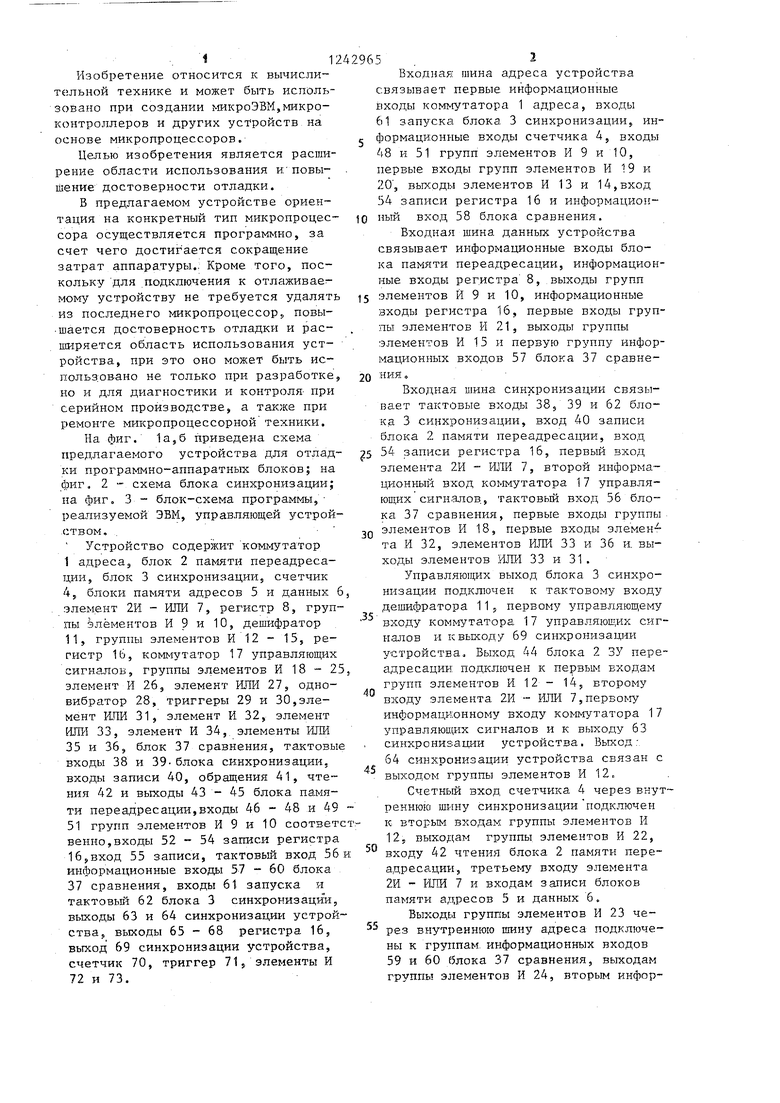

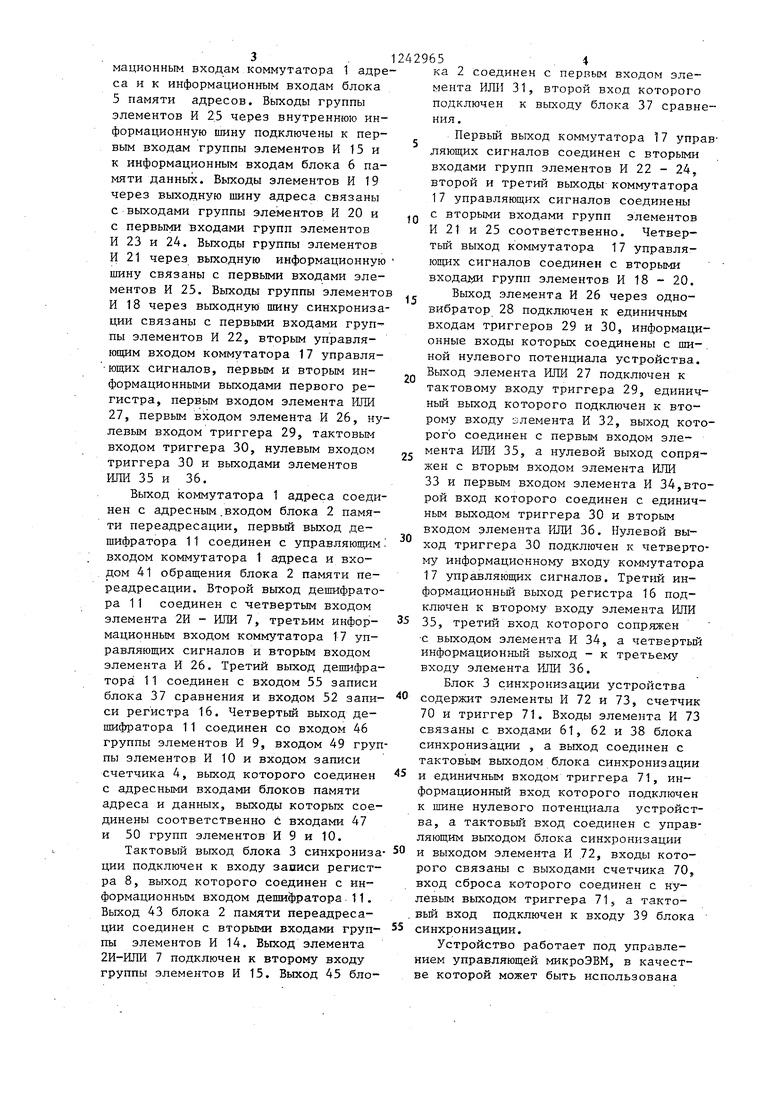

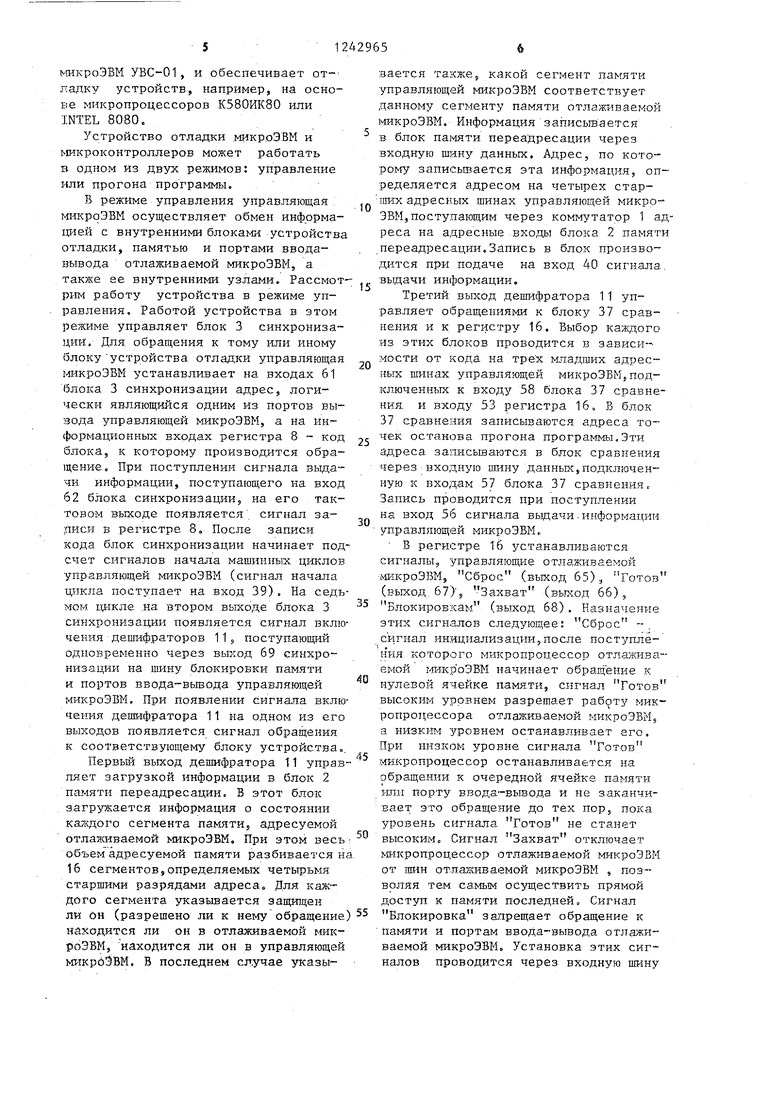

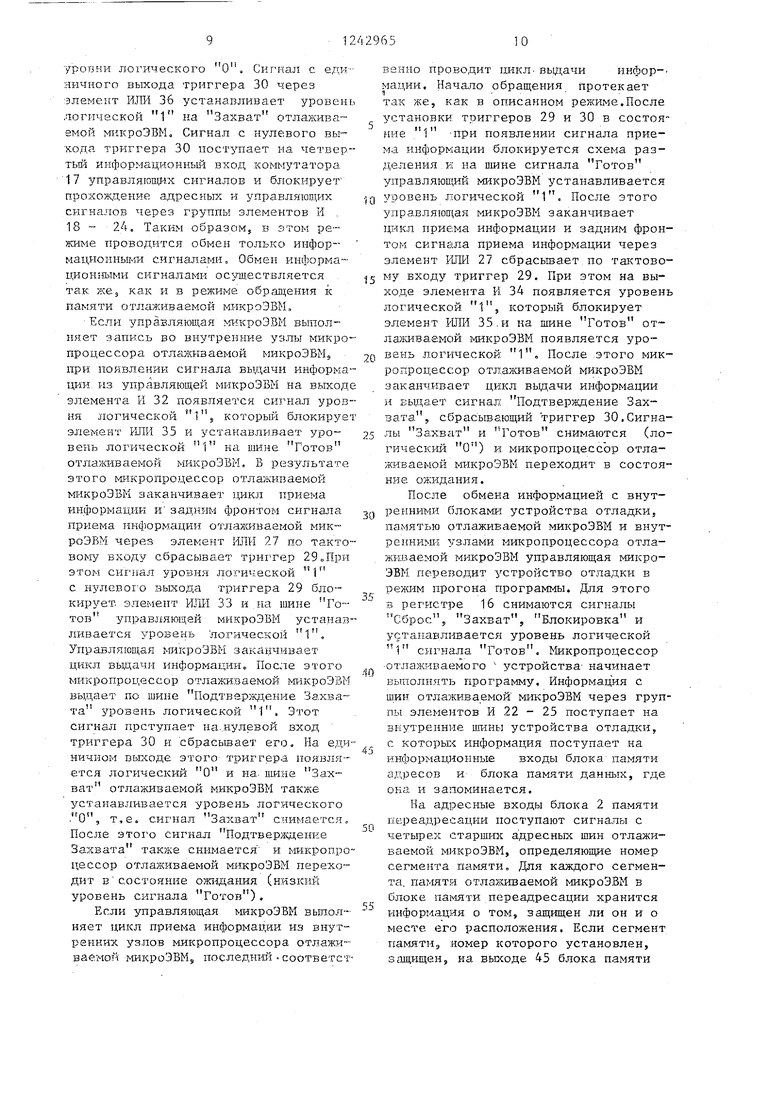

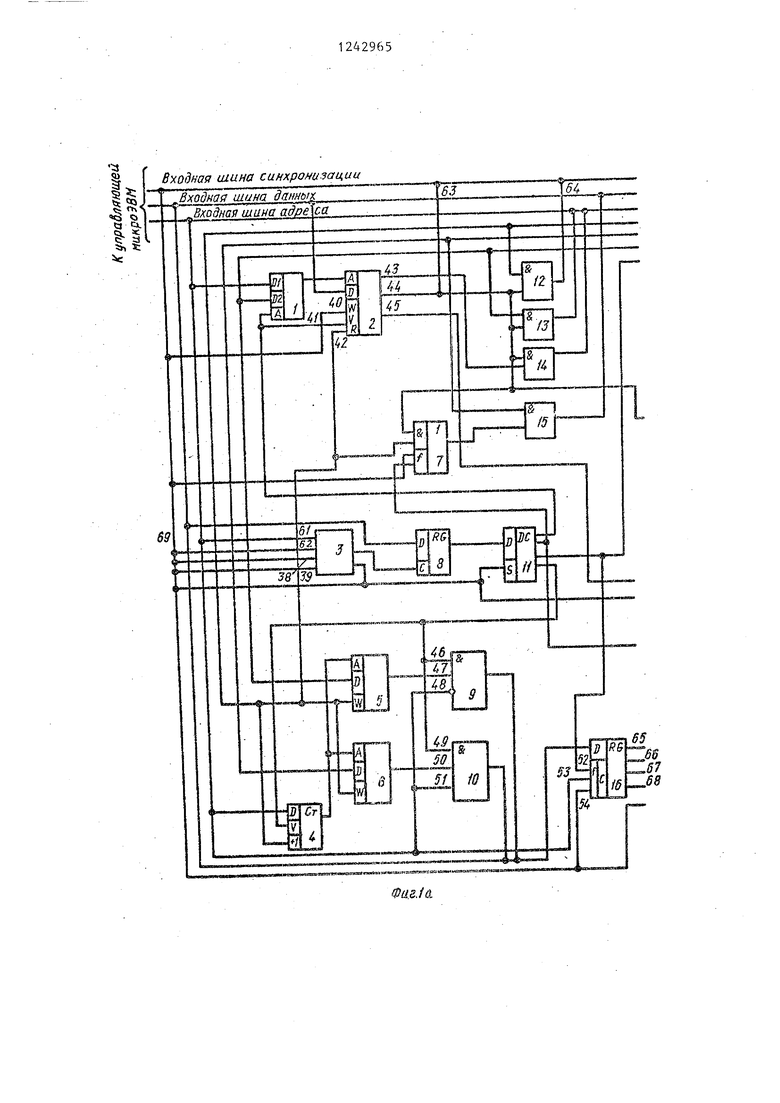

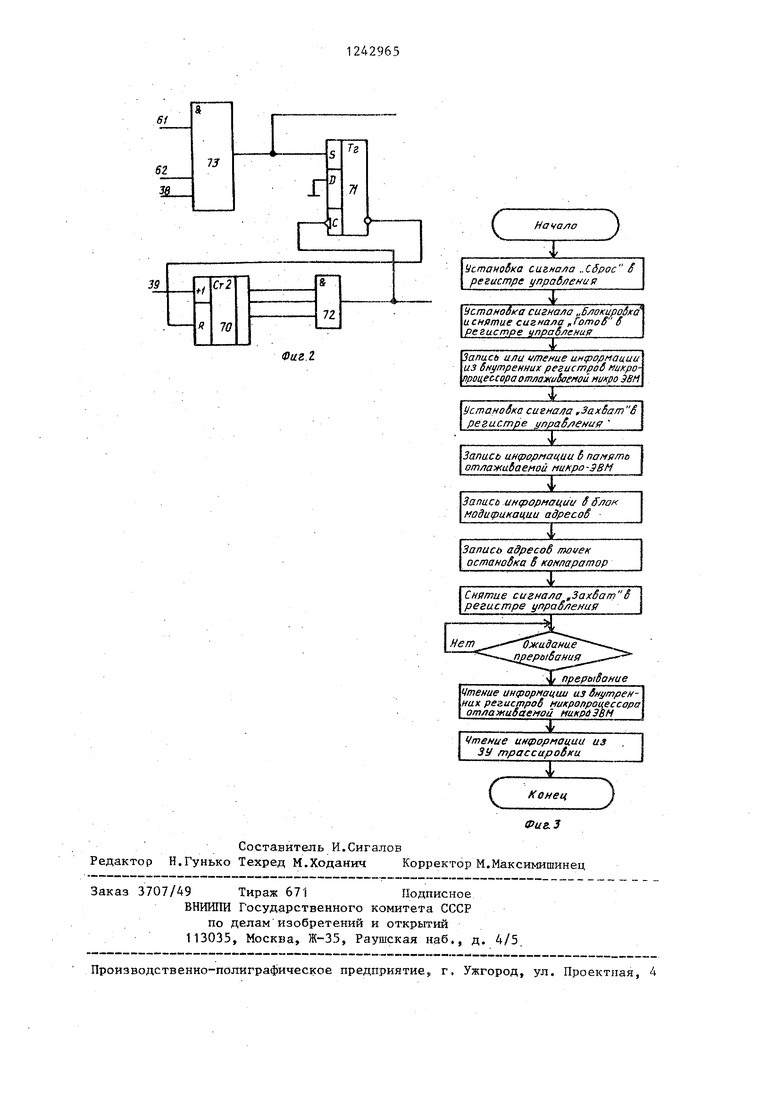

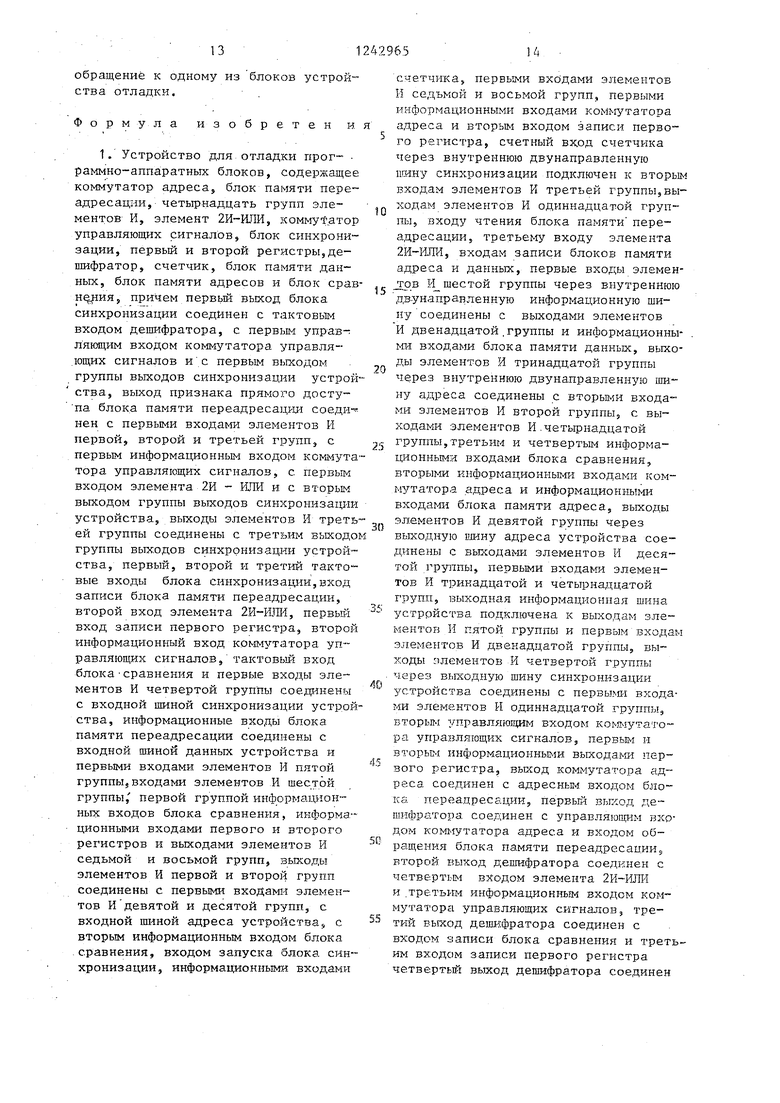

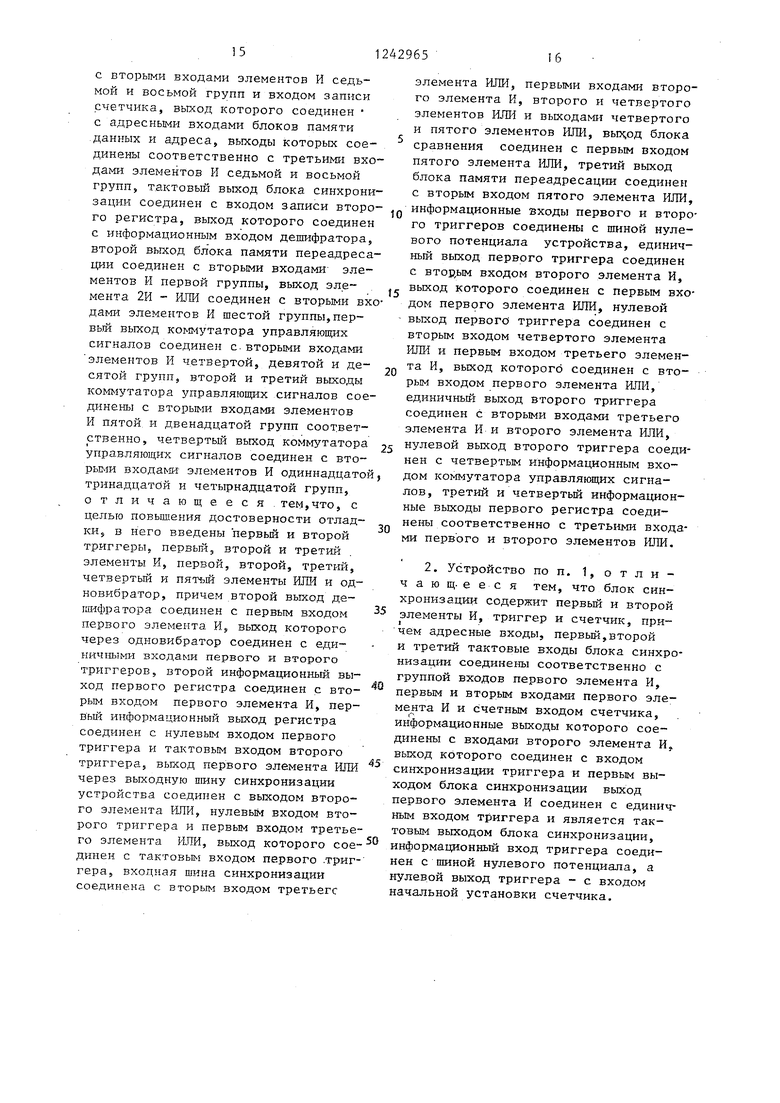

На фиг. 1а,б приведена схема предлагаемого устройства для отладит программно-аппаратных блоков; на фиг, 2 - схема блока синхронизации; на фиг. 3 - блок-схема программы, реализуемой ЭВМ, управляющей устрой- .ством.

Устройство содержит коммутатор 1 адреса, блок 2 памяти переадресации, блок 3 синхронизации, счетчик 4, блоки памяти адресов 5 и данных 6, .элемент 2И - ИЛИ 7, регистр 8, группы Элементов И 9 и 10, дешифратор 11, группы элементов И 12 - 15, регистр 16, коммутатор 17 управляющих сигналов, группы элементов И 18 - 25, элемент И 26, элемент ИЛИ 27, одно- вибратор 28, триггеры 29 и 30,элемент ШШ 31, элемент И 32, элемент ИЛИ 33, элемент И 34,, элементы ЩШ 35 и 36, блок 37 сравнения, тактовые входы 38 и 39-блока синхронизации, входы записи 40, обращения 41, чтения 42 и выходы 43 - 45 блока памяти переадресации,входы 46 - 48 и 49 - 51 групп элементов И 9 и 10 соответст:- венно,входы 52 - 54 записи регистра 16,вход 55 записи, тактовый вход 56 и информационные входы 57 - 60 блока 37 сравнения, входы 6t запуска и тактовьп 62 блока 3 синхронизации, выходы 63 и 64 синхронизации устрой30

,35

40

45

50

55

ства, выходы 65 - 68 регистра 16, выход 69 синхронизации устройства, счетчик 70, триггер 71 . элементы И 72 и 73.

0

15

20

5

965

30

,35

40

2

Входная шина адреса устройства связывает первые информационные )Е1Ходы ком гутатора 1 адреса, входы 61 запуска блока 3 синхронизации, информационные Входы счетчика 4, входы 48 и 51 групп элементов И 9 и 10, первые входы групп элементов И 19 и 20, вьгх:оды элементов И 13 и 14, вход 54 записи регистра 16 и информационный вход 58 блока сравнения.

Входная шина данных устройства связывает информационные входы блока памяти переадресации, информационные входы регистра 8, выходы групп элементов И 9 и 10, информационные входы регистра 16, первые входы группы элементов И 21, выходы группы элементов И 15 и первую группу информационных входов 57 блока 37 сравнения ,

Входная шина синхронизации связывает тактовые входы 38, 39 и 62 блока 3 синхронизации, вход 40 записи блока 2 памяти переадресации, вход. 54 записи регистра 16, первый вход элемента 2И - ШШ 7, второй информационный вход коммутатора 17 управляющих сигн.алов., тактовьш вход 56 блока 37 сравнения, первые входы группы элементов И 18, первые входы элемента И 32, элементов ИЛИ 33 и 36 и. выходы элементов Ш1И 33 и 31,

Управляющих выход блока 3 синхронизации подключен к тактовому входу дешифратора 11. первому управляющему входу коммутатора 17 управляющих сигналов и к выходу 69 сипхронизации устройства Выход 44 блока 2 ЗУ переадресации подключен к первым входам групп элементов И 12 - 14, второму

45

50

55

входу элемента 2И - ИЛИ 7,первоьгу информационному входу коммутатора 17 управляющих сигналов и к выходу 63 синхронизации устройства. Выход.- 64 синхронизации устройства связан с выходом группы элементов И 12,

Счетный вход счетчика 4 через внутреннюю шину синхронизации подключен к вторым входам: группы элементов И 12, выходам группы элементов И 22, входу 42 чтения блока 2 памяти пере адресации, третьему входу элемента 2И - Finn 7 и входам записи блоков памяти адресов 5 и данных 6,

Выходы группы элементов И 23 через внутреннюю шину адреса подключены к группам, информационных входов 59 и 60 блока 37 сравнения, выходам группы элементов И 24, вторым инфор3.

мационным входам коммутатора 1 адреса и к информационным входам блока 5 памяти адресов. Выходы группы элементов И 25 через внутреннюю информационную шину подключены к первым входам группы элементов И 15 и к информационным входам блока 6 памяти данных. Выходы элементов И 19 через выходную шину адреса связаны с выходами группы элементов И 20 и с первыми входами групп элементов И 23 и 24. Выходы группы элементов И 21 через выходную информационную шину связаны с первыми входами элементов И 25. Выходы группы элементо И 18 через выходную шину синхронизации связаны с первыми входами группы элементов И 22, вторым управля- входом коммутатора 17 управля- ющих сигналов, первым и вторым информационными выходами первого регистра, первым входом элемента ИЛИ 27, первым входом элемента И 26, нулевым входом триггера 29, тактовым входом триггера 30, нулевым входом триггера 30 и выходами элементов ИШ. 35 и 36.

Выход коммутатора 1 адреса соединен с адресным.входом блока 2 памяти переадресации, первый выход дешифратора 11 соединен с управляющим входом коммутатора 1 адреса и входом 41 обращения блока 2 памяти переадресации. Второй выход дешифратора 11 соединен с четвертым входом элемента 2И - ИЛИ 7, третьим информационным входом коммутатора 17 управляющих сигналов и вторым входом элемента И 26. Третий выход дешифратора 11 соединен с входом 55 записи блока 37 сравнения и входом 52 записи регистра 16. Четвертый выход дешифратора 11 соединен со входом 46 группы элементов И 9, входом 49 группы элементов И 10 и входом записи счетчика 4, выход которого соединен с адресными входами блоков памяти адреса и данных, выходы которых соединены соответственно и входами 47 и 50 групп элементов И 9 и 10.

Тактовый выход блока 3 синхронизации подключен к входу записи регистра 8, выход которого соединен с информационным входом дешифратора 11. Выход 43 блока 2 памяти переадресации соединен с вторыми входами группы элементов И 14. Выход элемента 2И-ИЖ 7 подключен к второму входу группы элементов И 15. Выход 45 бло10

15

20

25

42965. 4

ка 2 соединен с первым входом элемента ИЛИ 31, второй вход которого подключен к вькоду блока 37 сравнения .

Первый выход коммутатора 17 управляющих сигналов соединен с вторыми входами групп элементов И 22 - 24, второй и третий выходы коммутатора 17 управляющих сигналов соединены с вторыми входами групп элементов И 21 и 25 соответственно. Четвертый выход коммутатора 17 управляющих сигналов соединен с вторыми вxoдaJ групп элементов И 18 - 20. Выход элемента И 26 через одно- вибратор 28 подключен к единичным входам триггеров 29 и 30, информационные входы которых соединены с ши-, ной нулевого потенциала устройства. Выход элемента ИЛИ 27 подключен к тактовому входу триггера 29, единичный выход которого подключен к второму входу элемента И 32, выход которого соединен с первым входом элемента ИЛИ 35, а нулевой выход сопряжен с вторым входом элемента ИЛИ 33 и первым входом элемента И 34,второй вход которого соединен с единичным выходом триггера 30 и вторым входом элемента РШИ 36. Нулевой выход триггера 30 подключен к четвертому информационному входу коммутатора 17 управляющих сигналов. Третий ин- формационньй выход регистра 16 подключен к второму входу элемента ИЛИ 5 35, третий вход которого сопряжен с выходом элемента И 34, а четвертый информационный выход - к третьему входу элемента ИЛИ 36.

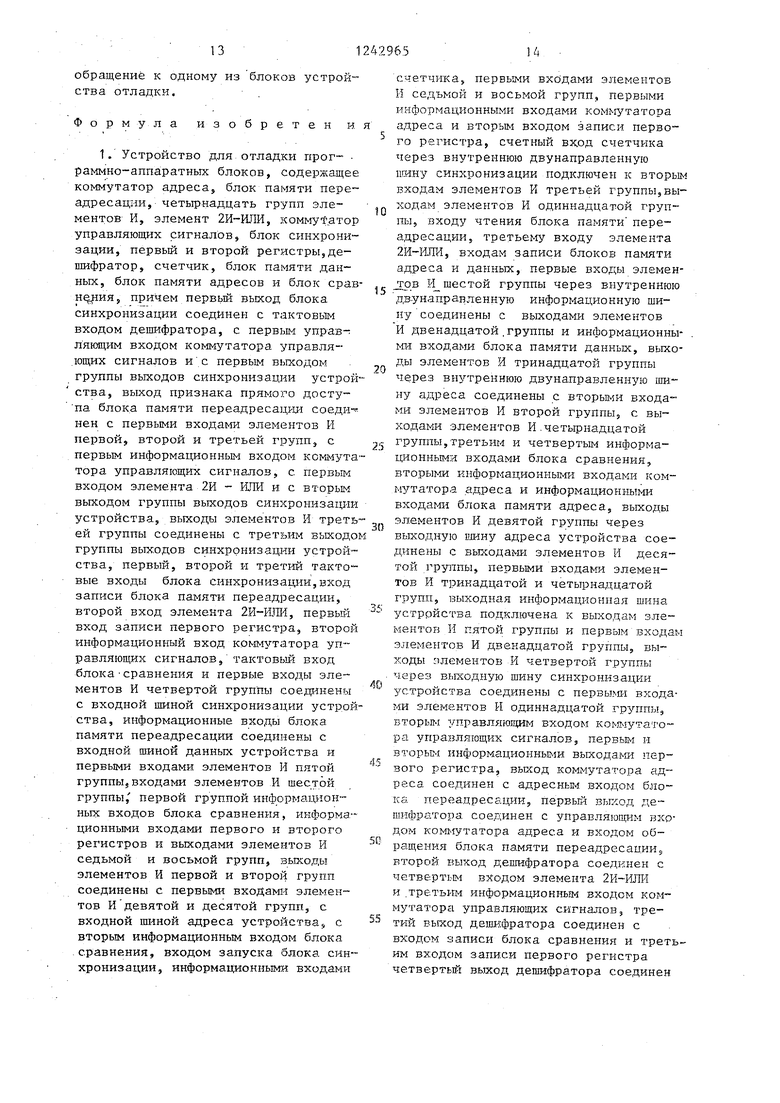

Блок 3 синхронизации устройства 0 содержит элементы И 72 и 73, счетчик 70 и триггер 71. Входы элемента И 73 связаны с входами 61, 62 и 38 блока синхронизации , а выход соединен с тактовым выходом блока синхронизации 5 и единичным входом триггера 71, информационный вход которого подключен к шине нулевого потенциала устройства, а тактовьй вход соединен с управляющим выходом блока синхронизации 0 и выходом элемента И 72, входы которого связаны с выходами счетчика 70, вход сброса которого соединен с нулевым выходом триггера 71, а тактовый вход подключен к входу 39 блока S синхронизации.

Устройство работает под управлением управляющей микроЭВМ, в качестве которой может быть использована

30

ь-шкроЭВМ УВС-01 , и обеспечивает от- ладку устройств, например, на основе микропроцессоров К580ИК80 или INTEL 8080.

Устройство отладки .микроЭВМ и 1 икроконтроллеров может работать в одном из двух режимов: управление или прогона программы,

В режиме управления управляющая микроэвм осуществляет обмен инфррма- 1щей с внутренними блоками устройства отладки, памятью и портами ввода- вывода отлаживаемой микроЭБМ, а также ее внутренними узлами. Рассмотрим работу устройства в режиме управления. Работой устройства в этом режиме управляет блок 3 синхронизации. Для, обращения к тому или иному блоку устройства отладки управляющая микроэвм устанавливает на входах 61 блока 3 синхронизации адрес, логически являющийся одним из портов вывода управляющей микроЭВМ, а на информационных входах регистра 8 код блока5 к которому производится обращение. При поступлении сигнала вьща- чи информации, поступающего на вход 62 блока синхронизации, на его тактовом выходе появляется сигнал записи в регистре 8, После записи кода блок синхронизации начинает подсчет сигналов начала машинных циклов управляющей микроЭВМ (сигнал начала цикла поступает на вход 39). На седьмом щжле ,на втором выходе блока 3 синхронизации появляется сигнал включения дешифраторов 11J поступающий одновременно через вькод 69 синхронизации на шину блокировки памяти и портов ввода-вьгоода управляющей микроЭБМ, При появлении сигнала включения дешифратора 11 на одном из его выходов появляется сигнал обращения к соответствующему блоку устройства, Первый выход дешифратора 11 управляет загрузкой информации в блок 2 памяти переадресации. В этот блок загружается информация о состоянии каждого сегмента памяти, адресуемой отлаясиваемой микроЭВМ, При этом весь объем адресуемой памяти разбивается н 16 сегментов,определяемых четырьмя старшими разрядами адреса. Для каждого сегмента указьшается защи1ден ли Он (разрешено ли к нему обращение находится ли он в отлаживаемой мик- роЗВМ, находится ли он в управляющей микроэвм. В последнем случае указы

5

0

5

0

5

5

0

5

вается также, какой сегмент памяти управляющей микроЭВМ соответствует данному сегменту памяти отлаживаемой 1 дакроЭВМ. Информация записывается в блок памяти переадресации через входную шину данных. Адрес, по кото-- ро№/ записьшается эта информация, определяется адресом на четырех стар- ших адресных шинах управляющей микро- ЭВМ, по ступающим через коммутатор 1 адреса на адресные входы блока 2 памяти переадресации,Запись в блок производится при подаче на вход 40 сигнала., выдачи информации.

Третий выход дешифратора 11 управляет обращениями к блоку 37 сравнения и к регистру 16, Выбор калодого из этих блоков проводится в зависи-- мости от кода на трех младших адресных шинах управляющей микроЭВМ,подключенных к входз 58 блока 37 сравнения, и входу 53 регистра 16. В блок 37 сравнения записываются адреса точек останова прогона программы,Эти адреса записьшаются в блок сравнения через входную агану данных,подключенную к входам 57 блока 37 сравнения. Запись проводится при поступлении на вход 56 сигнала вьщачи.информации управляющей микроЭВМ,

В регистре 1б устанавлива стся сигналы, управляющие отла.жи,ваемой микроЭБМ, Сброс (выход 65)., Готов (выход, 67), Захват (выход 66), Блокиров:кам (выход 68) . Назначение этих сигн.алов следующее: Сброс --. сигнал инициализации5 поcxie поступле- н ия которого мшсропроцессор отлаживаемой г-шкр оЭВМ начинает обращение к. нулевой ячейке памяти, сигнал Готов высоким уровнем разрешает работу микропроцессора отлаживаемой микроЭВМ, а низким уровнем останавливает его. При низком уровне сигнала Готов микропроцессор останавливается на обращении к очередной ячейке памяти ШП1 порту ввода-вьгоода и не заканчивает это обращение до тех пор, пока уровен,ь сигнала Готов не станет высоким. Сигнал Захват отключает микропроцессор отлаживаемой микроЭВМ от шин отлаживаемой микроЭВМ , позволяя тем самым осуществить прямой доступ к памяти последней. Сигнал Блокировка залрещает обращение к памяти и портам ввода-вывода отлаживаемой микроэвм. Установка этих сиг- нгшов проводится через входную шину

данных, подключенную к информационным входам регистра 16. Установка проводится при подаче на вход 54 сигнала вьщачи информации управляющей микроэвм.

Четвертьй выход дешифратора 11 управляет чтением из блоков памяти адресов и данных. В режиме управления из этих блоков считьшается информация о ходе выполнения программы отлаживаемой микроЭВМ, записанная в эти блоки в режиме прогона программы. Эта информация включает состояния шин отлаживаемой микроЭВМ в каждом машинном цикле. Информация из блока памяти адресов считывается при подаче на вход 48 группы элементов И 9 кода адреса О,, а информация из блока памяти данных считьшается .; при подаче на вход 51 группы элементов И 10 кода адреса 1.

Второй выход дешифратора 11 управляет обращениями к памяти и портам ввода-вьшода отлаживаемой микроЭВМ, а также обращениями к внутренним узлам микропроцессора последней. Для обращения к памяти отлаживаемой микроЭВМ в регистре 16 предварительно устанавливается сигнал Захват,передающийся через элемент ИЛИ 36 на со- ответствзтощую шину отлаживаемой микроЭВМ. При поступлении этого сигнала микропроцессор -последней отключается от шин и позволяет осуществить прямой доступ к памяти. Дешифратор 11 вьфабатьшает сигнал обращения к отлаживаемой микроэвм. При этом, если проводится запись в ее память, адресные, информационные и управляющие

сигналы управляющей микроЭВМ через группы элементов И 18 - 21, которые стробируются сигналами с второго и третьего выходов коммутатора 17 управляющих сигналов, через выходные шины поступают на соответствующие шины отлаживаемой микроЭВМ. Таким образом, информация из управляющей микроэвм записывается В память отлаживаемой микроэвм. При чтении информации из памяти отлаживаемой микроЭВМ направление передали адресньк и управляющих сигналов остается та- КИМ же, как и в режиме записи, а направление передачи информационных сиг.налов изменяется на противоположное, Сигналы с информационных шин отлаживаемой микроэвм, через группы элементов И 25 поступают на внутреннюю ин

формационную шину устройства отладки, а оттуда через группу элементов И 15 - в управляющую микроЭВМ.

Коммутатор управляющих сигналов 17 реализует следующие логические функции:

Y1 X51-X52.D1 VX51.X52 D4;

Y2 Х51-X52-D1 VX5bX52-D3;

10

15

20

25

5

0

5

5

0

Y3 X51.-X52-D3 D4; Y4 X51.X52-D1 V Х51 Х52г D2-D3, X

где Y:

D., - логические уров.

ни сигналов на

i-M выходе, j-M управляющем и к-м информационном входах коммутатора.

Для обмена информацией с внутренними узлами микропроцессора отлаживаемой микроэвм в регистре 16 предварительно устанавливается сигнал Блокировка и снимается сигнал Готов (т.е. на выходе 67 регистра 16 устанавливается уровень логи- ческого (О). Сигнал Готов с выхода 67 регистра 16 через элемент 1ШИ 35 поступает на соответствующую шину отлаживаемой никроЭВМ. Сигнал Блокировка с выхода 68 регистра 16 поступает на соответствующую шину отлаживаемой микроЭВМ.Затем дешифратор 11 вырабатывает сигнал обращения. к отлаживаемой микро- ЭВМ. При совпадении этого сигнала с сигналом Блокировка, сигнал уровня логической 1 с выхода элемента И 26 через одновибратор 28 устанавливает по единичным входам триггеры 29 и 30, Сигнал уровня логической 1 поступает на вход элемента И 32, а сигнал уровня логического О с нулевого выхода триггера 29 поступает на вход элемента ИЛИ 33, Так как в начале машинного цикла управляющей . микроэвм сигналы вьщачи информации (поступает на второй вход элемента И 32) и приема информации (поступает на второй вход элемента ИЛИ 33) отсутствуют (логический О), на выходе элемента И 32 н на выходе элемента ШШ 35 сохраняется уровень логического О, а на выходе элемента ИЛИ 33 -появляется сигнал уровня логического О, Таким образом, при обращении управляющей микроЭВМ к микропроцессору отлаживаемой микроЭВМ на шинах Готов управляющей и отла- живаемой микроЭВМ устанавливаются

Уровни логического О. Сигнал с едрг- яичного выхода триггера 30 через элемент ИЛИ 36 устанавливает уровень логической 1 на Захват отлажгиза-- емой микроэвм,, Сигнал с нулевого выхода триггер а 30 поступает на четвертый информационньй вход кoм syтaтopa

17управляюиях сигналов и блокирует прохождение адресных и управляюп рк сигналов через группь элементов И .

18- 24, Таким образом, в этом режиме проводится обмен только информационными сигналами. Обмен информа- сигналами осуществляется так жвд как и в режиме обраа ения к отлаживаемой микроЭВМ,

Если управляющая микроЭВМ выполняет запись во внутренние у;)лы микропроцессора отлаживаемой микроЭВМ, при появлении сигнала выдачи информации из управляющей микроЭВМ на выходе элемента И 32 появляется сигнал уров-ни логической 1 , который блокирует элемент ШШ 35 и устанавливает уро- тс;

отла51даваемой микроЭВМ, В результате этого микропроцессор отлалсиваемой микроэвм заканчивает цикл приема информации и задним фронтом сигнала приема информации отлалшваемой мик™ роЭВМ через эле.мент ШШ 27 по тактовому входу сбрасывггет триггер 29 о При этом сигнал уровня логической 1 с нулевого выхода триггера 29 блокирует, элемент ШШ 33 и на шине Готов управляющей микроЭВМ устаназ-ливается уровень логической 1 , Управляющая №1кроЭВМ закги.гчивает цикл вьщачи информации. После этого микропроцессор отлажи}заемой микроЭВМ выдает по шине Подтверждение Захвата уровень логической 1. Этот сигнал прступает на.нулевой вход триггера 30 и сбрасьшает его. На единичном Бькоде этого триггера появляется логический О и на. шине Захват отлаживаемой микроЭВМ также устанавливается уровень лог:яческого .О, т.е. сигнал Захват снимается,, После этог о сигнал Подтверждение Захвата также снимается и микропроцессор отлаживаемой микроЭВМ переходит в состояние ош-щания (низкий уровень сигнала Готов).

Если управляющая микроЭВМ выполняет цикл приема информации из внутренних уз,лов микропроцессора отлаживаемой м11КроЭВМ, последний .соответст

венно проводит гшкл- выдачи инфор- нации. Нача-по обращения протекает так же, как в описанном релсиме.После установки триггеров 29 и 30 в состояние 1 При появлении сигнала приема информации блокируется схема разделения и на пшне сигнала Готов управляющий микроэвм устанавливается уровень логической 1. После этого управляющая микроЭВМ заканчивает цикл приема информации и задним фронтом сигнала приема информации через элемент 27 сбрасывает по тактовому входу триггер 29. При этом на выходе элемента И 34 появляется уровень

1

который блокирует

0

с;

элемент ИТИ 35,и на шине Готов от- лалшваемой микроЭВМ появляется уровень логической После -ЭТОГО микропроцессор отлаживаемой микроЭВМ заканчивает цикл вьщачи информации и выдает сигнал Подтверждение Захвата, сбрасывающий триггер 30.Сигналы Захват и Готов снимаются (логический О ) и микропроцессор отлаживаемой микроэвм переходит в состояние ожидания.

После обмена информацией с внутренними блоками устройства отладки, памятью отлаживаемой микроЭВМ и внутренними узлами микропроцессора отлаживаемой микроэвм управляющая микро- ЭВМ переводит устройство отладки в режим прогона программы. Для этого в регистре 16 снимаются сигналы Сброс J Захват, Блокировка и устанавливается уровень логической 1 сигнала Готов. Микропроцессор отлаживаемого устройства- начинает выполнять программу. Информация с шин отлаживаемой микроЭВМ через группы элементов И 22 - 25 поступает на внутренние шины устройства отладки, с которьЕ информация поступает на информацнонные входы блока памяти адресов и блока памяти даншлх, где она и запоминается.

На адресные входы блока 2 памяти переадресации поступают сигналы с четырех старших адресных шин отлаживаемой микроэвм, определяюш е номер сегмента памяти. Для каждого сегмента, памяти отла,):хиваемой микроЭВМ в блоке памяти, переадресации хранится информация о том, защищен ли он и о месте его расположения. Если сегмент памятиэ номер которого установлен, згидищен, на вьпсоде 45 блока памяти

переадресации устанавливается уровень логической 1, которьш через элементы ИЛИ 31 и 36 вырабатьшает сигнал Захват, прекращающий выполнение программы микропро1дессором отлаживаемой микроэвм. Если сегмент памяти находится в управляющей микро ЭВМ, на выходе 44 блока памяти переадресации устанавливается уровень логической 1 иницирующий прямой доступ к памяти управляющей микроЭВМ Код номера сегмента памяти, к которому должно проводитьс обращение (старшие разряды адреса), появляется на вькодак 43 блока памяти переадресации и поступает на входы группы элементов И 14. Младшие разряды адреса (не модифицируемые) поступают н входы группы элементов И 13. Сигнал с выхода 43 блока памяти переадресации стробирует группы элементов И 12 - 14 и разрешают прохождение сигналов адреса и сигналов синхронизации отлаживаемой микроЭВМ на со- ответствующие шины управляющей микро ЭВМ, Кроме того, он разрешает прохождение информационных сигналов с шин управляющей микроЭВМ на информационные шины отлаживаемой микроЭВМ через группу элементов И 21 в случае чтения и в противоположном направлении через группу элементов И 15 в случае записи информации в память управляющей микроЭВМ. Таким образом, если в блоке памяти переадресации записано, что какой-либо сегмент памяти отлаживаемой микроЭВМ физически находится в базовой микроЭВМ, то отлаживаемая микроэвм проводит прямой доступ к памяти управляющей микро- ЭВМ. Номер сегмента памяти, к которому проводится прямой доступ, хранится в блоке памяти переадресации.

На входы 59 и 60 блока 37 сравнения поступают адресные сигналы отлаживаемой микроэвм и сравниваются с адресами точек останова прогона программы, заранее записанными в блок сравнения. При совпадении текущего адреса, установленного на шинах отлаживаемой микроЭВМ, с адресом одной из точек останова на выходе блока сравнения вырабатьшается сигнал уровня логической 1, устанавливающий через элемент ИЛИ 31 сигнал Прерьгоание на шине управляющей микроэвм, а через элемент ИЛИ 36 - сигнал Захват на шине отлажи

-JQ. а jo 25 ,,,

35

40

45

50

ваемой микроэвм. После получения сигнала Прерьшание управляющая микроэвм переводит устройство отладки в режим управления и проводит ана ЛИЗ хода выполнения программы, информация о котором записана в блоке памяти адресов и блоке памяти данных. Сигналы Прерывание для управляющей микроэвм и Захват для отлаживаемой микроэвм вьфабатьшаются и в том случае, если произошло обращение к за- щищенному сегменту памяти (выход 45 блока переадресации).

Блок-схема алгоритма взаимодействия управляющей микроЭВМ с устройством для отладки микроЭВМ и микроконтроллеров представлена на фиг. 3.

Блок синхронизации работает следующим образом.

Для обращения :К тому или иному блоку устройства отладки управляющая микроэвм устанавливает на входах 61 адрес блока синхронизации, а на входе 62 - признак обращения к порту ввода-вьгоода (блок синхронизации логически является одним из портов вывода управляющей микроЭВМ). При поступлении на вход 38 сигнала вьща- чи информации из управляющей микроЭВМ на выходе элемента И 73 появляется сигнал уровня логической 1 который устанавливает триггер 71 и заносит, код блока устройства отладки в регистр 8 (фиг. 1). После установки триггера 71 снимается сигнал сброса счетчика 70 (логической О) и он начинает подсчет сигналов начала машинного цикла управляющей MIIK- роЭВМ, поступающих на счетный вход счетчика по входу 39. При поступлении например, седьмого сигнала начала машинного цикла управляющей микг роЭВМ на выходах счетчика 70 устанав- ливаются код и сигнал с выхода элемента И 72 включает дешифратор 11 и устанавливает сигнал блокировки памяти и портов ввода-вьшода управляющей микроэвм (фиг. 1). При поступлении на счетный вход счетчика 70 следующего сигнала начала машинного цикла управляющей микроЭВМ на выходе элемент И 72 устанавливается уровень логического О. При этом по тактовому входу сбрасьшается триггер 71, который сбрасьюает счетчик 70. Таким образом, на заданном машинном цикле после обращения к блоку синхронизации управляющая микроЭВМ производит

обращение к одному из блоков устройства отладки.

Формула изобретен и

1. Устройство для отладки прог- раммно-аппаратных блоков, содержащее коммутатор адреса, блок памяти пере- адресации, четырнадцать групп элементов И, элемент 2И-ИЛИ, KOMNrytaxop управляющих сигналов, блок синхронизации, первый и второй регистры,дешифратор, счетчик, блок памяти данных, блок памяти адресов и блок срав , причем первьий выход блока синхронизации соединен с тактовым входом дешифратора, с первым управляющим входом коммутатора управля- .ющих сигналов и с первым выходом группы выходов синхронизации устройства, выход признака прямого досту- па блока памяти переадресации соеди- йен с первыми вxoдa ш элементов И первой, второй и третьей групп, с первым информационным входом коммутатора управляющих сигналов, с первым входом элемента 2И - ИЛИ и с вторым выходом группы выходов синхронизации устройства, выходы элементов И третьей группы соединены с третьим выходо группы выходов синхронизации устройства, первый, второй и третий такто вые входы блока синхронизации,вход записи блока памяти переадресации, второй вход элемента 2И-ШЖ, первы-й вход записи первого регистра, второй информационный вход коммутатора управляющих сигналов, тактовый вход блокасравнения и первые входы элементов И четвертой группы соединены с входной шиной синхронизации устройства, информационные входы блока памяти переадресации соединены с входной шиной данных устройства и первыми входами элементов И пятой группы входами элементов И шестой группы, первой группой информационных входов блока сравнения, информационными входами первого и второго регистров и выходами элементов И седьмой и восьмой групп, выходы элементов И первой и второй групп соединены с первыми входам- элементов И девятой и десятой групп, с входной шиной адреса устройства, с вторым информационньм входом блока -Сравнения, входом запуска блока синхронизации, информационными входами

5

0

;5

0

C

5

счетчика, первыми входами элементов И седьмой и восьмой групп, первыми информационными входами коммутатора адреса и ззторым входом записи первого регистра, счетный вход счетчика через внутреннюю двунаправленную игяну синхронизации подключен к вторым входам элементов И третьей группы,выходам элементов И одиннадцатой группы, входу чтения блока памяти переадресации, третьему входу элемента 2И-1 1Ш-15 входам записи блоков памяти адреса и данных, первые входы элемен- трв И шестой группы через внутреннюю двунаправленную информационную шину соединены с выходами элементов И двенадцатой.группы и информационными входами блока памяти данных, выходы элементов И тринадцатой группы через внутреннюю двунаправленную шину адреса соединены с вторьми входами элементов И второй группы, с выходами элементов И.четырнадцатой группы,третьим и четвертым информационными входами блока сравнения, вторыми информационньиуги входами коммутатора адреса и информационными входами блока памяти адреса, выходы элементов И девятой группы через выходную 1шну адреса устройства соединены с выходами элементов И десятой , первыми входами элементов И тринадцатой и четырнадцатой групп, выходная информационная шина устройства подключена к выходам элементов И пятой группы и первым входам элементов И двенадцатой группы, выходы элементов И четвертой группы через выходнувэ шину синхронизации устройства соединены с первыми входами элементов И одиннадцатой группы, Бторьм управляющим входом KorvK-syTaTo- pa управляющих сигналов, первым и вторьв-1 информационными выходами первого регистра, выход коммутатора адреса соединен с адресньм входом блока переадресации., первый вькод дешифратора соединен с управляющим входом коммутатора адреса и входом обращения блока памяти переадресации, второй выход дешифратора соединен с четвертом входом элемента 2H-I-fflI I и .третью информационнь м входом коммутатора управляющих сигналов, третий вь5ход деш Ефратора соединен с входом записи блока сравнения и третьим входом записи первого регистра четвертый выход дешифратора соединен

с вторыми входами элементов И седьмой и восьмой групп и входом записи счетчика, выход которого соединен с адресНЫМР1 входами блоков памяти .данных и адреса, выходы которых соединены соответственно с третьими входами элементов И седьмой и восьмой групп, тактовый выход блока синхронизации соединен с входом записи второ

го регистра, выход которого соединен с информационным входом дешифратора, второй выход бл ока памяти переадресации соединен с вторыми входами- элементов И первой группы, выход эле- мента 2И - ИЖ соединен с вторыми вхдами элементов И шестой группы,первый выход коммутатора управляющих сигналов соединен с. вторыми входами элементов И четвертой, девятой и де- сятой групп, второй и третий выходы коммутатора управляющих сигналов соединены с вторыми входами элементов И пятой и двенадцатой групп соответственно, четвертьй выход коммутатора управляющих сигналов соединен с вторыми входами элементов И одиннадцато тринадцатой и четырнадцатой групп, отличающееся, тем,что, с целью поБьштения достоверности отладки, в него введены первьп и второй триггеры, первый, второй и третий элементы И, первой, второй, третий, четвертый и пятъй элементы ИЛИ и од- новибратор, причем второй выход де- гш фратора соединен с первым входом первого элемента И, выход которого через одновибратор соединен с е,ди- ничнь ми хоцами первого и второго триггеров, второй информационный выход первого регистра соединен с вто- рым входом первого элемента И, первый iiнфopмaциoнный выход регистра соединен с нулевым входом первого триггера и тактовым входом второго триггера, выход первого элемента ИЛИ через выходную шину синхронизации устройства соединен с выходом второго элемента ИЛИ, нулевым входом второго триггера и первым входом третьего элемента ЕПИ, выход которого сое- динен с тактовым входом первого .триггера, входная шина синхронизации соединена с вторым входом третьего

10

0

, -п5

элемента ИЛИ, первыми входами второго элемента И, второго и четвертого элементов ИЛИ и выходами четвертого и пятого элементов ИЛИ, вьгх;од блока сравнения соединен с первым входом пятого элемента ИЛИ, третий вькод блока памяти переадресации соединен с вторым входом пятого элемента ИЛИ, информационные входы первого и второго триггеров соединены с шиной нулевого потенциала устройства, единичный выход первого триггера соединен с втор,ым входом второго элемента И, вькод которого соединен с первым входом первого элемента ИЛИ, нулевой выход первого триггера соединен с вторым входом четвертого элемента ИЛИ и первым входом третьего элемента И, выход которого соединен с вторым входом первого элемента РШИ, единичный выход второго триггера соединен с вторыми входами третьего элемента И и второго элемента ИЛИ, нулевой выход второго триггера соединен с четвертым информационным входом коммутатора управляющих сигналов, третий и четвертый информационные выходы первого регистра соединены соответственно с третьими входами первого и второго элементов ИЛИ.

2. Устройство по п. 1, о т л и - чающ-ееся тем, что блок синхронизации содержит первьй и второй элементы И, триггер и счетчик, причем адресные входы, первый,второй и третий тактовые входы блока синхронизации соединены соответственно с группой входов первого элемента И, первьм и вторым входам первого элемента И и счетным входом счетчика,

информационные выходы которого соединены с входами второго элемента И, выход которого соединен с входом синхронизации триггера и первым выходом блока синхронизации выход первого элемента И соединен с единичным входом триггера и является тактовым выходом блока синхронизации, информационный вход триггера соединен с шиной нулевого потенциала, а нулевой выход триггера - с входом начальной установки счетчика.

I N.

В кодная шина синхронизации

65

М 57

М

Фа.гМ

Фиг.1У

iPue.3

Составитель И.Сигалов Редактор Н.Гунько Техред М.Ходанич Корректор М.Максимишинец

Заказ 3707/49 Тираж 671Подписное

ВНРВДПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5,

Производственно-полиграфическое предприятие,, г. Ужгород, ул. Проектная, 4

С

Конец

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

Изобретение относится к вычис-, лительной технике и может быть ис- пользованб при создании микроЭВМ на основе микропроцессоров.Цель изобретения - расширение области использования и повьшение достоверности отладки. Устройство содержит коммутатор адреса, блок памяти переадресации, блок синхронизации, счетчик, блоки памяти адресов и данных, элемент 2И-Ш1И, регистр, три группы элементов И, дешифратор, коммутатор управляющих сигналов, блок сравнения счетчик,- три триггера, пять элементов И и пять элементов ИЛИ. 1 з.п. ф-лы, 3 ил. о € 1чЭ М ЧЭ СО Од еп

| Справочник по цифровой вычислительной технике | |||

| Под ред | |||

| Б.Н.Малиновского | |||

| Техника, 1981, т | |||

| III, с | |||

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Microcomputer System Data Book , Santa | |||

| Inte Corp | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1986-07-07—Публикация

1983-08-30—Подача