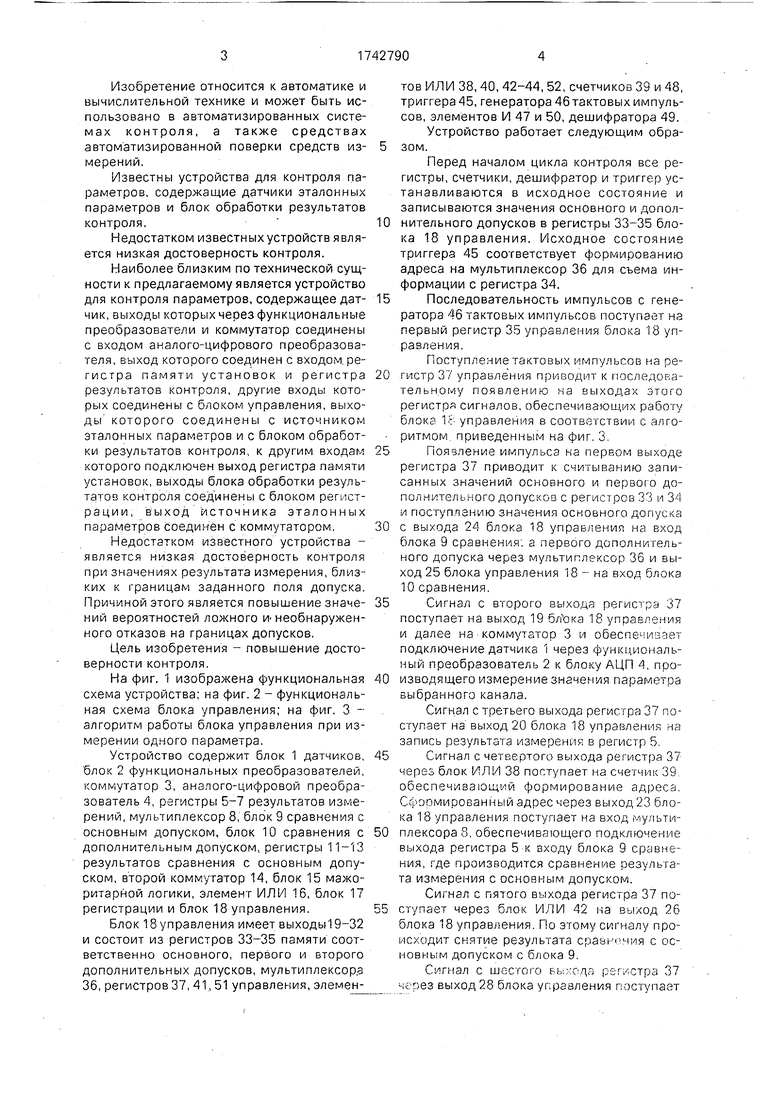

Фиг.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах контроля, а также средствах автоматизированной поверки средств из- мерений.

Известны устройства для контроля параметров, содержащие датчики эталонных параметров и блок обработки результатов контроля.

Недостатком известных устройств является низкая достоверность контроля.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля параметров, содержащее дат- чик, выходы которых через функциональные преобразователи и коммутатор соединены с входом аналого-цифрового преобразователя, выход которого соединен с входом регистра памяти установок и регистра результатов контроля, другие входы которых соединены с блоком управления, выходы которого соединены с источником эталонных параметров и с блоком обработки результатов контроля, к другим входам которого подключен выход регистра памяти установок, выходы блока обработки результатов контроля соединены с блоком реглет- рации, выход источника эталонных параметров соединен с коммутатором.

Недостатком известного устройства - является низкая достоверность контроля при значениях результата измерения, близких к границам заданного поля допуска. Причиной этого является повышение значе- ний вероятностей ложного № необнаруженного отказов на границах допусков.

Цель изобретения - повышение достоверности контроля.

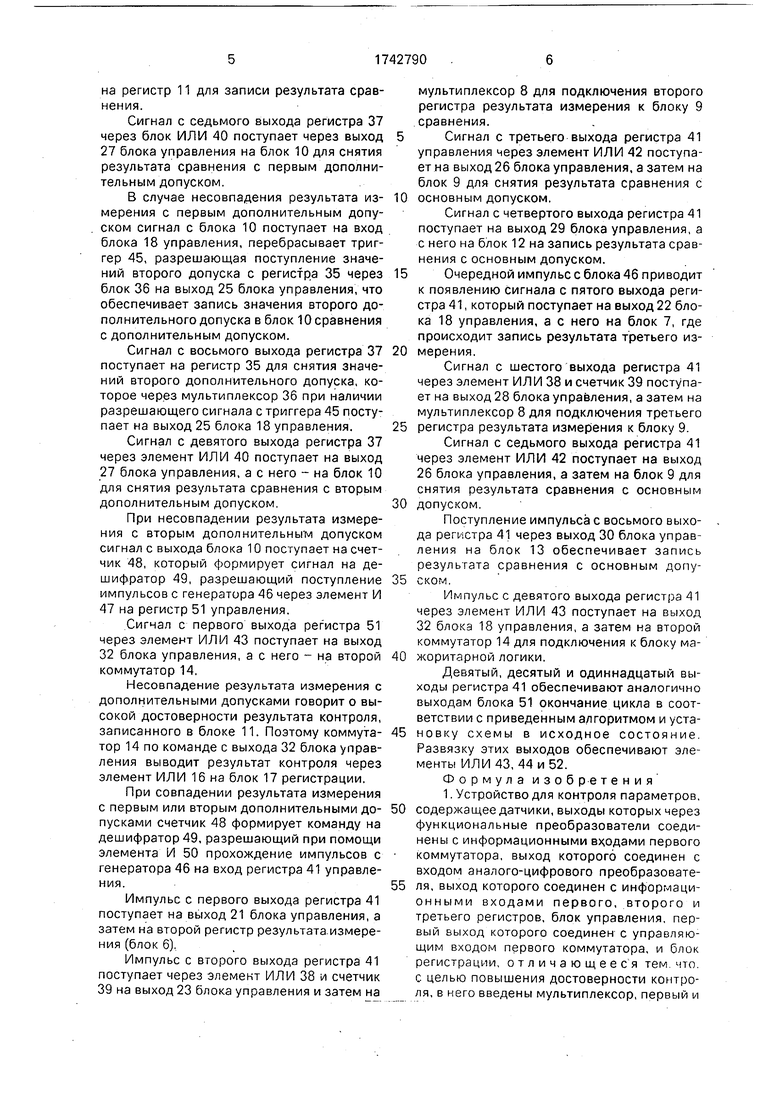

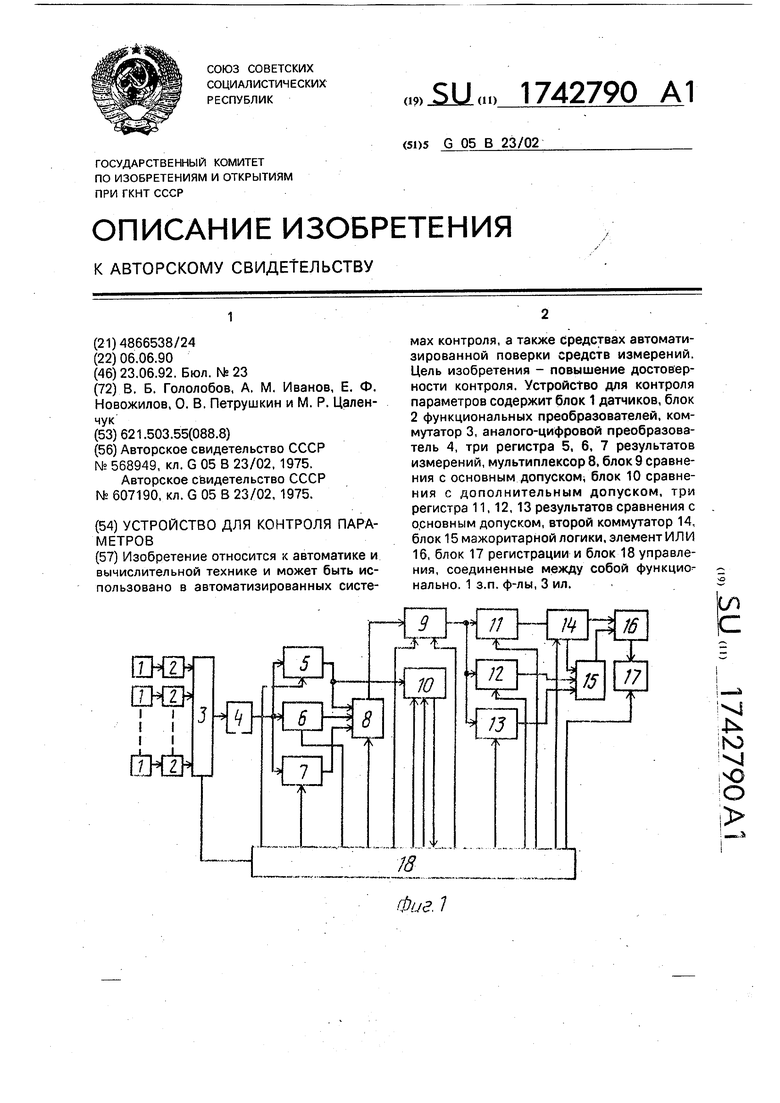

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - алгоритм работы блока управления при измерении одного параметра.

Устройство содержит блок 1 датчиков, блок 2 функциональных преобразователей, коммутатор 3, аналого-цифровой преобразователь 4, регистры 5-7 результатов измерений, мультиплексор 8, блок 9 сравнения с основным допуском, блок 10 сравнения с дополнительным допуском, регистры 11-13 результатов сравнения с основным допуском, второй коммутатор 14, блок 15 мажоритарной логики, элемент ИЛИ 16, блок 17 регистрации и блок 18 управления.

Блок 18 управления имеет выходы19-32 и состоит из регистров 33-35 памяти соответственно основного, первого и второго дополнительных допусков, мультиплексора 36, регистров 37, 41, 51 управления, элементов ИЛИ 38, 40, 42-44, 52, счетчиков 39 и 48, триггера 45, генератора 46 тактовых импульсов, элементов И 47 и 50, дешифратора 49.

Устройство работает следующим образом.

Перед началом цикла контроля все регистры, счетчики, дешифратор и триггер устанавливаются в исходное состояние и записываются значения основного и дополнительного допусков в регистры 33-35 блока 18 управления. Исходное состояние триггера 45 соответствует формированию адреса на мультиплексор 36 для съема информации с регистра 34.

Последовательность импульсов с генератора 46 тактовых импульсов поступает на первый регистр 35 управления блока 18 управления.

Поступление тактовых импульсов на регистр 37 управления приводит к последовательному появлению на выходах этого регистра сигналов, обеспечивающих работу блоке1 г управления в соответствии с апго- ритмом приведенным на фиг. 3

Появление импульса ьз первом выходе регистра 37 приводит к считыванию записанных значений основного и первою дополнительного допусков с регистров 33 и 34 и поступлению значения основного допуска с выхода 24 блока 18 управления на вход блока 9 сравнения, а первого дополнительного допуска через мультиплексор 36 и выход 25 блока управления 18 - на вход блока 10 сравнения.

Сигнал с второго выхода регистра 61 поступает на выход 19 блЪка 18 управления и далее на коммутатор 3 и обеспе1 и ззел подключение датчика 1 через функциональный преобразователь 2 к блоку АЦП 4, производящего измерение значения параметра выбранного канала.

Сигнал с третьего выхода регистра 37 го- ступает на выход 20 блока 18 управления на запись результата измерения в регистр 5

Сигнал с четвертого выхода регистра 37 через блок ИЛИ 38 поступает на счетчик 39 обеспечивающий формирование адреса Сооомированный адрес через выход 23 блока 18 управления поступает на вход мультиплексора 8, обеспечивающего подключение выхода регистра 5 к входу блока 9 сравнения, где производится сравнение резупьга- та измерения с основным допуском.

Сигнал с пятого выхода регистра 37 поступает через блок ИЛИ 42 на выход 26 блока 18 управления. По этому сигналу про- ислодит снятие результата сравп чия с основным допуском с блока 9.

Сигнал с шестого вь г да рсг/стра 37 чс оез выход 28 блока управления поступает

на регистр 11 для записи результата сравнения.

Сигнал с седьмого выхода регистра 37 через блок ИЛИ 40 поступает через выход 27 блока управления на блок 10 для снятия результата сравнения с первым дополнительным допуском.

В случае несовпадения результата измерения с первым дополнительным допуском сигнал с блока 10 поступает на вход блока 18 управления, перебрасывает триггер 45, разрешающая поступление значений второго допуска с perncfpa 35 через блок 36 на выход 25 блока управления, что обеспечивает запись значения второго дополнительного допуска в блок 10 сравнения с дополнительным допуском.

Сигнал с восьмого выхода регистра 37 поступает на регистр 35 для снятия значений второго дополнительного допуска, которое через мультиплексор 36 при наличии разрешающего сигнала с триггера 45 поступает на выход 25 блока 18 управления.

Сигнал с девятого выхода регистра 37 через элемент ИЛИ 40 поступает на выход 27 блока управления, а с него - на блок 10 для снятия результата сравнения с вторым дополнительным допуском.

При несовпадении результата измерения с вторым дополнительным допуском сигнал с выхода блока 10 поступает на счетчик 48, который формирует сигнал на дешифратор 49, разрешающий поступление импульсов с генератора 46 через элемент И 47 на регистр 51 управления.

Сигнал с первого выхода регистра 51 через элемент ИЛИ 43 поступает на выход 32 блока управления, а с него - на второй коммутатор 14.

Несовпадение результата измерения с дополнительными допусками говорит о высокой достоверности результата контроля, записанного в блоке 11. Поэтому коммутатор 14 по команде с выхода 32 блока управления выводит результат контроля через элемент ИЛИ 16 на блок 17 регистрации.

При совпадении результата измерения с первым или вторым дополнительными допусками счетчик 48 формирует команду на дешифратор 49, разрешающий при помощи элемента И 50 прохождение импульсов с генератора 46 на вход регистра 41 управления.

Импульс с первого выхода регистра 41 поступает на выход 21 блока управления, а затем на второй регистр результата измерения (блок 6).

Импульс с второго выхода регистра 41 поступает через элемент ИЛИ 38 и счетчик 39 на выход 23 блока управления и затем на

мультиплексор 8 для подключения второго регистра результата измерения к блоку 9 сравнения.

Сигнал с третьего выхода регистра 41

управления через элемент ИЛИ 42 поступает на выход 26 блока управления, а затем на блок 9 для снятия результата сравнения с

0 основным допуском.

Сигнал с четвертого выхода регистра 41 поступает на выход 29 блока управления, а с него на блок 12 на запись результата сравнения с основным допуском.

5 Очередной импульс с блока 46 приводит к появлению сигнала с пятого выхода регистра 41, который поступает на выход 22 блока 18 управления, а с него на блок 7, где происходит запись результата третьего из0 мерения.

Сигнал с шестого выхода регистра 41 через элемент ИЛИ 38 и счетчик 39 поступает на выход 28 блока управления, а затем на мультиплексор 8 для подключения третьего

5 регистра результата измерения к блоку 9.

Сигнал с седьмого выхода регистра 41 через элемент ИЛИ 42 поступает на выход 26 блока управления, а затем на блок 9 для снятия результата сравнения с основным

0 допуском.

Поступление импульса с восьмого выхода регистра 41 через выход 30 блока управления на блок 13 обеспечивает запись результата сравнения с основным допу5 ском.

Импульс с девятого выхода регистра 41 через элемент ИЛИ 43 поступает на выход 32 блока 18 управления, а затем на второй коммутатор 14 для подключения к блоку ма0 жоритарной логики.

Девятый, десятый и одиннадцатый выходы регистра 41 обеспечивают аналогично выходам блока 51 окончание цикла в соответствии с приведенным алгоритмом и уста5 новку схемы в исходное состояние Развязку этих выходов обеспечивают элементы ИЛИ 43, 44 и 52.

Формула изобретения

1. Устройство для контроля параметров,

0 содержащее датчики, выходы которых через функциональные преобразователи соединены с информационными входами первого коммутатора, выход которого соединен с входом аналого-цифрового преобразовате5 ля, выход которого соединен с информационными входами первого, второго и третьего регистров, блок управления, первый выход которого соединен с управляющим входом первого коммутатора, и блок регистрации, отличающееся тем что с целью повышения достоверности контроля, в него введены мультиплексор, первый и

второй блоки сравнения, четвертый, пятый и шестой регистры, второй коммутатор, блок мажоритарной логики и элемент ИЛИ, причем второй, третий и четвертый выходы блока управления соединены соответственно с входами разрешения записи первого, второго и третьего регистров, выходы которых соединены соответственно с первым, вторым и третьим информационными входами мультиплексора, управляющий вход которого соединен с пятым выходом блока управления, а выход мультиплексора соединен с первым информационным входом первого блока сравнения, второй информационный вход которого соединен с шестым выходом блока управления, выход первого регистра соединен с первым информационным входом второго блока сравнения, второй информационный вход которого соединен с седьмым выходом блока управления, восьмой и девятый выходы которого соединены соответственно с управляющими входами первого и второго блоков сравнения, выход второго блока сравнения соединен с входом блока управления, десятый, одиннадцатый и двенадцатый выходы которого соединены соответственно с входами разрешения записи четвертого, пятогс и шестого регистров, информационные входы которых соединены с выходом первого блока сравнения, выход четвертого регистра соединен с информационным входом второго коммутатора, первый выход которого соединен с первым входом блока мажоритарной логики, второй и третий входы которого соединены соответственно с выходами пятого и шестого регистров, второй выход второго коммутатора соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока мажоритарной логики, выход элемента ИЛИ соединен с информационным входом блока регистрации, управляющий вход которого соединен с тринадцатым выходом блока управления, четырнадцатый выход которого соединен с управляющим входом второго коммутатора.

2, Устройство по п. 1, отличающее- с я тем, что блок управления содержит регистр значений основного допуска, первый и второй регистры значений дополнительного допуска, мультиплексор, первый, второй и третий регистры управления, триггер, дешифратор, первый и второй счетчики, генератор тактовых импульсов, псгрвый и второй элементы И, первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, причем выход генератора тактовых импульсов соединен с тактовым входом первого

регистра управления и с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторым выходами дешифратора,

выход первого элемента И соединен с тактовым входом второго регистра управления, выход второго элемента И соединен с тактовым входом третьего регистра управления, вход дешифратора соединен с выходом пер0 вого счетчика, счетный вход которого соединен с входом блока управления и с установочным входом триггера, выход которого соединен с управляющим входом муль- типлексора, выход которого является

5 седьмым выходом блока управления, первый и второй информационные входы мультиплексора соединены соответственно с выходами первого и второго регистров значений дополнительного допуска, первый вы0 ход первого регистра управления соединен с входами разрешения считывания регистра значений основного допуска и первого регистра значений дополнительного допуска, выход регистра основного допуска является

5 шестым выходом блока управления, первый выход которого соединен с вторым выходом первого регистра управления, третий выход которого является вторым выходом блока управления, четвертый выход первого реги0 стра управления соединен с первым входом первого элемента ИЛИ, пятый выход первого регистра управления соединен с первым входом третьего элемента ИЛИ, шестой выход первого регистра управления является

5 десятым выходом блока управления, седьмой выход первого регистра управления соединен с первым входом второго элемента ИЛИ, восьмой выход первого регистра управления соединен с входом разрешения

0 считывания второго регистра значений дополнительного допуска, девятый выход первого регистра управления соединен с вторым входом второго элемента ИЛИ, выход которого является девятым выходом

С блок управления, третий выход которого соединен с первым выходом второго регистра управления, второй выход которого соединен с вторым входом первого элемента ИЛИ, третий выход второго регистра управ0 лень соединен с вторым входом третьего элемента ИЛИ, четвертый и пятый выходы второго регистра управления являются соответственно одиннадцатым и четвертым выходами блока управления, шестой выход

5 второго регистра управления соединен с третьим входом первого элемента ИЛИ, выход которого соединрч со счэтн входом второго счетчика, выход которою является , я ГУМ выходом блока угрчвлэни, седьмой выход второго регистре1 управления соединек с третьим входом третьего элемента ИЛИ, выход которого является восьмым выходом блока управления, двенадцатый выход которого соединен с восьмым выходом второго регистра управления, девятый, десятый и одиннадцатый выходы которого со- единены соответственно с первыми входами четвертого, пятого и шестого элементов ИЛИ, вторые входы которых соеди0

нены соответственно с первым, вторым и третьим выходами третьего регистра управления, выход четвертого элемента ИЛИ является четырнадцатым выходом блока управления, тринадцатый выход которого соединен с выходом пятого элемента ИЛИ, а выход шестого элемента ИЛИ является выходом внутренней установки блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Многоканальное устройство для обмена данными микропроцессорной системы | 1985 |

|

SU1264193A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Информационно-измерительное устройство | 1983 |

|

SU1088111A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах контроля, а также средствах автоматизированной поверки средств измерений. Цель изобретения - повышение достоверности контроля. Устройство для контроля параметров содержит блок 1 датчиков, блок 2 функциональных преобразователей, коммутатор 3, аналого-цифровой преобразователь 4, три регистра 5, 6, 7 результатов измерений, мультиплексор 8, блок 9 сравнения с основным допуском, блок 10 сравнения с дополнительным допуском, три регистра 11,12,13 результатов сравнения с о.сновным допуском, второй коммутатор 14, блок 15 мажоритарной логики, элемент ИЛ И 16, блок 17 регистрации и блок 18 управления, соединенные между собой функционально. 1 з.п. ф-лы, 3 ил.

21 26 29 22 30 32

3/

(I

J

Фиг. 2.

о

| Устройство для контроля параметров | 1975 |

|

SU568949A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля параметров | 1975 |

|

SU607190A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-06-23—Публикация

1990-06-06—Подача