±

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования двоичных кодов при трехкратном повторении сообщений | 1986 |

|

SU1345357A2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для воспроизведения цифровых сообщений | 1989 |

|

SU1638730A1 |

| Декодер сверточного кода | 1988 |

|

SU1660178A1 |

| Цифровой демодулятор сигналов с двухуровневой амплитудно-фазовой манипуляцией и относительной оценкой амплитуды символа | 2022 |

|

RU2790140C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2023348C1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

Изобретение относится к цифровой технике, в частности к логическим решающим устройствам, и может быть использовано в устройствах приема и обработки дискретных сообщений. Цель изобретения - повышение достоверности устройства. Устройство содержит детектор 1 качества, блок 2 коррекции, блок 3 синхронизации, счетчик 4 символов, регистр 5, элементы И 6-8, элемент ИЛИ 9, преобразователь 10 код-аналог. 1 з.п. ф-лы, 4 ил., 1 табл.

Ё

Х|

СО

о о со

ю

Изобретение относится к цифровой технике, в частности к логическим решающим устройствам, может быть использовано в устройствах приема и обработки дискретных сообщений и является усовершенствованием известного устройства по авт. св. № 1345357.

Известно устройство для декодирования двоичных кодов при трехкратном повторении сообщений, содержащее элементы ИЛИ, счетчик символов, первый, второй и третий элементы И, регистр, детектор качества, блок коррекции и блок синхронизации, тактовый вход которого соединен с тактовым входом устройства и тактовыми входами детектора качества, счетчика символов и регистра, первый и второй выходы которого подключены к первым входам соответственно первого и второго элементов И, два входа регистра являются управляющими входами устройства, выход старшего разряда счетчика символов подключен к второму входу первого элемента И и первому входу третьего элемента И, выходы первого, второго и третьего элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является выходом устройства, вход которого подключен к информационному входу детектора качества, первый и второй выходы которого под- ключены соответственно к первому и второму входам блока коррекции, три синх- ровхода которого соединены с соответствующими выходами блока синхронизации, а выход подключен к счетному входу счетчика символов, выход младшего разряда которого подключен к вторым входам второго и третьего элементов И и третьему входу блоха коррекции.

Недостатком известного устройства является низкая достоверность приема информациипривоздействиинестационарных помех, так как при вынесении решения детектором качества не учитывается имеющаяся информация о характере помех, действующих в данное время на принимаемые символы сигнала. Это приводит к росту вероятности необнаружения ошибки детектором качества и увеличение вероятности появления ложных стираний, что снижает достоверность приема информации устройства в целом.

Цель изобретения - повышение достоверности устройства.

Поставленная цель достигается тем, что в устройство для декодирования двоичных кодов при трехкратном повторении сообщений введен преобразователь код-аналог, выход которого подключен к управляющему

входу детектора качества, а входы подключены к управляющим входам устройства.

Детектор качества состоит из нормирующих усилителей, компараторов, элементов

НЕ, элементов И и источника опорного напряжения, выход которого соединен с первыми входами первого и второго нормирующих усилителей и через третий нормирующий усилитель - с первым входом

0 первого компаратора, выход которого соединен с первым входом первого элемента И, выходы второго и третьего нормирующих усилителей соединены с первыми входами соответственно второго и третьего компара5 торов, выход второго компаратора через элемент НЕ соединен с входом второго элемента И, выход третьего компаратора соединен с вторым входом второго элемента И, выходы первого и второго элементов И яв0 ляются выходами детектора качества, вторые входы компараторов объединены и являются информационным входом детектора качества, вторые входы второго и третьего нормирующих усилителей обьеди5 нены и являются управляющим входом детектора качества, второй вход первого элемента И и третий вход второго элемента И объединены и являются тактовым входом детектора качества.

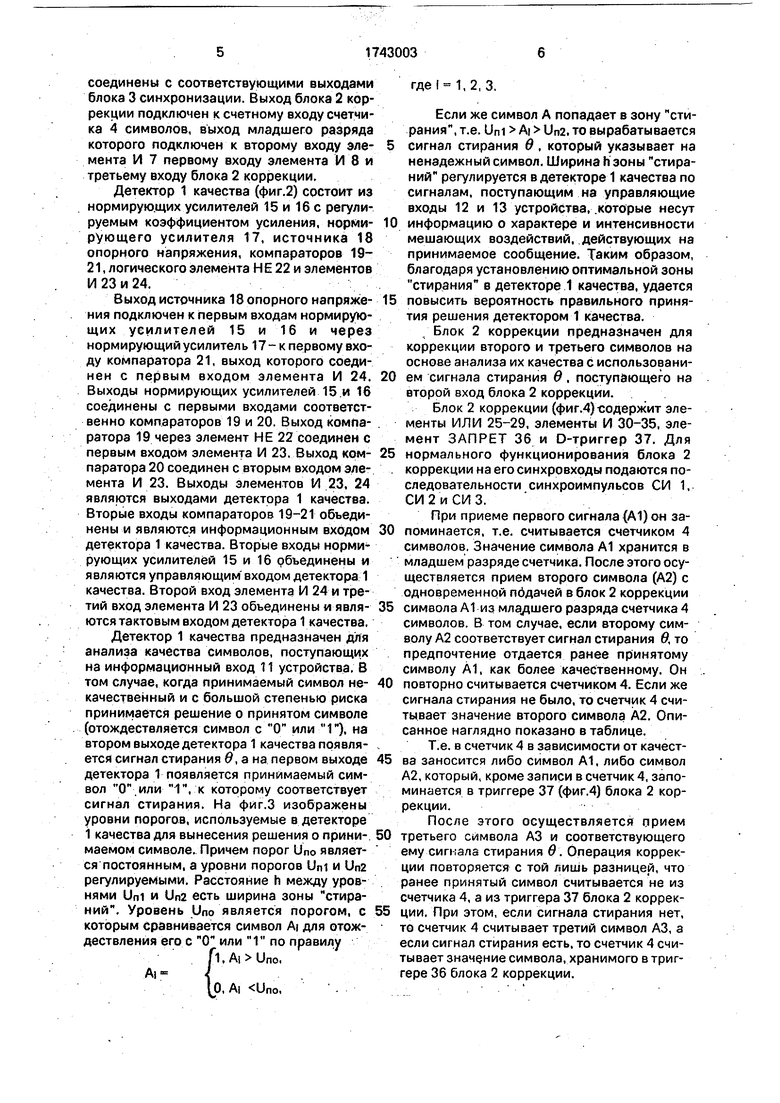

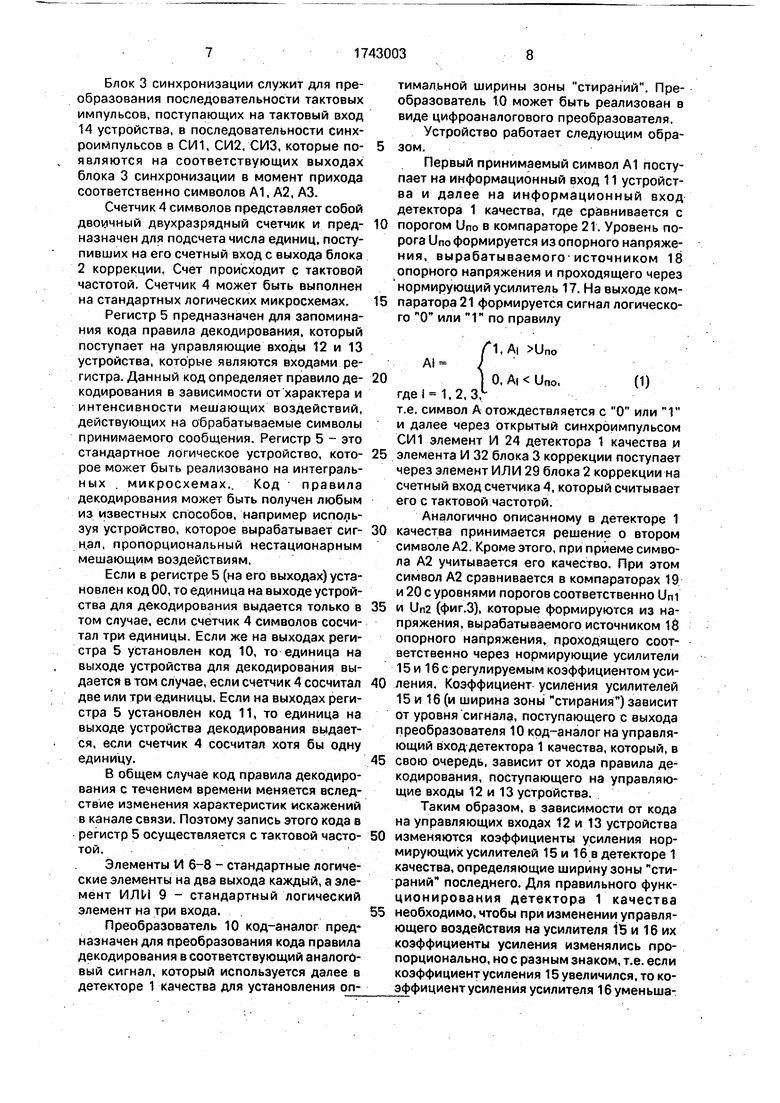

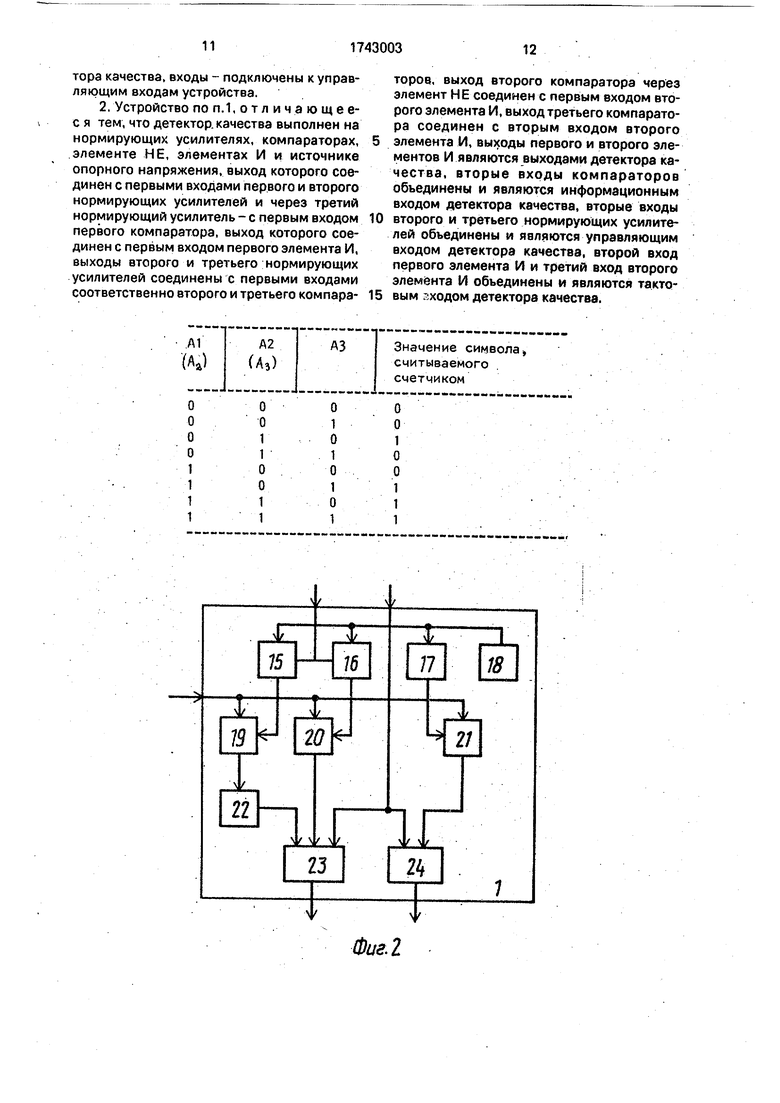

0 На фиг,1 представлена схема предлагаемого устройства; на фиг.2 - схема детектора качества; на фиг.З - график, поясняющий работу детектора качества; на фиг.4 - схема блока коррекции.

5 Устройство для декодирования двоичных кодов (фиг. 1) содержит детектор 1 качества, блок 2 коррекции, блок 3 синхронизации, счетчик 4 символов, регистр 5, элементы И 6-8, элемент ИЛИ 9,

0 преобразователь 10 код-аналог, информа-, ционный вход 11, управляющие входы 12 и 13 и тактовый вход 14. Причем тактовый вход 14 устройства подключен к тактовым входам блока 3 синхронизации, детектора 1

5 качества, счетчика 4 символов и регистра 5, первый и второй выходы которого подключены к первым входам соответственно элементов И 6 и 7. Два входа регистра 5 являются управляющим входами 12 и 13 ус0 тройства. Выход старшего разряда счетчика 4 символов подключен к второму входу элемента И 6 и второму входу элемента И 8. Выходы элементов И 6-8 подключены к входам элемента ИЛИ 9, выход которого явля5 ется выходом устройства. Вход 11 устройства подключен к информационному входу детектора 1 качества, первый и второй выходы которого подключены соответственно к первому и второму входам блока 2 кор- рекции, три синхровхода которого

соединены с соответствующими выходами блока 3 синхронизации. Выход блока 2 коррекции подключен к счетному входу счетчика 4 символов, выход младшего разряда которого подключен к второму входу элемента И 7 первому входу элемента И 8 и третьему входу блока 2 коррекции.

Детектор 1 качества (фиг.2) состоит из нормирующих усилителей 15 и 16с регулируемым коэффициентом усиления, нормирующего усилителя 17, источника 18 опорного напряжения, компараторов 19- 21, логического элемента НЕ 22 и элементов И 23 и 24.

Выход источника 18 опорного напряжения подключен к первым входам нормирующих усилителей 15 и 16 и через нормирующий усилитель 17- к первому входу компаратора 21, выход которого соединен с первым входом элемента И 24. Выходы нормирующих усилителей 15 и 16 соединены с первыми входами соответственно компараторов 19 и 20. Выход компаратора 19 через элемент НЕ 22 соединен с первым входом элемента И 23. Выход компаратора 20 соединен с вторым входом элемента И 23. Выходы элементов И 23, 24 являются выходами детектора 1 качества. Вторые входы компараторов 19-21 объединены и являются информационным входом детектора 1 качества. Вторые входы нормирующих усилителей 15 и 16 рбъединены и являются управляющим входом детектора 1 качества. Второй вход элемента И 24 и третий вход элемента И 23 объединены и являются тактовым входом детектора 1 качества.

Детектор 1 качества предназначен для анализа качества символов, поступающих на информационный вход 11 устройства. В том случае, когда принимаемый символ некачественный и с большой степенью риска принимается решение о принятом символе (отождествляется символ с О или 1), на втором выходе детектора 1 качества появляется сигнал стирания в, а на первом выходе детектора 1 появляется принимаемый символ О или 1м, к которому соответствует сигнал стирания. На фиг.З изображены уровни порогов, используемые в детекторе 1 качества для вынесения решения о принимаемом символе. Причем порог Uno является постоянным, а уровни порогов Uni и Un2 регулируемыми. Расстояние h между уровнями Uni и Un2 есть ширина зоны стираний. Уровень Uno является порогом, с которым сравнивается символ AI для отождествления его с О или 1 по правилу

Ар

fl,, (О, А| ипо,

где , 2,3.

Если же символ А попадает в зону стирания, т.е. Uni AI Un2. то вырабатывается 5 сигнал стирания в , который указывает на ненадежный символ. Ширина h зоны стираний регулируется в детекторе 1 качества по сигналам, поступающим на управляющие входы 12 и 13 устройства, которые несут

0 информацию о характере и интенсивности мешающих воздействий, действующих на принимаемое сообщение. Таким образом, благодаря установлению оптимальной зоны стирания в детекторе 1 качества, удается

5 повысить вероятность правильного принятия решения детектором 1 качества.

Блок 2 коррекции предназначен для коррекции второго и третьего символов на основе анализа их качества с использовани0 ем сигнала стирания в, поступающего на второй вход блока 2 коррекции.

Блок 2 коррекции (фиг.4) содержит элементы ИЛИ 25-29, элементы И 30-35, элемент ЗАПРЕТ 36 и D-триггер 37. Для

5 нормального функционирования блока 2 коррекции на его синхровходы подаются последовательности синхроимпульсов СИ 1, СИ 2 и СИ 3.

При приеме первого сигнала (А1) он за0 поминается, т.е. считывается счетчиком 4 символов. Значение символа А1 хранится в младшем разряде счетчика. После этого осуществляется прием второго символа (А2) с одновременной подачей в блок 2 коррекции

5 символа А1 из младшего разряда счетчика 4 символов. В том случае, если второму символу А2 соответствует сигнал стирания в, то предпочтение отдается ранее принятому символу А1, как более качественному. Он

0 повторно считывается счетчиком 4. Если же сигнала стирания не было, то счетчик 4 считывает значение второго символа А2. Описанное наглядно показано в таблице.

Т.е. в счетчик 4 в зависимости от качест5 ва заносится либо символ А1, либо символ А2, который, кроме записи в счетчик 4, запоминается в триггере 37 (фиг.4) блока 2 коррекции.

После этого осуществляется прием

0 третьего символа A3 и соответствующего ему сигнала стирания 9. Операция коррекции повторяется с той лишь разницей, что ранее принятый символ считывается не из счетчика 4, а из триггера 37 блока 2 коррек5 ции. При этом, если сигнала стирания нет, то счетчик 4 считывает третий символ A3, а если сигнал стирания есть, то счетчик 4 считывает значение символа, хранимого в триггере 36 блока 2 коррекции.

Блок 3 синхронизации служит для преобразования последовательности тактовых импульсов, поступающих на тактовый вход 14 устройства, в последовательности синхроимпульсов в СИ1, СИ2, СИЗ, которые появляются на соответствующих выходах блока 3 синхронизации в момент прихода соответственно символов А1, А2, A3.

Счетчик 4 символов представляет собой двоичный двухразрядный счетчик и предназначен для подсчета числа единиц, поступивших на его счетный вход с выхода блока 2 коррекции. Счет происходит с тактовой частотой. Счетчик 4 может быть выполнен на стандартных логических микросхемах.

Регистр 5 предназначен для запоминания кода правила декодирования, который поступает на управляющие входы 12 и 13 устройства, которые являются входами регистра. Данный код определяет правило декодирования в зависимости от характера и интенсивности мешающих воздействий, действующих на обрабатываемые символы принимаемого сообщения. Регистр 5 - это стандартное логическое устройство, которое может быть реализовано на интеграль- ных . микросхемах.. Код правила декодирования может быть получен любым из известных способов, например используя устройство, которое вырабатывает сигнал, пропорциональный нестационарным мешающим воздействиям.

Если в регистре 5 (на его выходах) установлен код 00, то единица на выходе устройства для декодирования выдается только в том случае, если счетчик 4 символов сосчитал три единицы. Если же на выходах регистра 5 установлен код 10, то единица на выходе устройства для декодирования выдается в том случае, если счетчик 4 сосчитал две или три единицы. Если на выходах регистра 5 установлен код 11, то единица на выходе устройства декодирования выдается, если счетчик 4 сосчитал хотя бы одну единицу.

В общем случае код правила декодирования с течением времени меняется вследствие изменения характеристик искажений в канале связи. Поэтому запись этого кода в регистр 5 осуществляется с тактовой частотой.

Элементы И 6-8 - стандартные логические элементы на два выхода каждый, а элемент ИЛИ 9 - стандартный логический элемент на три входа.

Преобразователь 10 код-аналог пред назначен для преобразования кода правила декодирования в соответствующий аналоговый сигнал, который используется далее в детекторе 1 качества для установления оптимальной ширины зоны стираний. Преобразователь 10 может быть реализован в виде цифроаналогового преобразователя. Устройство работает следующим образом.

Первый принимаемый символ А1 поступает на информационный вход 11 устройства и далее на информационный вход детектора 1 качества, где сравнивается с

порогом Uno в компараторе 21. Уровень порога Uno формируется из опорного напряжения, вырабатываемого-источником 18 опорного напряжения и проходящего через нормирующий усилитель 17. На выходе компарзтора 21 формируется сигнал логического О или 1 по правилу

А

1,A| Uno

1 0, Ai Uno,(1)

где 1 1.2, 3,L т.е. символ А отождествляется с О или 1 и далее через открытый синхроимпульсом СИ1 элемент И 24 детектора 1 качества и

элемента И 32 блока 3 коррекции поступает через элемент ИЛИ 29 блока 2 коррекции на счетный вход счетчика 4, который считывает его с тактовой частотой.

Аналогично описанному в детекторе 1

качества принимается решение о втором символе А2. Кроме этого, при приеме символа А2 учитывается его качество. При этом символ А2 сравнивается в компараторах 19 и 20 с уровнями порогов соответственно Uni

и Un2 (фиг.З), которые формируются из напряжения, вырабатываемого источником 18 опорного напряжения проходящего соответственно через нормирующие усилители 15 и 1 б с регулируемым коэффициентом усиления. Коэффициент усиления усилителей 15 и 16 (и ширина зоны стирания) зависит от уровня сигнала, поступающего с выхода преобразователя 10 код-аналог на управляющий вход-детектора 1 качества, который, в

свою очередь, зависит от хода правила декодирования, поступающего на управляющие входы 12 и 13 устройства.

Таким образом, в зависимости от кода на управляющих входах 12 и 13 устройства

изменяются коэффициенты усиления нормирующих усилителей 15 и 16 в детекторе 1 качества, определяющие ширину зоны стираний последнего. Для правильного функционирования детектора 1 качества

необходимо, чтобы при изменении управляющего воздействия на усилителя 15 и 16 их коэффициенты усиления изменялись пропорционально, нос разным знаком, т.е. если коэффициент усиления 15 увеличился, то ко- эффициент усиления усилителя 16 уменьшается на такую же величину. Это сделать несложно, применив в этих усилителях, например, транзисторы с различным типом проводимости и одинаковыми параметрами. Таким образом, уровни Uni и Un2 всегда находятся на одинаковом расстоянии от Uno, что важно для обеспечения минимума среднего риска при принятии решения о качестве символа, и, в то же время, расстояние h может быть различным в зависимости от управляющего воздействия, что позволяет оптимизировать ширину зоны стираний h.

По результатам сравнения символа А2 с уровнями порогов Uni и Un2 компараторы 19 и 20 вырабатывают сигнал логического О или 1 по правилу (1). Этот сигнал с выхода компаратора 19 инвертируется в элементе НЕ 22 и поступает на первый вход элемента И 23, на второй вход которого поступает сигнал непосредственное выхода компаратора 20. Таким образом, на первом и втором входах элемента И 23 только тогда будут сигналы логической 1, когда Uni AI 1)П2, т.е. символ входит в область стирания.

Сигнал стирания # поступает на выход детектора 1 качества с приходом на тактовый вход соответствующего синхроимпульса. С приходом второго символа А2 символ А1 с выхода младшего разряда счетчика 4 символов поступает через элемент 30 (фиг.4), открытый синхроимпульсом СИ2, на вход элемента ИЛИ и далее на вход элемента И 35, На элементах ЗАПРЕТ 36 и И 35 выполнена непосредственно схема коррекции. Сам символ А2 через элемент И, открытый СИ2, проходящими через ИЛИ, поступает на прямой вход элемента ЗАПРЕТ 36. Если символу А2 не соответствует сигнал стирания в (символ А2 качественный), то сигнал стирания равен нулю (0 0), он подается на инверсный вход элемента ЗАПРЕТ 36 и вход элемента И 35. Через элемент ЗАПРЕТ пройдет символ второго повторения А2, который через элементы ИЛИ 28 и 29 поступает на счетный вход счетчика 4 и считывается. Одновременно с этим с частотой СИ2 происходит его запись в D-триггер 37, Если же сигналу А2 соответствует сигнал стирания (0 1), то через элемент И 35 пройдет более качественный символ А1, который через элементы ИЛИ 28 и 29 сосчитаемая счетчиком 4 и запишется в D-триггер 37, Счет ведется с тактовой частотой.

С приходом третьего символа A3 он через И 33, открытый СИЗ, проходящими через элемент ИЛИ 25, поступает на прямой вход элемента ЗАПРЕТ. Одновременно с этим через элемент И 31, открытый СИЗ, и

далее через элемент ИЛИ на вход И 35 поступает ранее принятый символ (либо А1, либо А2 в зависимости от коррекции). Если символу A3 соответствует сигнал стирания, 5 то через элементы И 35, ИЛИ 28 и 29 счетчик 4 сосчитает содержимое триггера 37. Если же сигнала стирания не было, то символ A3 считается качественным, т.е. пригодным к дальнейшей обработке, и через элементы

10 ЗАПРЕТ 36, ИЛИ 28 и 29 считывается счетчиком 4.

Таким образом, после приема трех символов в счетчике 4 хранится код числа единиц в этих символах. В регистре 5 записан

15 код правила декодирования.

Если на входах первого и второго разрядов регистра 5 присутствует код 00, то на выходах элементо в И 6 и 7 сигналы равны нулю. Третий элемент И 8 выдает сигнал,

0 равный единице, только при наличии двух единиц на его входах, т.е. если счетчик 4 сосчитал три единицы. Сигнал с выхода третьего элемента И 8 через элемент ИЛИ 9 поступает на выход устройства для декоди5 рования. Таким образом, при коде 00 на выходах регистра 5 реализуется правило декодирования, при котором единица на выходе устройства для декодирования выдается только тогда, если счетчик 4 симво0 лов сосчитал три единицы.

Если на выходах регистра 5 установлен код 10, сигнал на выходе второго элемента И 7 присутствует при наличии единицы на выходе старшего разряда счетчика 4, т.е. если

5 счетчик 4 сосчитал две или три единицы.

Если на выходах регистра 5 установлен код 11, на выходе элемента И 7 единица будет в том случае, если счетчик сосчитал одну единицу на выходе элемента И 6 еди0 ница будет, если счетчик сосчитал две или три единицы. Этот сигнал через элемент ИЛИ 9 поступает на выход устройства. Таким образом, при коде 11 реализуется правило декодирования, при котором единица

5 на выходе устройства для декодирования выдается тогда, когда счетчик 4 символов сосчитал одну, две или три единицы.

При приеме последующего трижды повторенного символа В1, В2, ВЗ последова0 тельность действий полностью аналогична.

Ф о р м у л а и з о б р е т е н и я

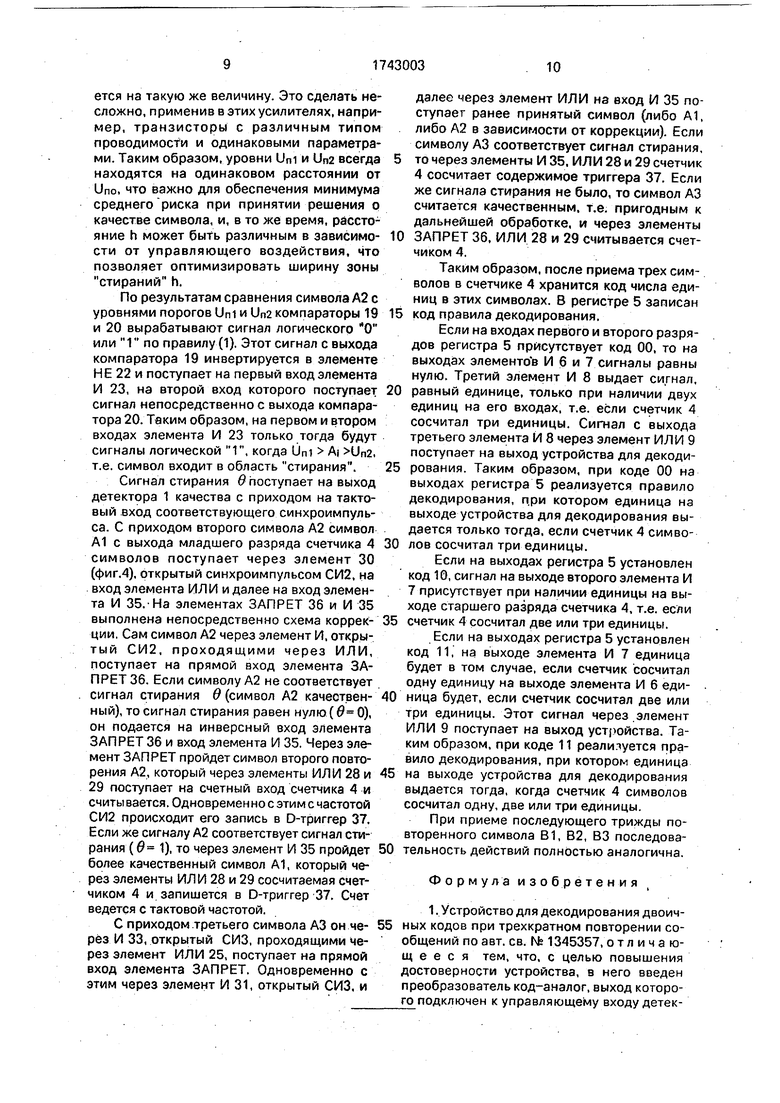

о о 1 1 о о 1 1

о 1 о 1 о 1

о 1

5

торов, выход второго компаратора через элемент НЕ соединен с первым входом второго элемента И, выход третьего компаратора соединен с вторым входом второго элемента И, выходы первого и второго элементов И являются выходами детектора качества, вторые входы компараторов объединены и являются информационным входом детектора качества, вторые входы второго и третьего нормирующих усилителей объединены и являются управляющим входом детектора качества, второй вход первого элемента И и третий вход второго элемента И объединены и являются тактовым -ходом детектора качества.

о о 1 о о 1 1 1

Фиг. 2

шг,м

Фиг.Ь

| Устройство для декодирования двоичных кодов при трехкратном повторении сообщений | 1986 |

|

SU1345357A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-23—Публикация

1990-02-27—Подача