Изобретение относится к технике воспроизведения цифровых сообщений и может быть использовано в каналах воспроизведения цифровой информации, например в составе запоминающих устройств с движущимся носителем.

Цель изобретения - повышение достоверности воспроизведения информации.

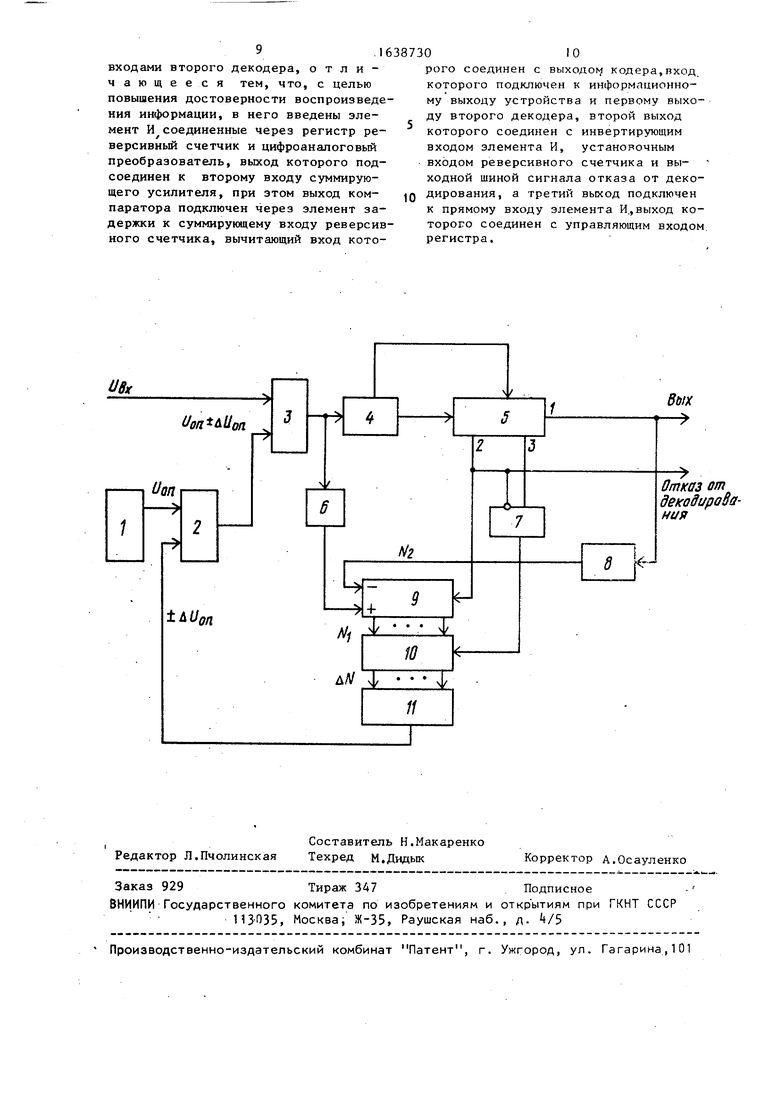

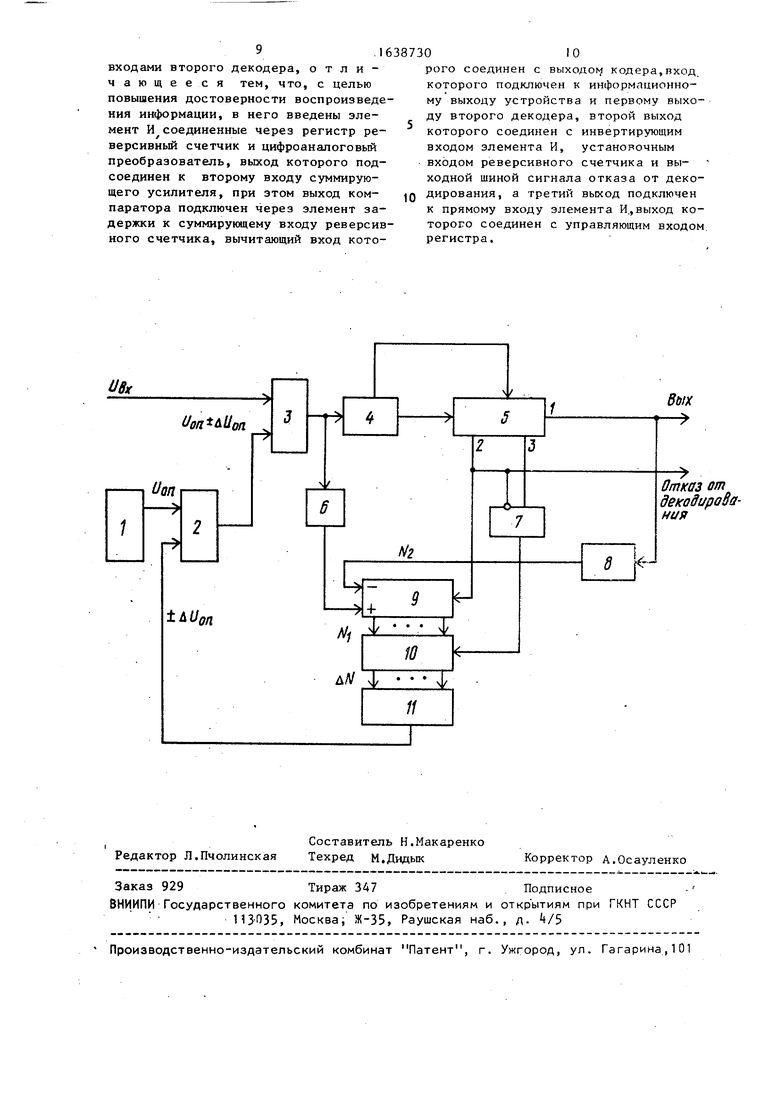

На чертеже представлена структурная электрическая схема устрой- ства для воспроизведения цифровых сообщений.

Устройство содержит источник 1 опорного напряжения, суммирующий усилитель 2, компаратор 3, первый 4 и второй 5 декодеры, элемент 6 задержки, элемент И 7, кодер 8, реверсив- ный счетчик 9, регистр 10 и цифро- аналоговый преобразователь 11. Выход источника 1 опорного напряжения подключен к первому входу суммирующего усилителя 2, выход которого подсоединен к второму входу компаратора 3, первый вход которого соединен с информационным входом устройства. Выход компаратора 3 соединен с входом первого декодера 4, первый и второй выходы которого связаны соответственно с информационным и маркирующим входами второго декодера 5. Раз- рядные выходы реверсивного счетчика 9 через регистр 10 соединены с разрядными входами цифроаналогового преобразователя 11, выход которого связан с вторым входом суммирующего усилителя 2. Выход компаратора 3 через элемент б задержки соединен с суммирующим входом реверсивного счетчика 9, вычитающий вход которого соединен с выходом кодера 8. Второй де- кодер 5 имеет три Выхода, Первый его выход соединен с информационным выходом устройства и входом кодера .в. Второй вход соединен с инвертирую щим входом элемента И 7, установоч- ным входом реверсивного счетчика 9 и выходом сигнала отказа от декодирования устройства. Третий выход подключен к прямому входу элемента И 7 выход которого подключен к управляю- щему входу регистра 10.

Устройство работает следующим образом.

Устройство работает в условиях, когда при записи и воспроизведении информации используется избыточный корректирующий блоковый код. Воспроизведенный с носителя и усиленный сигнал двоичной информации UBX посту пает на первый вход компаратора 3, на второй вход которого поступает скорректированный опорный уровень Uon±UUQn с выхода суммирующего усилителя 2, на входы которого пос- тупают сигнал опорного уровня Uotl с выхода источника 1 опорного напряжения и сигнал коррекции опорного уровня ± Uon с выхода цийроаналого- вого преобразователя 11. На выходе компаратора 3 формируется двоичная последовательность избыточного канального кода.

В избыточном канальном коде, на- пример коде (10,3), восьмибитовая комбинация (байт), представляющая собой один символ, преобразуется в избыточную кодовую последовательность, состоящую из десяти битов, записывается на носитель информации или воспроизводится с него.

Двоичная последовательность с выхода компаратора 3 поступает на вход первого декодера 4, в котором осуществляется преобразование последовательного кода в параллельный, а также производится преобразование избыточного кода в неизбыточный (например, десятиразрядного кода в восьмиразрядный) и обнаружение в символе некоторых ошибок (стираний), которые фиксируются как стирания. Если в сигнале стирания нет, то на первом выходе первого декодера 4 преобразованный код подается на информационный вход второго декодера 5. При обнаружении первым декодером 4 стирания на его первом выходе формируются нулевые элементы кода, а на втором выходе - маркирующий сигнал, который подается на маркирующий вход второго декодера 5. Второй декодер 5 работает с кодовыми блоками. После накопления в нем кодового блока, комбинации которого являются элементами конечного поля Галуа, закодированные с помощью блокового кода (И, К), например кода Рида-Соломона, второй декодер 5 на основании вычисления и анализа синдромов и учета маркирующих сигналов исправляет в кодовом блоке возможные ошибки и стирания и выдает информацию на выход устройства.

Для исправления пакетов ошибок второй декодер 5 может быть построен с учетом применения различных законов перемещения кодовых блоков.

Если кратность ошибок и стираний выше корректирующей способности кода то второй декодер 5 выдает сигнал отказа от декодирования, и весь декодируемый блок пропускается. Этим предлагаемое устройство выгодно отличается от прототипа, так как обнаруженные, но неисправленные ошибки на выход устройства не передаются. Остальные блоки устройства используются для формирования сигнала коррекции опорного уровня следующим образом.

С выхода компаратора 3 воспроизведенная двоичная последовательность сигналов через элемент 6 задержки подается на суммирующий вход реверсивного счетчика 9. Одновременно с выхода устройства исправленная информация подается на вход кодера 8,который производит обратное первому декодеру 4 преобразование параллельного неизбыточного кода в последовательный избыточный канальный код (например, восмиразрядного в десятиразрядный) .

Исправленная двоичная последовательность сигналов с выхода кодера 3 подается на вычитающий вход реверсивного счетчика 9.

Время задержки Ј элемента 6 задержки выбирается таким образом,чтобы исправленная двоичная последовательность сигналов на выходе кодера 3 соответствовала по временному положению той двоичной последовательности сигналов, которую получают на выходе компаратора 3, т.е.

Ј - Ј,+ЗД,где 2, Јг. Ј, времена задержек обработки сигналов соответственно первого декодера 4,второго декодера 5 и кодера 8.

После окончания обработки каждого кодового блока в реверсивном счетчике 9 фиксируется код ДЫ Н - Ng, где Ы - число единиц в двоичной последовательности,формируемой компаратором 3; Н - число единиц в двоичной последовательности, формируемой кодером 8. Таким образом, код Д N несет информацию о достоверности формируемой ДБОИЧ- ной последовательности сигналов компаратором 3. Если ДК 0, то указанные двоичные последовательности совпадают. В этом случае можно считать, что компаратор 3 работает в режиме, когда уровень опорного сигнала располагается симметрично относительно сигнала U &х. Происходит достоверное формирование компаратором 3 двоичной последовательности.

Если или ДК 0, то в формируемой двоичной последовательности сигналов компаратором 3 происходит преобладающее искажение формирования соответственно единиц или нулей. В этих случаях можно считать, что компаратор 3 работает в режиме,когда уровень опорного сигнала располагается несимметрично относительно

сигнала UB)(, что может быть вызвано указанными факторами. Достоверность работы компаратора 3 понижается.

Если кратность ошибок не превы- шает корректирующей способности кода, то на втором выходе второго декодера 5 отсутствует сигнал отказа от декодирования, а сигнал с его

третьего выхода, соответствующий концу каждого кодового блока, проходит через схему И 7 на управляющий вход регистра 10, переписывая в него код ДН из реверсивного счетчика 9 и сбра5 сывая реверсивный счетчик 9 в нулевое состояние (цепь сброса на чертеже не показана). Реверсивный счетчик 9 подготавливается к вычислению кода ДЫ для следующего кодового блока.

0 в соответствии со значением и знаком кода цифроаналоговый преобразователь 11 вырабатывает соответствующий сигнал коррекции опорного

уровня ± Дилп, который суммируется

э с Uor) и изменяет условия работы компаратора 3. Происходит повышение достоверности формирования двоичной последовательности сигналов компаратором 3 за счет симметрирования уров0 ня опорного сигнала относительно CHI- нала UgX

Если кратность ошибок корректирующей способности кода, то сигнал отказа от декодирования с иторого вы5 хода второго декодера запрещает прохождение управляющего сигнала через схему И 7, препятствуя переписи в регистр 10 очередного кода N, и сбрасывает реверсивный счетчик 9 в

0 нулевое состояние, подготавливая его к вычислению кода ДН для следующего кодового блока. Б этом случае опорный уровень не корректируется и сохраняет свое предыдущее значение,

5 Таким образом, в устройстве устанавливается обратная связ1- по коррекции опорного уровня компаратора 3,которая связана с корректирующей способностью применяемого кода.

0 Путем изменения параметров цифро- аналогового преобразователя 1 по экспериментальным данным в устройстве можно установить оптимальный закон изменения значения сигнала коу

5 рекции опорного уровня йД оп В устройстве повышение достоверности воспроизведение информации происходит за счет симметрирования опорного уровня компаратора 3 относительно UB)cy причем нарушение симметрии может быть вызвано указэнными факторами.

Понятие симметрии необходимо понимать в более широком смысле, чем просто соотношение между UQrt и U6)l, так как в устройстве за счет обратной связи устанавливается оптимальный симметричный опорный уровень с точки 1 зрения достоверности воспроизведения двоичной информации.

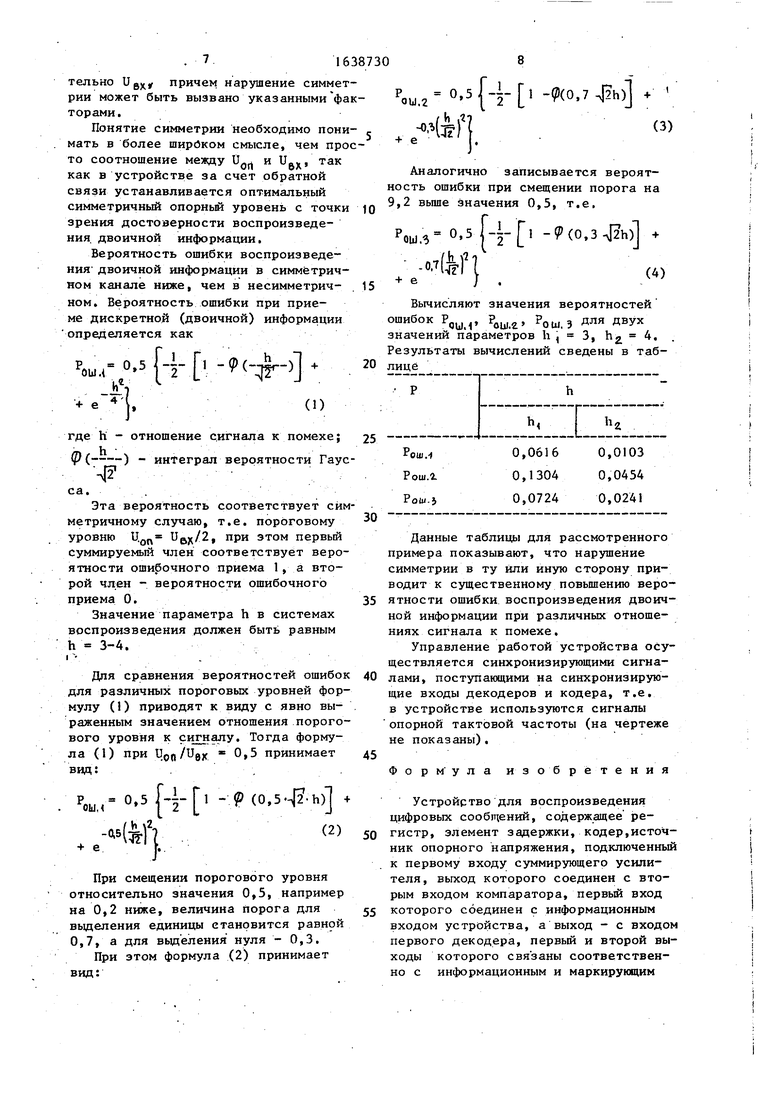

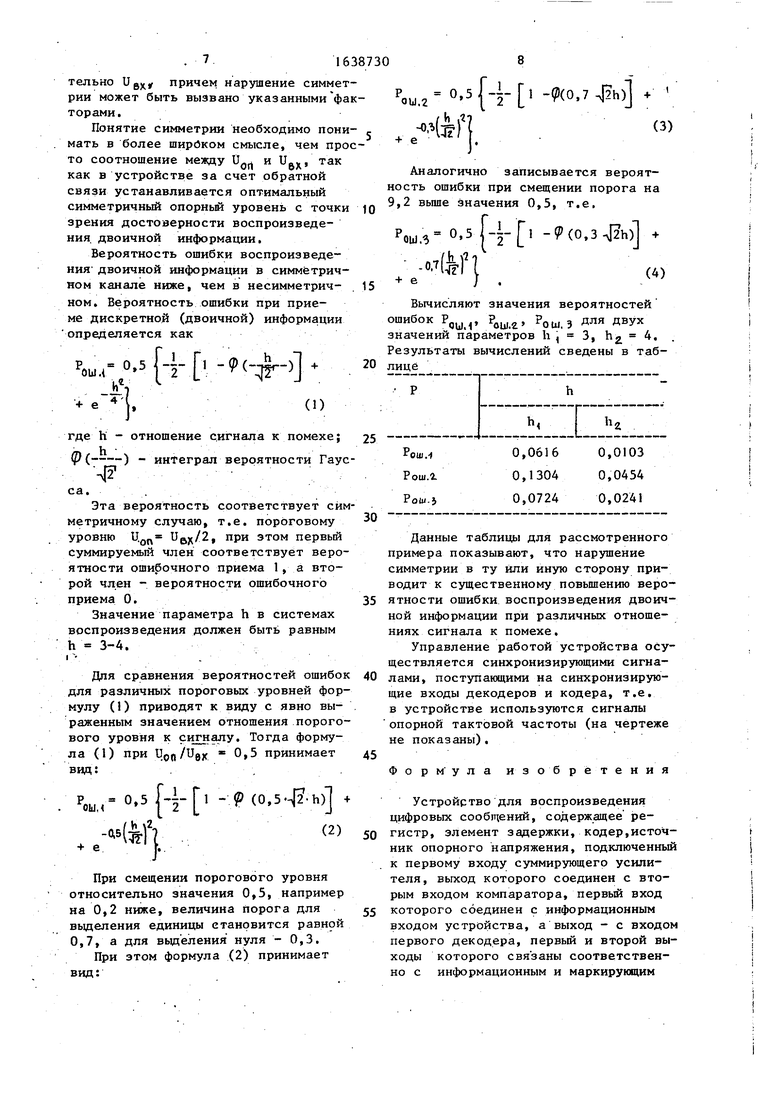

Вероятность ошибки воспроизведения двоичной информации в симметричном канале ниже, чем в несимметрич- 1 ном. Вероятность ошибки при приеме дискретной (двоичной) информации определяется как

(4- .-К)

(1)

РОЫ.2 f H1 -(

-W-fefl

(3)

+ е

Аналогично записывается вероятность ошибки при смещении порога на 9,2 выше значения 0,5, т.е.

f1 -РСО.З-фо

(4)

Вычисляют значения вероятностей ошибок Рсцм, выл, Рош 3 для двух значений параметров h , 3, Ьг 4. Результаты вычислений сведены в таблице

| название | год | авторы | номер документа |

|---|---|---|---|

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Декодер кодов Рида-Соломона | 1989 |

|

SU1777244A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Устройство передачи и приема команд согласования скоростей | 1989 |

|

SU1793553A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

Изобретение относится к технике воспроизведения цифровых сообщений и может быть использовано в каналах воспроизведения цифровой информации, например, в составе запоминающих устройств с движущегося носителя.Целью изобретения является повышение достоверности воспроизведения информации. В устройство для воспроизведения цифровых сообщении, содержащее источник опорного напряжения,подключенный й-первому входу суммирующего усилителя, выход которого соединен с вторым входом компаратора, первый вход которого соединен с информационным входом устройства, а выход - с входом первого декодера, первый и второй выходы которого соединены соответственно с информационным и маркирующим входами второго декодера, введены последовательно соединенные реверсивный счетчик, регистр и циф- роаналоговый преобразователь, выход которого подсоединен к второму входу суммирующего усилителя, элемент задержки, вход которого соединен с выходом компаратора,а выход - с суммирующим входом реверсивного счетчика, вычитающий вход которого соединен с выходом кодера, вход которого соединен с информационным выходом устройства и первым выходом второго декодера, второй выход которого соединен с инвертирующим входом схемы И, с установочным входом реверсивного счетчика и с выходом сигнала отказа от декодирования устройства, а третий йыход подключен к прямому входу схемы И, выход которой подключен к управляющему входу регистра. 1 ил. i (Л С 05 оо оо ОЭ

+ е

-«(Я

М2л

)}.

(2)

где h - отношение сигнала к помехе; (р () интеграл вероятности ГауеЧ

са.

Эта вероятность соответствует симметричному случаю, т.е. пороговому уровню Чоп ив)/2, при этом первый суммируемый член соответствует вероятности ошибочного приема 1, а второй член - вероятности ошибочного приема 0.

Значение параметра h в системах воспроизведения должен быть равным

h - 3-4. i

Для сравнения вероятностей ошибок для различных пороговых уровней формулу (1) приводят к виду с явно выраженным значением отношения порогового уровня к сигналу. Тогда формула (1) при Uon/Uex « 0,5 принимает вид:

.5.#h) +

При смещении порогового уровня относительно значения 0,5, например на 0,2 ниже, величина порога для выделения единицы становится равнрй 0,7, а для выделения нуля - 0,3.

При этом формула (2) принимает вид:

5

0

5

0

5

Данные таблицы для рассмотренного примера показывают, что нарушение симметрии в ту или иную сторону приводит к существенному повышению вероятности ошибки воспроизведения двоичной информации при различных отношениях сигнала к помехе.

Управление работой устройства осуществляется синхронизирующими сигналами, поступающими на синхронизирующие входы декодеров и кодера, т.е. в устройстве используются сигналы опорной тактовой частоты (на чертеже не показаны).

Формула изобретения

Устройртво для воспроизведения цифровых сообщений, содержащее регистр, элемент задержки, кодер,источник опорного напряжения, подключенный к первому входу суммирующего усилителя, выход которого соединен с вторым входом компаратора, первый вход которого соединен с информационным входом устройства, а выход - с входом первого декодера, первый и второй выходы которого связаны соответственно с информационным и маркирующим

входами второго декодера, отличающееся тем, что, с целью повышения достоверности воспроизведения информации, в него введены элемент И соединенные через регистр реверсивный счетчик и цифроанапоговый преобразователь, выход которого подсоединен к второму входу суммирующего усилителя, при этом выход компаратора подключен через элемент задержки к суммирующему входу реверсивного счетчика, вычитающий вход котоив

.

±лиоп

рого соединен с выходом кодера,вход которого подключен к информационному выходу устройства и первому выходу второго декодера, второй выход которого соединен с инвертирующим входом элемента И, устанояочным входом реверсивного счетчика и выходной шиной сигнала отказа от декодирования, а третий выход подключен к прямому входу элемента И,выход которого соединен с управляющим входом регистра.

Вшх -

Отказ от декодирования

| Устройство воспроизведения информации с оптического носителя | 1982 |

|

SU1078465A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для воспроизведения цифровых сообщений | 1984 |

|

SU1243027A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-03-30—Публикация

1989-03-27—Подача