Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией, например, для эффективного приема данных компьютером из локальной сети, выполненной на основе последовательного интерфейса RS- 232С.

Цель изобретения - повышение быстродействия.

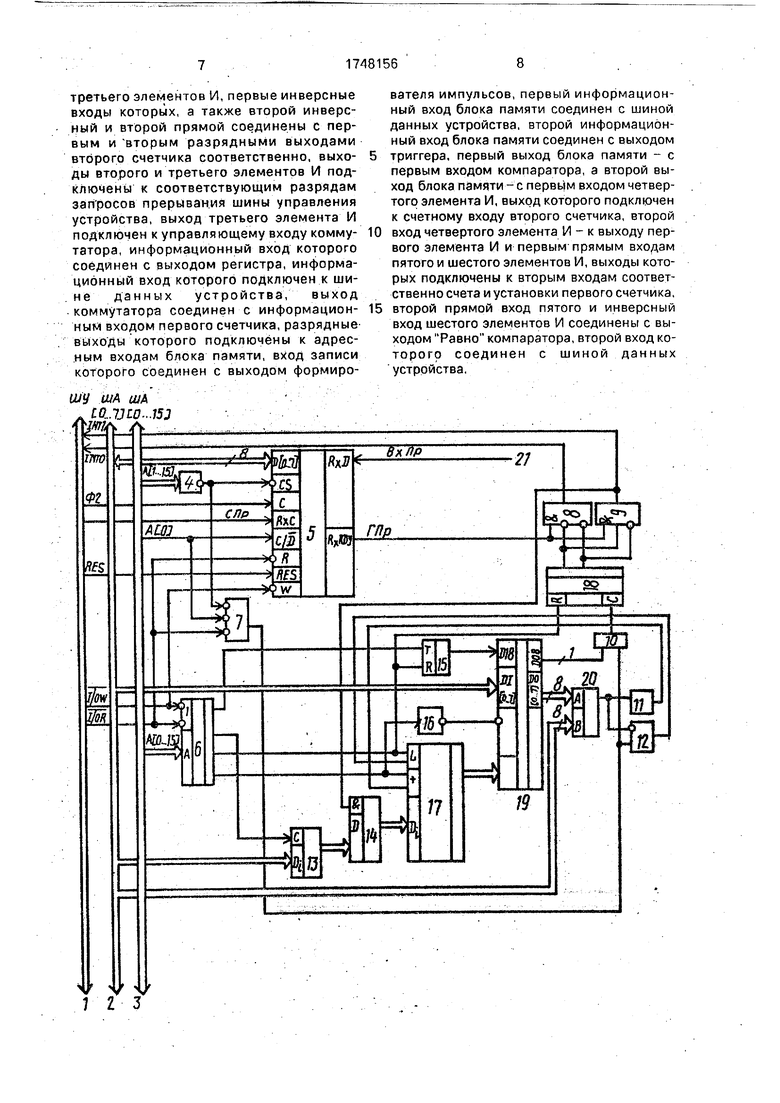

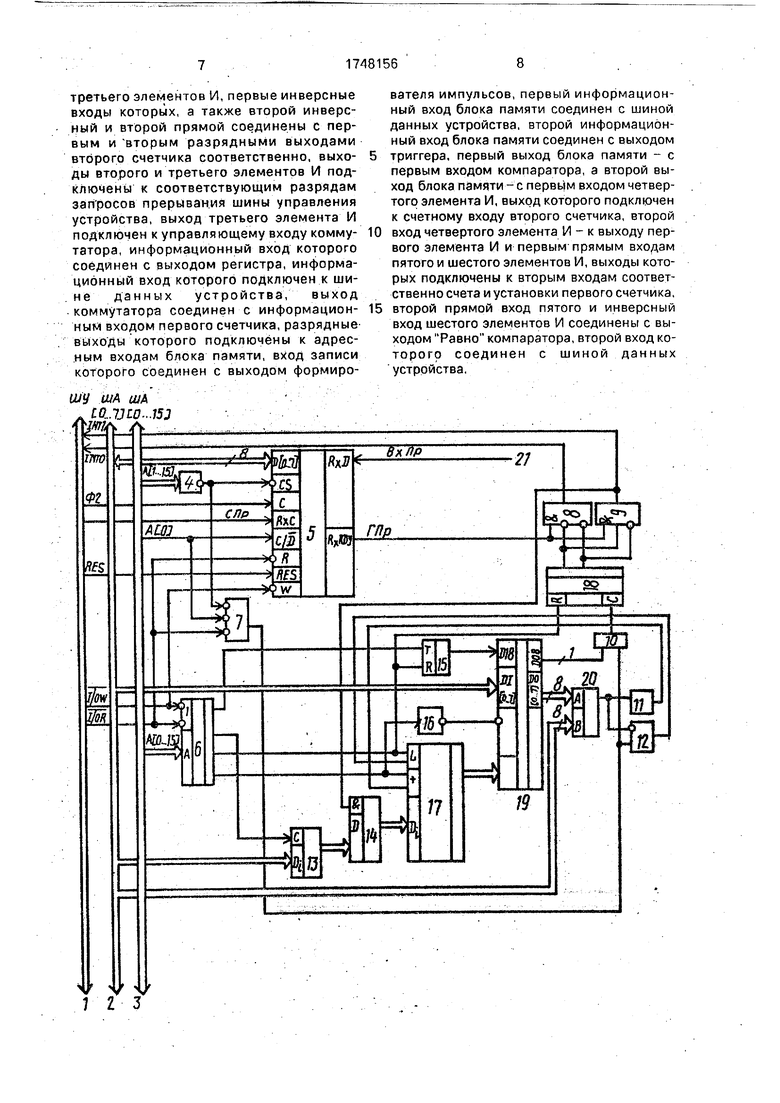

На чертеже представлена функциональная схема устройства.

Устройство содержит процессорные шины управления 1, данных 2; адреса 3, первый 4 дешифратор, блок 5 последова.- тельного интерфейса, второй 6 дешифратор, первый 7, второй 8, третий 9, четвертый 10, пятый 11 и шестой 12 элементы И, регистр 13, коммутатор 14, триггер 15, формирователь 16 импульсов; первый 17 и второй 18 счетчики, блок 19 памяти, компаратор 20, линейный 21 информационный вход.

Данный вариант устройства предназначен для ввода информации в процессор из локальной сети, причем информация представлена в виде текста,, ограниченного с обеих сторон паролями, представляющими собой группы заранее обусловленных знаков (не более 8 знаков на пароль).

Устройство работает следующим образом.

При включении устройства микропроцессор по шине t управления устанавливает в течение нескольких тактов первого синх- ровхода блока 5 сигнал сброса RES по одноименному входу последнего. На второй синхровход РхС блока 5 подаются меандры

VI

4 00

ел о

частотой, превышающей в 16 раз скорость примененных посылок в 9600 бод. Допустим, условные пароли начала и конца сообщения принимаемого в микроЭВМ из линии соответственно ALPHA и BETA размещены в системной памяти под метками М1, М2 (М1: DW ALPHA; M2: DW1 BETA);

ADR0 - адрес, выставляемый на старших линиях адресной шины и дешифрируемый выходом первого дешифратора 4, ADRI, ADR2, ADR3, ADR4 - адреса, дешифрируемые соответственно первым, вторым, третьим и четвертым выходами второго дешифратора 6. Тогда инициализация устройства микроЭВМ примет следующую последовательность: (1) MVIA, 5EH OVT 2xADRO + 1; блок 5 программируется на обмен 8 бит на посылку, контроль по нечетности, 1 столовый бит на посылку, деление частоты сигнала по второму синхровходу 1:16.

(2)MVIA, 36H

OVT 2xADRO + 1; блок 5 настраивается на прием информации из линии 21 по входу Рх.

(3)OVT ADR3; сигналом с третьего выхода дешифратора 6 сбрасывается триггер 15, счетчик 18, сбрасывается счетчик 16, ввиду нулевого значения выхода мультиплексора, блокируемого нулевым значением по входу управления с выхода элемента И 9.

(4)LXI В,0504Н; в рг С помещается длина пароля BETA, равная 4, размещенная под меткой М1: в системной памяти; в рг В помещается длина пароля начала ALPHA, равная 5.

(5)LX1 Н, М1-1; в регистровую пару HL помещается начальный адрес сообщения ALPHA BETA, расположенный по адресу под меткой М1 минус 1.

(6)LABEL1:MV1 D,1

DCRB

INZLABEL2

OVT ADR1; установка триггера 15 по счетному входу

LABEL2: MOVA,M

OVT ADR4

INXH

INZLA8EL1

OVT ADR 1; сброс триггера 15 по счетному входу

MOV В,С

DCRD

INZ LABEL1: исполнение приведенного сегмента программы приводит к размещению последовательности AL ГНАВЕТА в ячейках, начиная с нулевого адреса блока 19 памяти в разрядах 0-7. Конечным знаком А (пятый и девятый символы в AL PHABETA) в

разряде 8 блока памяти с выхода счетного триггера 15 записывается значение, равное единице. Сигнал записи по входу W блока 19 памяти формируется на формирователе 16 из переднего фронта сигнала с четвертого выхода дешифратора 6, который своим задним фронтом инкрементирует счетчик 17, адресующий блок 19 памяти.

(7)MVIA, 5H

OVT ADR2; занесение в регистр 13 значения номера ячейки, равное 5, по которому в блок памяти занесено значение пароля конца BETA,

(8)ОТАРЗ; сброс устройства в исходное состояние, т.е. сброс счетчиков 17, 18, триггера 15.

(9)EI; процессор настраивается на разрешение отработки запросов прерываний, в том числе и сигналов INTO, INTI, поступающих с выходов элементов И 8,9.

Для отработки прерываний INTO, INTI, отведены в системной памяти микроЭВМ следующие фрагменты обработки процессором прерываний INT0: D I

PVSH PSW IN2xADR0 POP PSW Ei

RET Dl

INTl: PVSH H PVSH PSW LHLD STACK

STACK - отведенная заранее ячейка системной памяти с занесенным ,туда первоначальным значением начального адреса хранения принимаемого сообщения

IN 2xADR MOVM,A

iNxH

SHLD STACK POP PSW POP H Ei RET

Очевидно, фрагмент INT0 необходим лишь для прочтения содержимого принятого байта на первом этапе до расшифровки устройством пароля ALPHA, предварящего текст сообщения по входу 21 устройства, тогда как фрагмент отработки процессором прерывания INTI позволяет записать сообщение в отведенную область системной па- мяти.

После инициализации устройство готово к приему сообщений по последовательному входу RxD, Значения счетчиков 17, 18 нулевые. В блоке 19 памяти хранятся паро- ли ALPHABETA с признаками 1 в разряде

8 в ячейках, соответствующих концам паролей (т.е. ячейках 4,8). В регистре 13 - адрес хранения первого символа BETA в блоке 19 памяти.

Допустим первым принятым блоком 5 символом является А . Блок 5 выставляет единичное значение выхода Р хР У на первый вход элемента И 8, который нулевыми значениями выходов счетчика 18 на инверсных втором и третьем входах пропускает сигнал на вход прерывания INT0 Процессор производит холостое чтение по приведенному выше фрагменту, при этом элемент И 7 отрабатывает момент чтения значения А из блока 5 на системную шину 2 данных, стробируя по вторым входам элементов И 11 и 12 единичное значение выхода компаратора 20, производящего сравнение содержимого байта блока 19 памяти и шины 2 данных. В результате элемент И 11 по своему прямому входу пропускает единичное значение выхода компаратора 20 на второй счетный вход счетчика 17, который инкриминируется по срезу приходящего сигнала, адресуя уже вторую букву пароля Т в блоке . 19 памяти По окончании чтения процессором байга, принятого блоком 5, значение его выхода RxRDY сбрасывается, и он готов к принятию очередного символа. Если приходящий символ не равен очередному, адресуемому текущим значениям счетчика 17, при чтении процессором принятого байта из блока 5, нулевое значение выхода компаратора 20 на первом инверсном входе элемента И 12 позволяет последнему пропустить единичный строб с выхода элемента И 7 на второй вход установки счетчика 17, Учитывая нулевое значение входа управления коммутатора 14, счетчик 17 сбрасывается и устройство готово к очередному распознаванию пароля ALPHA. Если счетчик 17 уже адресует последнюю букву пароля П, т.е. равен четырем и в блок 5 приходит эта же буква, то при чтении процессором байта из блока 5 наряду со сраба- тыванием вентиля 11, вентиль 10 пропускает единичное значение с выхода 08 блока 19 памяти. По срезу приходящих сигналов инкриминируются оба счетчика. Причем счетчик 17 адресует уже пароль конца сообщения, счетчик 18 принимает значение 01, блокирующее элемент И 8 и разрешающее элементу И 9 пропускать единичное значение сигнала с выхода RxRDY блока 5. Единичное значение выхода элемента И 8 позволяет теперь вызывать запрос прерывания 1 П, отрабатывая который процессор разрешает сообщение в заранее отведенном месте системной памяти, а также единичным значением по входу управления

коммутатора 14 позволяет последнему подключить выход регистра 13 с хранящимся значением начального адреса пароля конца сообщения в блоке 19 памяти к информационному входу счетчика 17, адресующего этот блок памяти. Прохождение устройством пароля конца сообщения при принятии последнего символа пароля вызовет инкри- мент счетчика 18 и запрет прохождения сиг0 налов с выхода РхР У блока на запрос прерывания процессором, тем самым блокируя дальнейший прием сообщений. Дальнейший прием сообщений возможен лишь с инициализацией устройства процессором.

5 Ф о р м у л а и з о б р е т е н и я

Устройство для ввода информации, содержащее первый дешифратор адреса и блок последовательного интерфейса, линейный информационный вход которого яв0 ляется линейным информационным входом устройства, информационный вход-выход блока последовательного интерфейса подключен к шине данных устройства, первый и второй синхровходы, входы записи, чте5 ния и сброса которого подключены к соответствующим разрядам шины управления устройства, вход задания режима работы соединен с нулевым разрядом шины адреса устройства, а вход выборки блока последо0 вательного интерфейса подключен к выходу первого дешифратора адреса, информационные входы которого соединены со старшими разрядами шины адреса устройства, отличаю щ-ееся тем, что с целью

5 повышения быстродействия, оно содержит второй дешифратор адреса, шесть элементов И, регистр, коммутатор, триггер, формирователь импульсов, два счетчика, блок памяти и компаратор, причем первый выход

0 второго дешифратора адреса подключен к счетному входу триггера, второй выход второго дешифратора адреса - к синхровходу регистра, третий выход второго дешифратора адреса - к первому входу установки пер5 вого счетчика и входам сброса триггера и второго счетчика, четвертый выход второго дешифратора адреса подключен к первому счетному входу первого счетчика и входу формирователя импульсов.информацион0 ный вход подключен к шине адреса устройства, первый вход разрешения - к входу записи блока последовательного интерфейса, а второй - к входу чтения блока последовательного интерфейса и первому

5 инверсному входу первого элемента И, второй и третий инверсные входы которого соединены соответственно с входами режима и выборки блока последовательного интерфейса, выход готовности которого соединен с первыми прямыми входами второго и

третьего элементов И, первые инверсные входы которых, а также второй инверсный и второй прямой соединены с первым и вторым разрядными выходами второго счетчика соответственно, выходы второго и третьего элементов И подключены к соответствующим разрядам запросов прерывания шины управления устройства, выход третьего элемента И подключен к управляющему входу коммутатора, информационный вход которого соединен с выходом регистра, информационный вход которого подключен к шине данных устройства, выход коммутатора соединен с информационным входом первого счетчика, разрядные выходы которого подключены к адресным входам блока памяти, вход записи которого соединен с выходом формироШУ ША ША

CQ..7JЈ0...;JJ WA

вателя импульсов, первый информационный вход блока памяти соединен с шиной данных устройства, второй информационный вход блока памяти соединен с выходом

триггера, первый выход блока памяти - с первым входом компаратора, а второй выход блока памяти - с первым входом четвертого элемента И, выход которого подключен к счетному входу второго счетчика, второй

вход четвертого элемента И - к выходу первого элемента И и первым прямым входам пятого и шестого элементов И, выходы которых подключены к вторым входам соответственно счета и установки первого счетчика,

второй прямой вход пятого и инверсный вход шестого элементов И соединены с выходом Равно компаратора, второй вход которого соединен с шиной данных устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для идентификации паролей пользователей | 1988 |

|

SU1661814A1 |

| БИНОКУЛЯРНОЕ УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ ТРОМБОЗА ГЛУБОКИХ ВЕН ГОЛЕНИ | 2006 |

|

RU2305487C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией. Цель изобретения - повышение быстродействия. Устройство связано с микроЭВМ через адресную,информационную шины и шину управления и содержит два счетчика, два дешифратора, блок последовательного интерфейса коммутатор, формирователь импульсов, компаратор, триггер, регистр, шесть элементов И. Устройство позволяет аппаратно определить Пароли начала и конца сообщения, которые представляют собой последовательности заранее обусловленных символов и ввести сообщение в микро- ЭВМ,значительноповысив производительность последней. 1 ил.

| Устройство для сопряжения телеграфной линии связи с ЦВМ | 1986 |

|

SU1374234A1 |

| Морисита И | |||

| Аппаратные средства мик- роЭВМ | |||

| М.: Мир, 1988 | |||

| стр | |||

| Поршень для воздушных тормозов с сжатым воздухом | 1921 |

|

SU188A1 |

Авторы

Даты

1992-07-15—Публикация

1990-10-22—Подача