Изобретение относится к вычислительной технике и может быть использовано для определения моментов включения тестовых проверок.

Целью изобретения является повышение точности.

Поставленная цель достигается тем, что в устройство для определения моментов включения тестовых проверок, содержащее счетчик импульсов, вход запуска, генератор тактовых импульсов, выход которого соединен со счетным входом счетчика импульсов, схему сравнения, два блока деления, два блока умножения, блок памяти констант, блок памяти допусковых уровней, блок памяти результатов, четыре алгебраических сумматора, формирователь импульсов, два элемента задержки и блок вычитания, выход первого элемента задержки подключен к входу запуска генератора тактовых импульсов, вход останова которого и вход обнуления счетчика импульсов объединены и подключены к выходу второго элемента задержки, вход которого соединен с выходом формирователя импульсов и входом записи блока памяти результатов, информационные входы которого подключены соответственно к разрядным выходам счетчика импульсов и первым информационным входам первого и второго блоков умножения Выход первого блока умножения соединен с первым информационным входом первого алгебраического сумматора, выход которого соединен с первым информационным входом первого блока деления, выход которого подключен к информационному входу блока вычитания, выход которого подключен к первому информационному входу схемы сравнения, второй информационный вход которой подключен к выходу блока памяти допусковых уровней, а выход Равно схемы сравнения соединен с входом формирователя импульсов. Выходы второго и третьего алгебраических сумматоров подключены соответственно к второму информационному входу первого блока деления и первому

СП

С- ДцА

информационному входу второго блока деления, выход которого соединен с информационным входом счетчика импульсов. Первый выход блока памяти констант соединен с первым информационным входом четвертого алгебраического сумматора и вторым информационным входом второго блока умножения, выход которого соединен с вторым информационным входом второго алгебраического сумматора. Второй выход блока памяти констант подключен к второму информационному входу первого блока умножения и второму информационному входу четвертого алгебраического сумматора, выход которого соединен с вторым информационным входом второго блока деления. При этом в устройство дополнительно введены третий элемент задержки, элемент ИЛИ, накапливающий сумматор, блок памяти параметров разброса и блок памяти параметров положения, причем выход третьего элемента задержки соединен с первым входом элемента ИЛИ, второй вход которого является входом запуска устройства, выход элемента ИЛИ соединен с входом первого элемента задержки и входом записи начальных условий счетчика импульсов, разрядные выходы которого подключены соответственно к информационным входам накапливающего сумматора, вход записи которого и вход третьего элемента задержки объединены и соединены с выходом формирователя импульсовВыход накапливающего сумматора соединен с первыми адресными входами блока памяти параметров положения и блока памяти параметров разброса, второй адресный вход которого подключен к третьему выходу блока памяти констант, первый и четвертый выходы которого соединены соответственно с вторым и третьим адресными входами блока памяти пар етров положения, выход которого соединен с вторым и нформа- ционным входом второго алгебраического сумматора и первым информационным входом третьего алгебраического сумматора, второй информационный вход которого и второй информационный вход первого алгебраического сумматора подключены к выходу блока памяти параметров разброса.

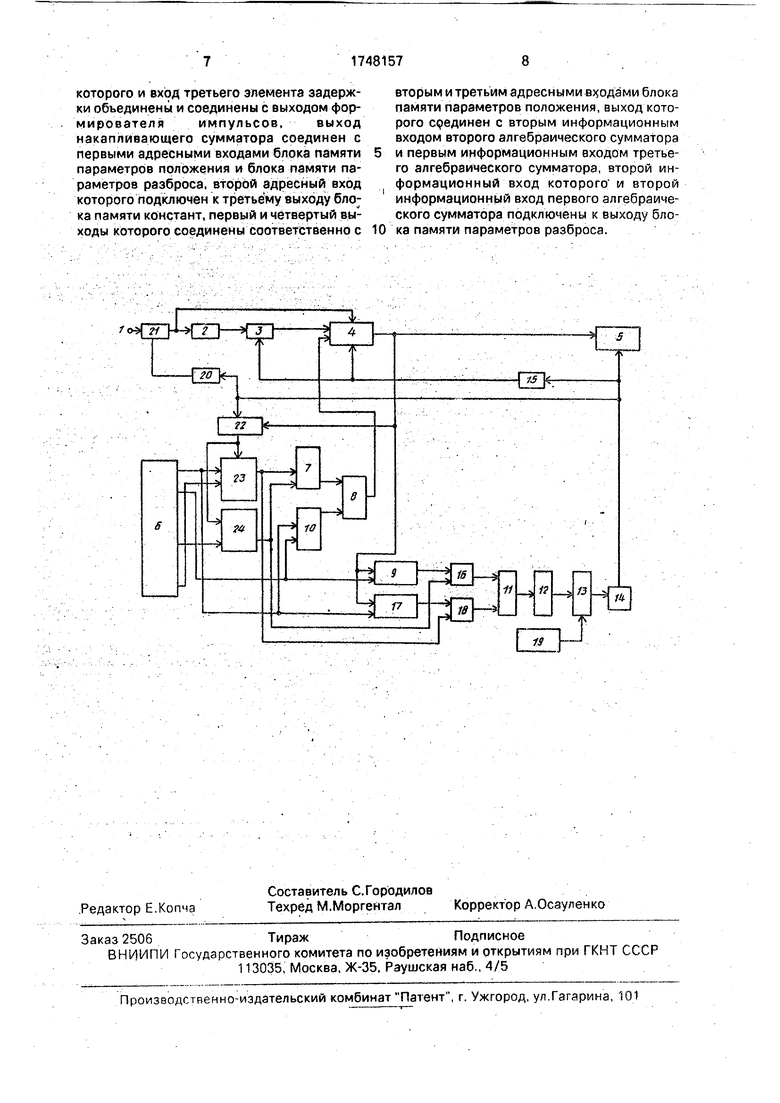

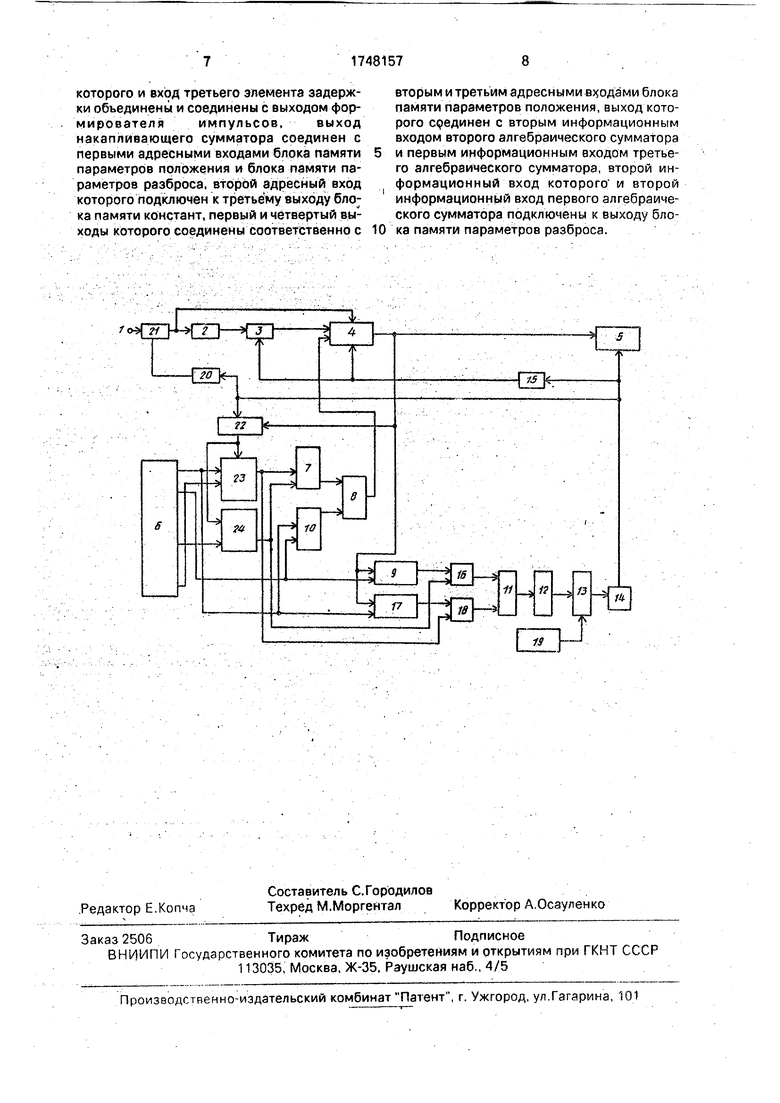

На чертеже изображена структурная схема устройства.

Устройство содержит вход 1 запуска, первый элемент 2 задержки, ГТИ 3, счетчик 4 импульсов, блок 5 памяти результата, блок б памяти констант, третий алгебраический сумматор 7, второй блок 8 деления, первый блок 9 умножения, четвертый алгебраический сумматор 10, первый блок 11 деления, блок 12 вычитания, схему 13 сравнения,

формирователь 14 импульсов, второй эле мент 15 задержки, первый алгебраический сумматор 16, второй блок 17 умножения, второй алгебраический сумматор 18, блок

19 памяти допусковых уровней, третий элемент 20 задержки, элемент ИЛИ 21, накапливающий сумматор 22, блок 23 памяти параметров положения и блок 24 памяти параметров разброса.

Работа устройства основана на вычислении функции принадлежности времени включения тестовых проверок

/«ti 1 - I

3oi - ti ae

t| Cfe + Ooi

0)

при условии (a0r Ooi )/(ae + Ое) ti (а0)

+ ае) /ае- cfe},

где a0i, obi , ае, Ое - коэффициенты, характеризующие положение и разброс возможных значений интенсивности обнаружения дефектов и начальной вероятности их необнаружения.

С учетом выбираемого допускового

уровня ид по функции принадлежности можно количественно оценить момент времени включения тестовых проверок t-д до появления дефекта.

Работа устройства начинается с подачей запускающего импульса с входа 1 запуска через элемент ИЛИ 21 на вход записи начальной установки счетчика 4 импульсов, сигнал начальной установки, равный значению времени левой границы условия (1),

формируется последовательно соединенными блоком 6 памяти констант, блоком 24 памяти параметров разброса, третьим 7 и четвертым 10 алгебраическими сумматорами, вторым блоком 8 деления, на выходе

которого формируется сигнал (a0r cr0i)/(ae + + те).

Накапливающий сумматор 22 формирует на выходе сигнал, соответствующий величине Тн1 времени общей наработки

тестируемой аппаратуры.

Блок 23 памяти параметров положения, выполненный в виде ПЗУ, производит вычисление коэффициента а0| по формуле

50

Soi aoexpf-aeTHi-.

(2)

55

Блок 24 памяти параметров разброса производит вычисление коэффициента Ъ0, по формуле

ОЫ e Ob/ VTVT+ 1

(3)

Сформированный сигнал начальной установки с учетом (2) и (3) поступает выхода

второго блока 8 деления на информационный вход счетчика 4 импульсов. Импульс с выхода элемента ИЛИ 21 поступает также на вход первого элемента 2 задержки, после чего поступает на вход запуска ГТИ 3, им- пульсы которого с постоянной частотой поступают на счетный вход счетчика 4 импульсов.

Счетчик 4 импульсов формирует временную шкалу и передает этот сигнал на информационный вход блока 5 памяти результатов, первые входы блоков 9 и 17 умножения, на вторые входы которых подаются сигналы от блока 6 памяти констант. В блоке 9 формируется число ое ti, a в блоке 17-aeti. Сумматоры 16,18 и блоки 11 и 12 формируют значение функции принадлежности.

Схема 13 сравнения при равенстве значения функции принадлежности допусково- му уровню ид, сформированного блоком 19 памяти допусковых уровней, формирует на выходе сигнал, который поступает на формирователь 14 импульсов, который укорачи- вает сигнал и передает его на управляющий вход блока 5 памяти результатов, в котором запоминается искомое время гд. Импульс с выхода формирователя 14 импульсов поступает также на второй элемент 15 задержки, выход которого соединен с входом обнуле- ния счетчика 4 импульсов и с входом останова ГТИ 3. Импульс с выхода формирователя 14 импульсов поступает также на управляющий вход накапливающего сумматора 22 и вход третьего элемен- та 20 задержки. С приходом импульса на управляющий вход накапливающий сумматор 22 производит суммирование сигнала с выхода счетчика 4 импульсов со своим содержимым, следовательно, накапливающий сумматор 22 находится в режиме суммирования времени наработки тестируемой аппаратуры. После задержки импульс с выхода третьего элемента 20 задержки поступает на вход элемента ИЛИ 21 и описан- ные процессы повторяются.

Формула изобретения

Устройство для определения моментов включения тестовых проверок, содержащее счетчик импульсов, генератор тактовых импульсов, выход которого соединен со счетным входом счетчика импульсов, схему сравнения, два блока деления, два блока умножения, блок памяти констант, блок памяти допусковых уровней, блок памяти результатов, четыре алгебраических сумматора, формирователь импульсов, два

элемента задержки и блок вычитания выход первого элемента задержки подключен к входу запуска генератора тактовых импульсов, вход останова которого и вход обнуления счетчика импульсов объединены и подключены к выходу второго элемента задержки, вход которого соединен с выходом формирователя импульсов и входом записи блока памяти результатов, информационные входы которого подключены соответственно к разрядным выходам счетчика импульсов и первым информационным входам первого и второго блоков умножения, выход первого блока умножения соединен с первым информационным входом первого алгебраического сумматора, выход которого соединен с первым информационным входом первого блока деления, выход которого подключен к информационному входу блока вычитания, выход которого подключен к первому информационному входу схемы сравнения, второй информационный вход которой подключен к выходу блока памяти допусковых уровней, а выход Равно схемы сравнения соединен с входом формирователя импульсов, выходы второго и третьего алгебраических сумматоров подключены соответственно к второму информационному входу первого блока деления и первому информационному входу второго блока деления, выход которого соединен с информэ- ционным входом счетчика импульсов, первый выход блока памяти констант соединен с первым информационным входом четвертого алгебраического сумматора и вторым информационным входом второго блока умножения, выход которого соединен с вторым информационным входом второго алгебраического сумматора, второй выход блока памяти констант подключен к второму информационному входу первого блока умножения и второму информационному входу четвертого алгебраического сумматора, выход которого соединен с вторым информационным входом второго блока деления. отличающееся тем, что. с целью повышения точности, оно дополнительно содержит третий элемент задержки, элемент ИЛИ, накапливающий сумматор, блок памяти параметров разброса и блок памяти параметров положения, причем выход третьего элемента задержки соединен с первым входом элемента ИЛИ. второй вход которого является входом запуска устройства, выход элемента ИЛИ соединен с входом первого элемента задержки и входом записи начальных условий счетчика импульсов, разрядные выходы которого подключены соответственно к информационным входам накапливающего сумматора, вход записи

которого и вход третьего элемента задержки объединены и соединены с выходом фор- мирователя импульсов, выход накапливающего сумматора соединен с первыми адресными входами блока памяти параметров положения и блока памяти па раметров разброса, второй адресный вход которого подключен к третьему выходу бло; ка памяти констант, первый и четвертый выходы которого соединены соответственно с

0

вторым и третьим адресными входами блока памяти параметров положения, выход которого соединен с вторым информационным входом второго алгебраического сумматора и первым информационным входом третьего алгебраического сумматора, второй информационный вход которого и второй информационный вход первого алгебраического сумматора подключены к выходу блока памяти параметров разброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения моментов включения тестовых проверок | 1989 |

|

SU1661784A1 |

| Устройство для прогнозирования времени восстановления сложного технического объекта | 1989 |

|

SU1661797A1 |

| Устройство для вычисления оптимальных параметров микроэлектронных схем | 1980 |

|

SU942046A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ БЛИЗОСТИ ТЕКУЩИХ И ЭТАЛОННЫХ ПРИЗНАКОВ ОБЪЕКТОВ С АДАПТАЦИЕЙ К УСЛОВИЯМ ОБСТАНОВКИ | 1996 |

|

RU2112271C1 |

| Устройство для определения момента изменения свойств случайного процесса | 1983 |

|

SU1166149A1 |

| Система идентификации параметров линейных объектов | 1988 |

|

SU1534429A1 |

| Устройство для определения моментов изменения свойств случайного процесса | 1985 |

|

SU1282159A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОТКЛОНЕНИЙ ПАРАМЕТРОВ ПРИ ДОПУСКОВОМ КОНТРОЛЕ | 2016 |

|

RU2617982C1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для прогнозирования времени восстановления сложного технического объекта | 1990 |

|

SU1748159A2 |

Изобретение относится к вычислительной технике и может быть использовано для Рт , определения моментов времени включения тестовых проверок. Целью изобретения является повышение точности устройства содержащего вход запуска, элемент ИЛИ ГТИ, счетчик импульсов, блок памяти результатов, блок памяти констант, четыре алгебраических сумматора, два блока деления, два блока умножения, три элемента задержки, блок вычитания, схему сравнения, формирователь импульсов блок памяти допусковых уровней накапливающий сумматор, блок памяти параметров и блок памяти параметров разброса 1 ил

| Устройство для определения моментов включения тестовых проверок | 1989 |

|

SU1661784A1 |

Авторы

Даты

1992-07-15—Публикация

1990-04-28—Подача