Г

Изобретение относится к запоминающим устройствам и может найти приме- нешсе при построении запоминающих .устройств высоконадежных вычиспитепь ных систем. ,

Известно резервированное многоканальное запоминающее устройство, содержашее регистр адреса, дешифраторы адреса, накопители, регистры слова, схему равен- . стеа кодов, элемент И, блок управления, Q элемент И ЛИ, группы элементов И по количеству накопителей, выходной регистр, дополнительные регистры слова по количес.тву накопителей и схемы поразрядной прю- верки по. количеству накопителей fl.15

Недостатки устройства состоят в боль- ищх аппаратурных затратах и невысокой надежности.

Наиболее близким техническим решением к .предлагаемому является резервиро- го ванное многоканальное запоминающее устройство, содержащее модули памяти, регистр адреса, состоящий из регистра номера модупя, выход которого подсоединен к входу дешифратора номера Moioynfl и регистра нокюра ячейки, выход которого подсоединен к входам регистров адреса накопителей модулей, выходной регистр, соединенный с блоком управления, блок коммутации модулей (содержащий регистр состояния модулей, и ксилмутатор), один вход которого подключен к выхояу Дешифрат(фа номера модупя, а выход - ко входам накопительных мопупей, блок коррекции, выходы которого подсоединены соответственно к другсмиу входу блсжа кс 1мутации модулей в BUxofbtoMy регистру, а входы - к выходам введенных в устройство блоков схем ИЛИ (сборка), входы которых подключешзг к выходам регистрсж слов накопительных модулей 2.

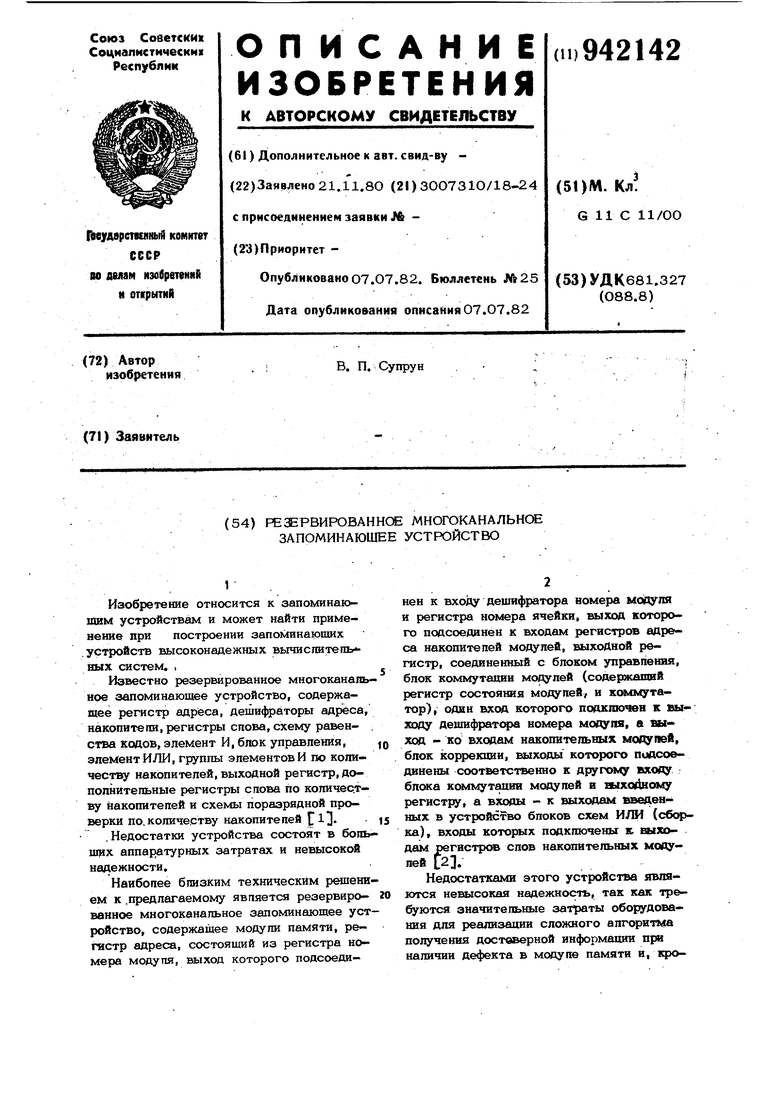

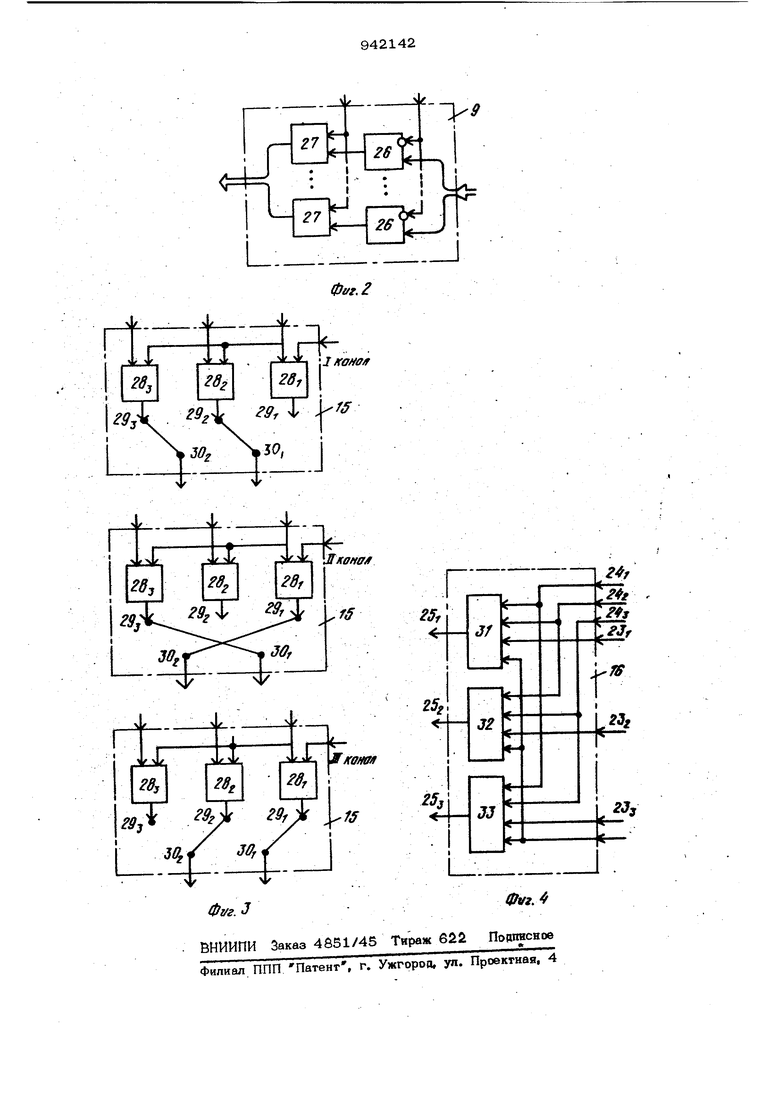

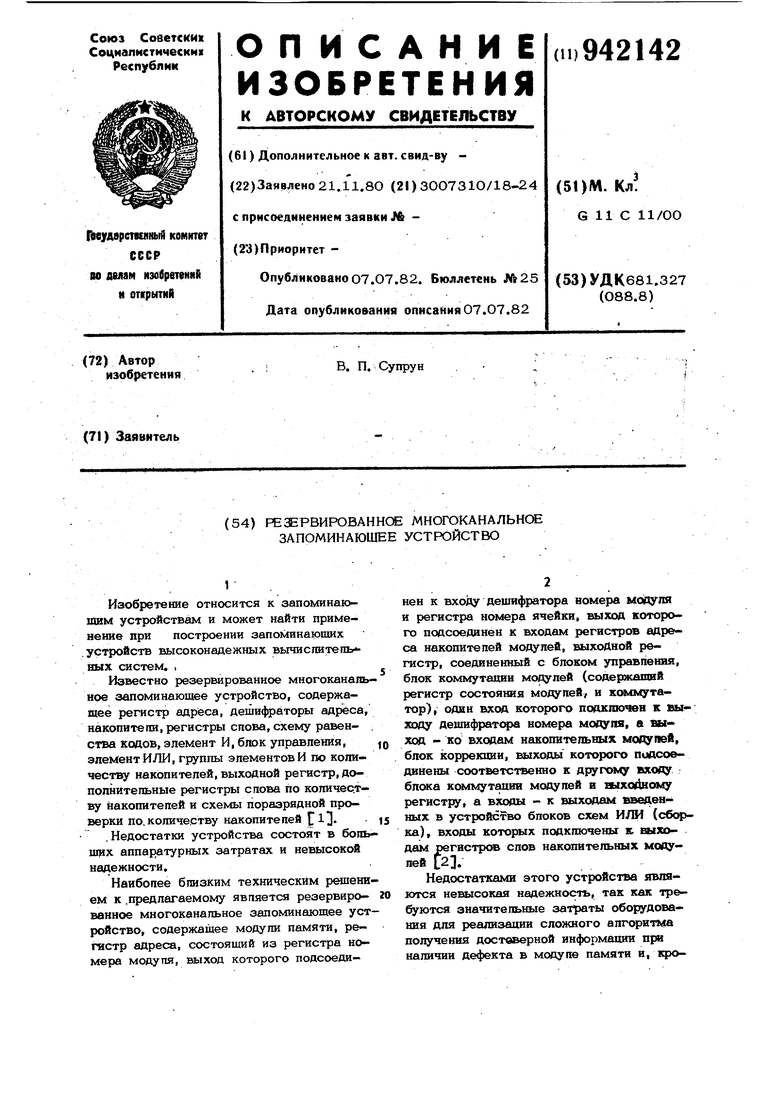

Недостатками этого устройства яташются невысокая надежность, так как требуются значительные затраты оборудования для реализации сложного алгоритма получения достоверной информации при наличии дефекта в модуле памяти и, 1фо39Me того, жесткая привязка номеров мо- дупей памяти к адресу снижает эффективность резервирования, а также невысокое быстродействие, так как при наличии отказов в модулях памяти время выборки информации резко возрастает. Цепь изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в резервированное многоканальное запоминающее устройство, содержащее в каждом канале, блоки памяти, адресные, информационные и управляющие входы которых являются соответственно адресными и информационными входами и входами записи устройства, регистры номеровблоков памяти, элемент ИДИ входы которого подключены к выходам блоков памяти, дешифратор, регистр состояний и коммутаторы, входы которых соединены соответственно с выходами регистра состояний, введены в каждом канале группа схем сравнения, группы элементов И, пер вый и второй погические блоки, схема сравнения, мажоритарные элементы и шиф ратор, причем первые входы элементов И первой группы соединены соответственно с выходами схем сравнения группы, перные входы которых подключены соответственно к выходам регистров номеров блоков памяти, информационные входы которых соединены с информационными входами 1поков памяти, входы обращения которых подкшочены соответственно к вы ходам элементов И первой группы| вторые входы схем сравнения группы соединены со входами дешифратора, адресными входами блоков памяти и управляющими входами коммутаторов, первые входы эле ментов И второй группы подключены соот ветственно к выходам дешифратора, а выходы - соответственно к входам строби- рования регистров номеров блоков памяти Первый, второй и третий вхояь второго логического блока подключены соответст- венно к выходам коммутаторов и входам первого мажоритарного элемента, инверсный выход которого соединен с четвер- : тым входом второго логического бпока, выходы которого подключены соответственно к управляющим входам первого логического блока, входы которого соединены с выходами элемента ИЛИ, а выход подключен к первому входу схемы сравнения и первому входу второго мажоритар ного элемента, второй вход которого соединен с вторым входом схемы сравнения, прямой выход и входы первого мажоритар 2 rtOro элемента соединены соответственно с одними из входов шифратора, другие входы которого подключены соответственно к другим входам шифраторов и выходам схем сравнения всех кан&лов, первый, второй и третий входы второго мажоритарного элемента каждого канала соединены соответственно с ьходами вторых мажоритарных элементов других каналов, вторые входы элементов И первой и второй групп, выходы шафраторов и вторых мажоритарных элементов явл5потся соответственно входом обращения, входом стробирования, выходами признаков отказавших каналов и информационными выходами устройства. При этом каждый первый логический блок выполнен содержащим элементы запрета и элементы ИЛИ - по количеству разрядов устройства, причем первые входы элементов ИЛИ подключены соответственно к выходам элементов запрета, инверсные входы которых и вторые входы элементов ИЛИ являются соответственно первым и вторым управляющими входами первого логического блока, входами которого явл1иотся прямые входы элементов запрета, а выходом - выходы элементов ИЛИ. Причем каждый второй логический элемент выполнен содержащим элементы И, первые входы которых являются соответс-паенно первым, вторым и третьим входами блока, вторые входы элементов И объединены и являются четвертым входом блока, выходы элементов И являются выходами блока. На фиг. 1 изображена функциональная схема устройства; на фиг. 2 и 3 - функциональные схемы вариантов выполнения соответственно первого и второго логических блоков; на фиг. 4 -функциональная схема шифратора. Устройство состоит (фиг. 1) из первого 1, второго l. и третьего 1 идентичных каналов, каждый из которых содержит блоки памяти, регистры 3i-3 номеров блоков памяти, схемы 4jj-4 yj сравнения группы, первую , и вторую 6,-6у, группы элементов И, дешифратор 7, элемент ИЛИ 8, первый логический блок 9, схему Ю сравнения, первый мажоритарный элемент 11, регистр 12 состояний, коммутаторы , второй мажоритарный элемент 14, второй логический блок 15 и шифратор 16. На фиг, 1 обозначены адресные входы 17, информационные входы 18 и выходы 19, входы 20 стробирования, входы 21 обращения, входы 22 записи устройства, выходы коммутаторов, выходы схем сравнения и выходы признаков отказавших канапов устройства. Первый логический блок (фиг. 2) содержит элементы 26 запрета и ИЛИ 27. Второй логический блок (фиг. 3) каждого канала содержит элементы И с выходами соответственн На фиг. 3 обозначены выходы и ЗОэ второго логического блока. Шифратор (фиг. 4) содержит элемен ты И 31-33. Регистр 12 (фиг. 1) разделен на и секций, где и - количество блоков 2 па мяти в каждом канале устройства Устройство работает следующим образом. Рассмотрим вариант устройства с четырьмя блоками памяти (фиг. 1) и соответственно четырьмя трехразрядными секциями регистра 12. Вначале, когДа все блоки 2 -2j памяти (фиг. 1) исправны, производится исходная настройка устройства, т.е. по- сылка во всех каналах 1 единиц во все разряды всех.секций регистра 12. Запись адресов блоков 2, памяти производится следующим образом. Два (например, старшие) разряда адресного входа 17 .каждого канала 1 поступает на вход дешифратора 7, на одном из выходов которого вырабатывается сигнал, и отпирает соответствующий элемент И Q 6. На входе, 2О вырабатывается сигнал который, пройдя через соответствующий элемент И 6, поступает на стробируюащй вход одного из регистров , в котог рый записывается присваиваемый адрес для соответствующего блока поступающий на информационные вхояы одного из регистров 3 -3 с двух (например, старших) разрядов входа 18. Таким образом, физические номера бл ков 2 памяти не закреплены жестко за их адресом, в то же самое время секции регистра 12 закреплены жестко за адре- сагЛи блоков 2 соединением соответствую шим образом выходов их с входами коммутаторов 1Я -13л, которые пропускают сигналы на свои выходы с соответствующих входов .в соответствии с содержимым двух старших разрядов адреса. Запись информации в устройство производится следующим образом. На входы 21 и 22 подаются сигналы, а на входы 17 и 18 подаются соответственно код адреса и информация для записи. Старшие два разряда адреса адресуют блок 2 памяти, а остальные разрядьг указывают адрес ячейки в блоке 2 памяти. Старшие два разряда адреса поступают на вторые входы схем сравнения, на первые входы которых поступают коды с соответствующих регистров 3i-3. Сигнал на выходе вырабатывает только одна из схем 4 -4 и отпирая соответствующий элемент И ,. Таким образом, сигнал обращения поступает только на тот из блоков ,, в который в соответст вующую ячейку записывается информация. При чтении информации сигнал на входе 22 не вырабатывается, а считанная с соответствующей ячейки соответствующего блока 2 -2 информация через элемент ИЛИ 8 поступает на информацион- . ный вход блока 9, Когда блоки в каждом канале 1 исправны, до обращения к устройств во всех разрядах регистра 12 имеются единицы, поэтому в этом случае с выходов коммутаторов поступают единичные сигналы на соответствующие входы мажоритарного элемента- 11, блока 15 и шифратора 16. На инверсном выходе мажоритарного элемента 11 и на соотве.т- . ствующем входе блока 15 при этом сиг нал отсутствует, а на прямом выходе элемента 11 и соответствующем входе шифратора 16 присутствует сигнал. При отсутствии сигнала на инверсном выходе элемента 11 элементы И (фиг. 3) закрыты, поэтому сигналы отсутствуют на выходах блока 15 (фиг.1) и соответственно на управляющих входах блока 9. При этом информация с информационного входа блока 9 поступает на его выход и соответственно через второй мажоритарный элемент 14 на выход 19. Следует отметить, что на входах и выходах элемента 11 присутствуют оДтнрразрядные сигналы, а на каждом из вхбдов и выходов элемента 14 - многоразрядная информация. Кроме того, информация с выхода бпо:ку 9 поступает на первый вход схемы Ю сравнения своего канала .l и соответствующего соседнего канала 1. При этом, если, например,,в первом канале 1 в блоках 2(-2j, .происходит отказ, то на выходах 24 и 242. схем ДО в первом 1 и во втором 1 канапах вырабатываются сигналы, которые поступают на шестой и седьмой входы шифраторов 16 во всех канапах 1 -1з каждом канапе

,, в шифраторах 16 эпементы И 3133 (фиг, 4) открыты по первому входу сигналом с выхода мажоритарного эпемента 11, а по вторым выходам-сигналами с выходов 2ЗУ-23 3 (фиг. 4) коммутаторов , (фиг. 1). По третьему и четвертому входу открыт только элемент И 31 (фиг. 4) сигналами с выходов 24. и Ю (фиг. 1) сравнения первого 1 и второго 2, каналов. Таким образом, при отказе в первом канале 1 вырабатъшается сигнал только на выходе 25 (фиг. 1) признака отказавшего канала 1. Аналогичным образом сигнал вырабатывается на выходе 25,j(25a) при отказе в одном из блоков 2j-2j во втором 1 (третьем l) канале. После этого в соответствующую секцию регистра 12 заносится код ОН где О означает отказ определенного блока 2 в первом канале l-f.

Если при обращении к блоку 2(фиг. 1) происходит отказ во втором канапе l то существует некоторая вероятность

выработки сигнала на выходе 25 вместо выхода 2 5о признака отказавшего кана ла 1л. На выходе 25 при этом сигнал не вырабатывается, так как ноль с выхода первого разряда первой секции регистра 12 через коммутатор 13 (выход 23 ) поступает на второй вход элемента И 31 и запрещает его срабатывание. Выработка сигнала на выходе 25 вмеСто выхода 252 происходит, если во втором канале l. происходит отказ того же типа и в том же разряде, чго и в первом канале 1. В противном случае-сигналы вырабатываются и на выходе 25а; и на выходе 25 л в кан4Дом канале Х|-1з Если же отказ в первом канале 1и вырабатывает сигнал (О или ), совпадающий с истинным сигналом в исправном канале Ij, а во втором канале 12. происходит отказ, вырабатывающий противоположный сигнал ( или О), то сигнал вырабатывается на выходе 25. Таким образом, наличие второго отказа обнаруживается оперативно, а для достоверной локализации отказавшего канала Х( , 1- или 1 необходима поканальная про верка, причем адрес на входе 17 указывает как адрес блока , так и адрес ячейки в блоке 2, -2, породивший бракЕсли, например, происходит отказ в блоках 2 в первом 1 и во втором l. каналах, то в первой секции регистра 12 устанавливается код ОО1. В этом случае при обращении к блокам 2 появляется сигнал только на выходе коммутатора 13j. При этом открывается только элемент И 28 (фиг. 3) и только на его выходе 29 в каждом канале з присутствует сигнал, причем в первом канале If этот сигнал через второй выход ЗОа. (фиг. 3) блока 15 {4мг. 1) поступает на управляющий вход блока 9 и соответственно на первые входы элементов ИЛИ 27 (фиг. 2), при этом по всем разрядам на выходе блока 9 (фиг. 1) вырабатываются единицы. Во втором канале 1 сигнал через выход 3Q, (фиг. 3) блока 15 поступает на управляющий вход блока 9 и соответственно на входы запрета элементов 26 ((. 2), поэтому во Втором канапе 1 (фиг. 1) на выходе блока 9 по всем разрядам выдаются нули В третьем канале 1з выход 29 (фиг. 3) незадействован, поэтому сигналы на выходах блока 15 (фиг. 1) отсутствуют, а на выходе блока 9 присутствует считанный с блока 2 код, который поступает на выходы 19 всех каналов о, (фиг. 1). так как на их входах, связанных межканальными связями выходами первого 1 и второго1 каналов присутствуют соответственно единицы и купи.

На выходах сигналы не вырабатываются, так как отсутствует сигнал на инверсном выходе элемента 11 (фиг. 1) и соответственно на первых входах элементов И 31-33 (фиг. 1) шифратора 16 (фиг. 1).

Для возможности тестового контроля отказавшего канала при поканальной работе устройства изменяется адресация отказавшего, например, блока 2 памяти, таким образом, чтобы этот отказавший бпок 2 был адресован ко второй секции регистра i2.

Технико-экономические преимущества предлагаемого устройства заключаются в том, что оно сохраняет работоспособност при многократных отказах в блоках памяти, причем время считывания информации при наличии отказов не увеличивается, за счет чего повышаются его надежность и быстродействие по сравнению с прототипом. Формула изобретения 1, Резервированное многоканапьное запоминающее устройство, содержащее в каждом канапе бпоки памяти, адресные, информационные и управляющие входы которых являются соответственно адресными и информационными входами и входами записи устройства, регистры номеров блоков памяти, элемент ИЛИ, входы которого подключены к выходам блоков памяти, дешифратор, регистр состояний и коммутаторы, входы которых среди нень соответственно с выходами регистра состояний, от личающееся тем, что, с цепью повышения надежности устройства, оно содержит в каждом канапе группу схем сравнения, группы элементов И, первый и второй логические блоки, схему сравнения, мажоритарные элементы и шифратор, причем первые вхрды элементов И первой группы соединены соответственно с выходами схем сравнения группы, пер)- вые входы. которых подключены соответственно к выходам регистров номеровблоков памяти, информационные входы которых соединены с информационными входами блоков памяти, входь обращения которых подключены соответственно к выходам элементов И первой группы, вторые входы схем сравнения группы соединены с входами дешифратора, адресными входами блоков памяти и управляющими входами коммутаторов, первые вхошл элементов И второй группы подключены соответственно к выходам дешифратора, а выхо. ды - соответственно к входам стробирования регистров номеров блоков памяти, пер шлй, второй и третий входы второго лаги- ческого блока подключены соответственно к выходам коммутаторов и входам первого мажоритарного элемента, инверсный выход которого соединен с четвертым входом второго логического блока, выходы которого подключены соответственно . к управляющим входам первого логического блока, входы которого соединены с выходами элемента ИЛИ, а выход подкшочен к первому входу схемы сравнения и пёрвому входу второго мажоритарного 94 210 элемента, второй вход которого соединен с вторым входом схемы сравнения, прямой выход и входы первого мажоритарного элемента соединены соответственно с одними из входов шифратора, другие входы которого подключены соответственно к другим входам шифраторов и выходам схем сравнения всех каналов, первый, второй и третий входы второго мажоритарного элемента каждого канала соединены соответственно с входами вторых, мажоритарных элементов других каналов, вторые входы элементов И первой и втор«Л групп .выходы шифраторов и вторых мажс ритарных элементов являются соответственно входом офащения, входом стробирования, выходами признаков отказавигах каналов и информационными выходами устройства, 2.Устройство поп. 1, отличающее с я . тем, что каждый первый логический блок содержит элементы запрета и элементы ИЛИ - по количеству разрядов устройства, причем первые входы элементов ИЛИ подключены соответственно к выходам элементов aianpeта, инверсные входы которых и вторые входы элементов} ИЛИ являются соответственно первым-и вторым управляющими входами первого логического блока, входами которого являются прямые входы элементов запрета, а вь1ходам - выходы элементов ИЛИ. 3.Устройство по пп, 1 и 2, о т л ич а ю щ е е с я тем, что каждый .второй логический элемент содержит элементы И,. первые входы которых являются соответственно первым, вторым и третьим входами блока, вторые входы лементов И объедивегол и являются четвертым входом блока, выходы элементов И являются выходами блока. Источники информации, принятые во внимание при. экспертизе 1.Авторское свидетельство СССР №385319, кп. в 11 С 29/00 1972. 2.Авторское свидетельство , № 439О20, кл.. G 11 С 29/00, 1972 (прототип).

Фаг, 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1702434A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

Авторы

Даты

1982-07-07—Публикация

1980-11-21—Подача