Изобретение относится к вычислительной технике, а именно к устройствам преобразования координат, и может быть использовано в специализированных вычислителях при преобразовании адресов телевизионного дисплея.

Известно устройство для преобразования координат, содержащее два регистра абсцисс, два регистра ординаты, два сумматора, два вычитателя, два счетчика угла, счетчик дистанции, регистр угла, два дешифратора, схему сравнения, а также вход аргумента, два выхода абсциссы, два выхода ординаты, выходы разрешения и запрета устройства и блок управления.

Недостатком данного устройства является то, что блоки поворота искомого и исходного вектора и схема управления, включающая блок управления, выполнен так, что вектора вращаются только вокруг начала координат, не обеспечивая тем самым поворот изображения относительно произвольного центра вращения.

Ближайшим техническим решением (прототипом) является устройство для преобразования координат. Известное устройство содержит регистры абсциссы и ординаты, два вычитателя, сумматор, два счетчика угла, счетчик дистанции, два регистра угла, два дешифратора и две схемы сравнения.

Недостатком данного устройства является наличие в схеме дешифраторов, анализирующих граничные значения угла и дистанции и выдающих управляющие сигналы на блок управления, что не обеспечивает возможности оперативно менять эти значения, тем самым не обеспечивается обработка произвольной части изображения.

Целью изображения является расширение класса решаемых задач за счет возможности поворота части изображения и его отдельных точек относительно произвольного центра поворота.

Сущностью изобретения является то, что в устройство для преобразования координат, содержащее регистр абсциссы, регистр ординаты, два регистра угла, два счетчика угла, счетчик дистанции и два дешифратора, причем выход первого счетчика угла соединен с входом второго дешифратора, выход счетчика дистанции соединен с входом первого дешифратора, выход первого аргумента устройства соединен с входом первого регистра угла, вход второго аргумента соединен с входом второго регистра угла, дополнительно введены регистр начального значения абсциссы, регистр начального значения ординаты, регистр смещения по абсциссе, регистр смещения по ординате, регистр дистанции, счетчик абсциссы, счетчик ординаты, третий дешифратор, два арифметических узла и блок управления, причем выход регистра абсциссы соединен со вторым входом первого арифметического узла и с третьим входом второго арифметического узла, выход регистра ординаты соединен со вторым входом второго арифметического узла и с третьим входом первого арифметического узла соединен с входом регистра абсциссы, выход второго арифметического узла соединен с входом регистра ординаты, выход регистра начального значения абсциссы соединен с информационным входом счетчика абсциссы, выход которого соединен с первым входом первого арифметического узла, четвертый вход которого соединен с выходом регистра смещения по абсциссе, выход регистра начального значения ординаты соединен с информационным входом счетчика ординаты, выход которого соединен с первым входом второго арифметического узла, четвертый вход которого соединен с выходом регистра смещения по ординате, входы начального значения абсциссы и ординаты устройства соединены с входами регистра начального значения абсциссы и регистра начального значения ординаты соответственно, входы смещения по абсциссе и по ординате устройства соединены с входами регистра смещения по абсциссе и регистра смещения по ординате соответственно, выход второго счетчика угла соединен с входом третьего дешифратора, выход первого дешифратора соединен с входом нулевого значения дистанции блока управления, выходы второго и третьего дешифратора соединены соответственно с входами нулевого значения большего и меньшего углов блока управления, вход значения дистанции устройства соединен с входом регистра дистанции, выход которого соединен с информационным входом счетчика дистанции, информационные выходы первого и второго регистров угла соединены соответственно с информационными входами первого и второго счетчиков угла, знаковые выходы первого и второго регистров угла соединены соответственно с входами знака большего угла и знака меньшего угла блока управления, вход разрешения счета устройства соединен с входом признака разрешения счета блока управления, выходы регистра абсциссы, регистра ординаты и готовности блока управления соединены с одноименными выходами устройства, первый тактовый выход блока управления соединен с входами записи первого и второго счетчиков угла, второй и третий тактовый выходы блока управления соединены со счетными входами первого и второго счетчиков угла соответственно, четвертый тактовый выход блока управления соединен со счетными входами счетчиков абсциссы и дистанции, пятый тактовый выход соединен с входами записи счетчиков абсциссы и дистанции и со счетным входом счетчика ординат, шестой тактовый выход соединен с синхронизирующими входами регистров абсциссы и ординаты, выходы режима блока управления с первого по четвертый соединены соответственно входами режима с первого по четвертый первого и второго арифметических узлов, первый и второй знаковые выходы блока управления соединены соответственно с знаковыми входами первого и второго арифметических узлов.

Арифметический узел состоит из четырех коммутаторов, двух сумматоров-вычитателей и трех элементов И, причем вход второго аргумента арифметического узла соединен с информационным входом первого коммутатора, выход которого соединен с первым информационным входом первого сумматора-вычитателя, второй информационный вход которого соединен с выходом второго коммутатора, информационный вход которого соединен с входом третьего аргумента арифметического узла, вход четвертого аргумента которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом первого сумматора-вычитателя, выход третьего коммутатора соединен с первым информационным входом второго сумматора-вычитателя, второй информационный вход которого соединен с входом второго аргумента арифметического узла, вход первого аргумента которого соединен с первым информационным входом четвертого коммутатора, второй информационный вход которого соединен с выходом второго сумматора-вычитателя, а выход четвертого коммутатора является выходом результата арифметического узла, знаковый вход которого соединен с управляющими входами первого и второго сумматора-вычитателей, вход первого режима арифметического узла соединен с первыми инверсными входами первого и второго элементов И и с прямым входом третьего элемента И, вход второго режима арифметического узла соединен с прямым входом первого элемента И, и со вторым и первым инверсными входами второго и третьего элементов И соответственно, вход третьего режима арифметического узла соединен со вторыми инверсными входами первого и третьего элементов И и с третьим инверсным входом второго элемента И, вход четвертого режима арифметического узла соединен с прямым входом второго элемента И и с третьими инверсными входами первого и третьего элементов И.

Блок управления устройства состоит из генератора тактовых импульсов, четырех триггеров и узла синхронизации, причем вход разрешения работы блока управления соединен с входом установки в единицу первого триггера, выход которого соединен с входом разрешения работы узла синхронизации, тактовый вход которого соединен с первым выходом генератора тактовых импульсов, второй вход которого соединен с входом установки в ноль второго и третьего триггеров, выходы которых соединены соответственно с первым и вторым управляющими входами узла синхронизации, установочные входы которого соединены соответственно с установочными входами блока управления, с первого по пятый выходы узла синхронизации являются соответственно пятью тактовыми выходами блока управления, шестой тактовый выход которого соединен с третьим выходом генератора тактовых импульсов, шестой и седьмой выходы узла синхронизации соединены соответственно с входами установки в единицу второго и третьего триггеров, восьмой выход узла синхронизации соединен с входом установки в единицу четвертого триггера и с входом установки в ноль первого триггера, выход которого соединен с входом установки в ноль четвертого триггера, выход которого является выходом готовности блока управления, выходы с девятого по двенадцатый узла синхронизации являются соответственно выходами режимов с первого по четвертый блока управления, а тринадцатый и четырнадцатый выходы узла синхронизации являются соответственно знаковыми выходами большего и меньшего блока управления.

Отличительным признаком изобретения является то, что в устройство дополнительно введены регистр начального значения абсциссы, регистр начального значения ординаты, регистр смещения по абсциссе, регистр смещения по ординате, регистр дистанции, счетчик абсциссы, счетчик ординаты, третий дешифратор, два арифметических узла и блок управления, причем выход регистра абсциссы соединен со вторым входом первого арифметического узла и с третьим входом второго арифметического узла, выход регистра ординаты соединен со вторым входом второго арифметического узла и с третьим входом первого арифметического узла, выход первого арифметического узла соединен с входом регистра абсциссы, выход второго арифметического узла соединен с входом регистра ординаты, выход регистра начального значения абсциссы соединен с информационным входом счетчика абсциссы, выход которого соединен с первым входом первого арифметического узла, четвертый вход которого соединен с выходом регистра смещения по абсциссе, выход регистра начального значения ординаты соединен с информационным входом счетчика ординаты, выход которого соединен с первым входом второго арифметического узла, четвертый вход которого соединен с выходом регистра смещения по ординате, входы начального значения абсциссы и ординаты устройства соединены с входами регистра начального значения абсциссы и регистра начального значения ординаты соответственно, входы смещения по абсциссе и по ординате устройства соединены с входами регистра смещения по абсциссе и регистра смещения по ординате соответственно, выход второго счетчика угла соединен с входом третьего дешифратора, выход первого дешифратора соединен с входом нулевого значения дистанции блока управления, выходы второго и третьего дешифратора соединены соответственно с входами нулевого значения большего и меньшего углов блока управления, вход значения дистанции устройства соединен с входом регистра дистанции, выход которого соединен с информационным входом счетчика дистанции, информационные выходы первого и второго регистров угла соединены соответственно с информационными входами первого и второго счетчиков угла, знаковые выходы первого и второго регистров угла соединены соответственно с входами знака большего угла и знака меньшего угла блока управления, вход разрешения счета устройства соединен с входом признака разрешения счета блока управления, выходы регистра абсциссы, регистра ординаты и готовности блока управления соединены с одноименными выходами устройства, первый тактовый выход блока управления соединен с входами записи первого и второго счетчиков угла, второй и третий тактовый выходы блока управления соединены со счетными входами первого и второго счетчиков угла соответственно, четвертый тактовый выход блока управления соединен со счетными входами счетчиков абсциссы и дистанции, пятый тактовый выход соединен с входами записи счетчиков абсциссы и дистанции и со счетным входом счетчика ординат, шестой тактовый выход соединен с синхронизирующими входами регистров абсциссы и ординаты, с первого по четвертый выходы режима блока управления соединены соответственно с первого по четвертый входы режима первого и второго арифметических узлов, первый и второй знаковые выходы блока управления соединены соответственно с знаковыми входами первого и второго арифметических узлов. Арифметический узел содержит четыре коммутатора, два сумматора-вычитателя и три элемента И, причем вход второго аргумента арифметического узла соединен с информационным входом первого коммутатора, выход которого соединен с первым информационным входом первого сумматора-вычитателя, второй информационный вход которого соединен с выходом второго коммутатора, информационный вход которого соединен с входом третьего аргумента арифметического узла, вход четвертого аргумента которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом первого сумматора-вычитателя, выход третьего коммутатора соединен с первым информационным входом второго сумматора-вычитателя, второй информационный вход которого соединен с входом второго аргумента арифметического узла, вход первого аргумента которого соединен с первым информационным входом четвертого коммутатора, второй информационный вход которого соединен с выходом второго сумматора-вычитателя, а выход четвертого коммутатора является входом результата арифметического узла, знаковый вход которого соединен с управляющими входами первого и второго сумматоров-вычитателей, вход первого режима арифметического узла соединен с первыми инверсными входами первого и второго элементов И и с прямым входом третьего элемента И, вход второго режима арифметического узла соединен с прямым входом первого элемента И и со вторым и первым инверсными входами второго и третьего элементов И, соответственно вход третьего режима арифметического узла соединен со вторыми инверсными входами первого и третьего элементов И и с третьим инверсным входом второго элемента И, вход четвертого режима арифметического узла соединен с прямым входом второго элемента И и с третьими инверсными входами первого и третьего элементов И. Блок управления содержит генератор тактовых импульсов, четыре триггера, и узел синхронизации, причем вход разрешения работы блока управления соединен с входом установки в единицу первого триггера, выход которого соединен с входом разрешения работы узла синхронизации, тактовый вход которого соединен с первым выходом генератора тактовых импульсов, второй вход которого соединен с входом установки в ноль второго и третьего триггеров, выходы которых соединены соответственно с первым и вторым управляющими входами узла синхронизации, установочные входы которого соединены соответственно с установочными входами блока управления, с первого по пятый выходы узла синхронизации являются соответственно пятью тактовыми выходами блока управления, шестой тактовый выход которого соединен с третьим выходом генератора тактовых импульсов, шестой и седьмой выходы узла синхронизации соединены соответственно с входами установки в единицу второго и третьего триггеров, восьмой выход узла синхронизации соединен с входом установки в единицу четвертого триггера и с входом установки в ноль первого триггера, выход которого соединен с входом установки в ноль четвертого триггера, выход которого является выходом готовности блока управления, выходы с девятого по двенадцатый узла синхронизации являются соответственно выходами режимов с первого по четвертый блока управления, а тринадцатый и четырнадцатый выходы узла синхронизации являются соответственно знаковыми выходами большего и меньшего блока управления.

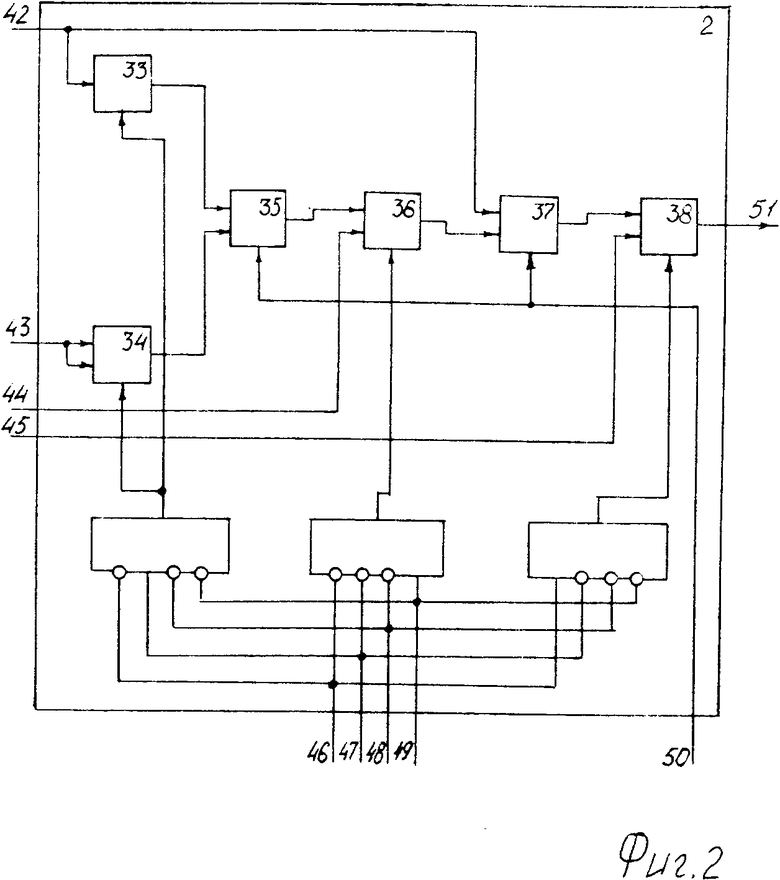

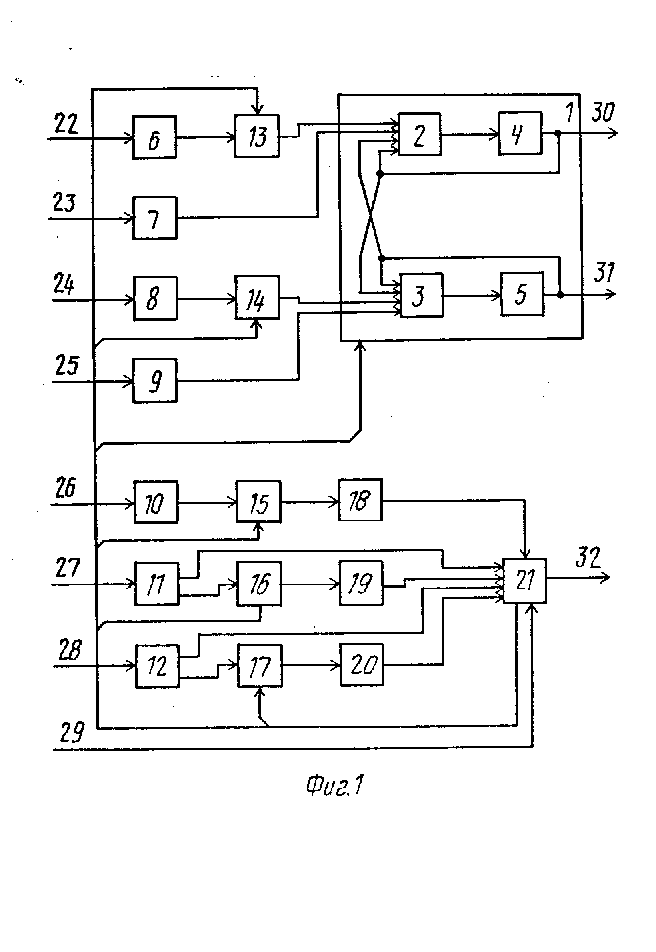

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - схема арифметического узла; на фиг. 3 - схема блока управления.

Устройство для преобразования координат содержит блок поворота вектора 1, состоящий из первого арифметического узла 2, второго арифметического узла 3, регистра абсциссы 4, регистра ординаты 5, а также регистр начального значения абсциссы 6, регистр смещения по абсциссе 7, регистр начального значения ординаты 8, регистр смещения по ординате 9, регистр дистанции 10, первый регистр угла 11, второй регистр угла 12, счетчик абсциссы 13, счетчик ординаты 14, счетчик дистанции 15, первый 16 и второй 17 счетчик угла, три дешифратора 18, 19 и 20, блок управления 21, вход начального значения абсциссы 22, вход значения смещения по абсциссе 23, вход начального значения ординаты 24, вход значения смещения по ординате 25, вход дистанции 26, вход первого аргумента 27, вход второго аргумента 28, вход разрешения счета 29, выход абсциссы 30, выход ординаты 31 и выход готовности 32, причем выход регистра абсциссы 4 соединен со вторым входом первого арифметического узла 2 и с третьим входом второго арифметического узла 3, выход регистра ординаты 5 соединен со вторым входом второго арифметического узла 3 и с третьим входом первого арифметического узла 2, выход первого арифметического узла 2 соединен с входом регистра абсциссы 4, выход второго арифметического узла 3 соединен с входом регистра ординаты 5, выход регистра начального значения абсциссы 6 соединен с информационным входом счетчика абсциссы 13, выход которого соединен с первым входом первого арифметического узла 2, четвертый вход которого соединен с выходом регистра смещения по абсциссе 7, выход регистра начального значения ординаты 8 соединен с информационным входом счетчика ординаты 14, выход которого соединен с первым входом второго арифметического узла 3, четвертый вход которого соединен с выходом регистра смещения по ординате 9, входы начального значения абсциссы 22 и ординаты 24 устройства соединены с входами регистров начального значения абсциссы 6 и ординаты 8 соответственно, входы смещений по абсциссе 23 и по ординате 25 устройства соединены с входами регистров смещения по абсциссе 7 и по ординате 9 соответственно. Выходы первого 11 и второго регистров угла соединены соответственно с информационными входами первого 16 и второго 17 счетчиков угла соответственно, знаковые выходы 11 и второго 12 регистров угла соединены соответственно с входами признака знака большего угла и признака знака меньшего угла блока управления 21, выходы первого 16 и второго 17 счетчиков угла соединены с входами второго 19 и третьего 20 дешифраторов соответственно, выход регистра дистанции 10 соединен с информационным входом счетчика дистанции 15, выход которого соединен с входом первого дешифратора 18, выход которого соединен с входом нулевого значения дистанции блока управления 21, выходы второго 19 и третьего 20 дешифраторов соединены соответственно с входами нулевого значения большего и меньшего углов блока управления 21, вход значения дистанции устройства 26 соединен с входом регистра дистанции 10, входы первого 27 и второго 28 аргументов устройства соединены соответственно с входами первого 11 и второго 12 регистров угла, вход разрешения счета 29 устройства соединен с входом разрешения счета блока управления 21, выходы регистра абсциссы 4, регистра ординаты 5 и готовности блока управления 21 соединены с одноименными выходами устройства 30, 31 и 32 соответственно, с первого по четвертый выходы режима блока управления 21 соединены соответственно с первого по четвертый входами режима первого 2 и второго 3 арифметических узлов, первый и второй знаковые выходы блока управления 21 соединены соответственно с знаковыми входами первого 2 и второго 3 арифметических узлов, первый тактовый выход блока управления 21 соединен с входами записи первого 16 и второго 17 счетчиков угла, второй и третий тактовые выходы блока управления 21 соединены со счетными входами первого 16 и второго 17 счетчиков угла соответственно, четвертый тактовый выход блока управления 21 соединен со счетными входами счетчиков абсциссы 13 и дистанции 15, пятый тактовый выход блока управления 21 соединен с входами записи счетчиков абсциссы 13 и дистанции 15 и со счетным входом счетчика ординат 14, шестой тактовый выход блока управления 21 соединен с синхронизирующими входами регистров абсциссы 4 и ординаты 5.

Арифметический узел 2 содержит первый коммутатор 33, второй коммутатор 34, первый сумматор вычитатель 35, третий коммутатор 36, второй сумматор-вычитатель 37, четвертый коммутатор 38, три элемента И 39, 40 и 41, которые имеют по три инверсных и по одному прямому входу. Имеются также входы с первого по четвертый аргументов 42, 43, 44 и 45, входы с первого по четвертый режимов 46, 47, 48, 49, знаковый вход 50, выход результата 51, причем выход коммутатора 33 соединен со сдвигом на К1 разрядов (К1 - константа итерации) в сторону младших разрядов с входом первого операнда сумматора вычитателя 35, выход которого и вход четвертого аргумента 44 соединены соответственно с входами первого и второго операндов коммутатора 36, вход второго аргумента 42 соединен с входом первого операнда коммутатора 33, на вход второго операнда которого всегда подается ноль, вход третьего аргумента 43 соединен со сдвигом на К2 разряда (К2 - константа итерации) в сторону младших разрядов с входом первого операнда коммутатора 34 и со сдвигом на К3 разряда (К3 - константа итерации) в сторону младших разрядов с входом второго операнда коммутатора 34, выход которого соединен с входом второго операнда сумматора вычитателя 35. Вход второго аргумента 42 и выход коммутатора 36 соединены соответственно с входами первого и второго операндов сумматора-вычитателя 37, выход которого и вход первого аргумента 45 соединены соответственно с входами первого и второго операндов коммутатора 38, выход которого соединен с выходами результата 51, выход элемента И 39 соединен с управляющими входами коммутаторов 33 и 34, выход элемента И 40 соединен с управляющим входом коммутатора 36, выход элемента И 41 соединен с управляющим входом коммутатора 38, вход первого режима 46 соединен с инверсными входами элементов И 39 и 40 и с прямым входом элемента И 40, вход второго режима 47 соединен с инверсными входами элементов И 40 и 41 и прямым входом элемента И 39, вход третьего режима 48 соединен с инверсными выходами элементов И 39, 40 и 41, вход четвертого режима 49 соединен с инверсными входами элементов И 39 и 41 и прямым входом элемента И 40, знаковый вход 50 соединен с управляющими входами сумматоров-вычитателей 35 и 37.

Арифметический узел 3 идентичен арифметическому узлу 2.

Блок управления 21 содержит первый 52, второй 53 и третий 54 триггеры, генератор импульсов 55, узел синхронизации 56, четвертый триггер 57. Вход разрешения счета 58 соединен с входом установки триггера 52, входы которого соединены с восьмым входом узла синхронизации 56 и с входом сброса триггера 57, с первого по пятый выходы узла синхронизации 56 соединены соответственно с входами нулевого значения большего угла 59, нулевого значения меньшего угла 60, нулевого значения дистанции 61, знака большего угла 62, знака меньшего угла 63, шестой и седьмой входы узла синхронизации 56 соединены соответственно с выходами триггеров 53 и 54, первый выход генератора 55 соединен с синхронизирующим входом узла 56, второй выход генератора 55 соединен с входами сброса триггеров 53 и 54, третий выход генератора 55 соединен с шестым тактовым выходом блока управления 21. С первого по пятый выходы узла синхронизации 56 соединены соответственно с первого по пятый тактовые выходы 64 блока управления 21, шестой и седьмой выходы узла 56 соединены соответственно с входами установки триггеров 53 и 54, восьмой выход узла синхронизации 56 соединен с входом сброса триггера 52 и с входом установки триггера 57, с девятого по двенадцатый выходы узла синхронизации 56 соответственно соединены с первого по четвертый выходы режима блока управления 21, тринадцатый и четырнадцатый выходы узла 56 соединены соответственно с выходами знака большего угла и знака меньшего угла блока управления 21, выход триггера 57 соединен с выходом готовности 32 блока управления 21.

Устройство функционирует следующим образом.

Работа устройства выражается формульными зависимостями:

(1)

(1)

и

(2)

(2)

Начальными значениями координат формульной зависимости (1) являются координаты точки, которую необходимо преобразовать. Начальными значениями координат в (2) являются конечные значения координат (1).

Для поворота одной точки зависимость (1) повторяется m, а (2) - n раз, причем m и n рассчитываются заранее на универсальной ЭВМ по формулам:

m= int(abs( α)/arcsin2-К2),

n= int(abs(abs( α)-arcsin2-К2˙m)/

/arcsin2-К3), (3) где α- угол поворота.

Значения и определяются углом и величиной поворота:

ζ1= sign α, ζ2= sign(abs( α)-m˙arcsin2-К2) ˙ ζ1 . (4)

После выполнения выражения (1) m раз и выражения (2) n раз, к полученным значениям координат прибавляются смещения , вычисляемые по формуле:

где Хц, Yц - координаты центра поворота.

где Хц, Yц - координаты центра поворота.

На этом цикл поворота одной точки заканчивается.

Для поворота всего изображения задаются начальные координаты и дистанция по абсциссе, т. е. ширина преобразуемого изображения. Цикл поворота изображения начинается с поворота точки с начальными координатами. Затем абсцисса наращивается, пока величина приращения не достигнет дистанции. Тогда по абсциссе опять берется для поворота для поворота начальное значение, а ордината наращивается. И так далее, пока не будет стоять сигнал "Разрешено" на входе в устройство. После того, как будет повернуто все изображение, сигнал "Разрешено" снимается и работа устройства прекращается.

Перед началом вычислений на входы начального значения абсциссы 22 и начального значения ординаты 24 устройства подаются соответствующие значения, которые записываются соответственно в регистры 6 и 8, на выходы 23 и 25 устройства соответственно подаются значения смещений по абсциссе и по ординате, которые записываются соответственно в регистры 7 и 9, на вход значения дистанции устройства 26 подается значение разности между максимальным и минимальным значением абсциссы, которое записывается в регистры 10, на входы 27 и 28 устройства подаются значения количества итераций по большим и по меньшим углам соответственно, которые записываются в регистр больших углов 11 и в регистр меньших углов 12 соответственно. Затем на входы записи счетчиков 16 и 17 подается сигнал с первого тактового выхода блока управления 21, на входы записи счетчиков 13 и 15 подается сигнал с пятого тактового выхода блока управления 21, а также при записи в регистр начального значения ординаты 8 информация переписывается в счетчик ординаты 14. Далее перед началом поворота очередной точки по достижению условия< Сч20>= 0 с дешифратора 20 поступает сигнал на блок управления 21, который вырабатывает сигналы при условии <Сч15>= 0 на первом и четвертом тактовом выходе и в счетчики 16 и 17 информация записывается заново, на счетный вход счетчика 13 поступает сигнал "1", на счетный вход счетчика 15 поступает сигнал "-1" и начинается обработка следующей точки, а в противном случае (<Сч15>≠0) с дешифратора 18 поступает сигнал на блок 21, которым вырабатываются сигналы на первом и пятом тактовом выходе, при которых в счетчиках 13, 15, 16 и 17 информация записывается заново, а счетчик 14 увеличивается на "1" и начинается обработка новой строки точек изображения. После каждого цикла поворота точки значение абсциссы подается с регистра 4 на выход 30 и значение ординаты подается с регистра 5 на выход 31 устройства и вырабатывается сигнал "Готовность" блока управления 21, подаваемый на выход 32 устройства.

Цикл обработки одной точки заключается в следующем. В первом такте на входы знаков большего и меньшего углов блока управления 21 подаются знаковые разряды с регистров 11 и 12 соответственно, и блок 21 вырабатывает сигналы на первом и втором знаковых выходах, которые подаются на знаковые входы первого 2 и второго 3 арифметических узлов. Кроме того, подается сигнал с первого выхода режима блока управления 21 подается на соответствующие входы первого 2 и второго 3 арифметических узлов, устанавливая те в режим Z= t1, загружая тем самым блок поворота вектора 1 значениями координат поворачиваемой точки, передаваемые со счетчиков 13 и 14 через арифметические узлы 6 регистры 4 и 5 соответственно. В последующие такты блок управления 21 вырабатывает сигнал второго выхода режима, устанавливая оба арифметических узла в режим Z= t2--t2˙2-К1±t3˙2-К2. Кроме того, в каждом такте содержимое счетчика 16 уменьшается на "1". По достижению <Сч16>= 0 блок управления 21 переключает арифметические узлы 2 и 3 в третий режим Z= t2±t3˙2-К3 и начинает подаваться сигнал "-1" с третьего тактового выхода блока 21 на счетный вход второго счетчика угла, до тех пор пока содержимое счетчика 17 не станет равным 0 (<Сч17>= 0), после чего блок управления переключает арифметические узлы 2 и 3 в четвертый режим Z= t2+ t4, тем самым прибавляя к полученным значениям значения смещений по абсциссе и ординате соответственно. Полученное значение абсциссы и ординаты подается на выход абсциссы 30 и выход ординаты 31 соответственно с регистров абсциссы 4 и ординаты 5. Одновременно выставляется сигнал "Готовность" на выходе 32. Цикл поворота одной точки закончился. Устройство ожидает сигнала разрешения счета на входе 29 для продолжения работы. После того как будут считаны координаты преобразованной точки устройство запускается на счет следующей точки. Цикл расчета точки повторяется до тех пор пока не будут преобразованы все точки.

Арифметический узел 2 функционирует следующим образом.

Арифметический узел обеспечивает четыре режима работы в зависимости от управляющих сигналов: , (6) где -t1, t2, t3, t4 - с первого по четвертый входы аргументов арифметического узла,

, (6) где -t1, t2, t3, t4 - с первого по четвертый входы аргументов арифметического узла,

Z - выход результата арифметического узла,

К1, К2, К3 - константы итераций.

Сигнал на знаковом входе 50 арифметического узла 2 устанавливает оба сумматора вычитателя 35 и 37 в режим суммирования, а отсутствие - в режим вычитания. В зависимости от того, какой из четырех входов режима 46, 47, 48 или 49 подается сигнал, арифметический узел 2 устанавливается один из четырех возможных режимов. Элементы И 39, 40 и 41 в зависимости от сигнала на входах 46, 47 48 и 49 управляют коммутаторами 33, 34, 36 и 38. При подаче сигнала на входе 46 четвертый коммутатор 38 передает значение с первого входа 45 узла 2 на выход 51, реализуя тем самым функцию Z= t1. При подаче сигнала на вход 47 через коммутатор 33 значение, подаваемое на второй вход 42, передается со сдвигом на К1 разрядов в сторону младших разрядов на первый вход сумматора вычитателя 35, коммутатор 34 передает значение с третьего входа 43 узла 2 на второй вход сумматора вычитателя 35 со сдвигом на К2 разрядов в сторону младших разрядов, коммутатор 36 передает результат с выхода сумматора вычитателя 35 на второй вход сумматора вычитателя 37, на первый вход которого подается значение со второго входа 42, и результат с выхода которого передается коммутатором 38 на выход 51 арифметического узла 2, реализуя тем самым функцию Z= t2-t2˙2±t3. При подаче сигнала на вход 48 узла 2 коммутатор 33 подает "0" на первый вход сумматора вычитателя 35, на второй вход которого через коммутатор 34 подается значение с входа 43 со сдвигом на К3 разряда в сторону младших разрядов, результат с выхода сумматора вычитателя 35 через коммутатор 36 подается на второй вход сумматора вычитателя 37, на первый вход которого подается, значение с входа 42, а результат с выхода через коммутатор 38 подается на выход 51, реализуя тем самым функцию Z= t2±t3˙2-К3. При подаче сигнала на вход 49 коммутатор 36 с входа 44 передает значение на второй вход сумматора вычитателя 37, результат с выхода которого подается через коммутатор 38 на выход узла 2, реализуя тем самым функцию Z= t2+t4. Таким же образом реализуются все четыре функции арифметического узла 3.

Блок управления 21 функционирует следующим образом.

При подаче сигнала на вход 58 включается триггер 52, выключается триггер 57, сигнал "Готовность" на выходе 32 снимается и начинается очередной цикл поворота точки. В зависимости от состояния входов 59, 60 и 61, а также состояния триггеров 53 и 54 на выходах режима узла синхронизации 56 выставляется сигнал соответствующего режима арифметических узлов 2 и 3. В зависимости от состояния входов знаков больших 62 и меньших 63 углов, а также с учетом режима арифметического узла на знаковых, выходах узла 56 выставляются соответствующие сигналы. Во втором режиме выходы знаков блока управления 21 соответствуют сигналу на знаковом входе больших углов 62, а в третьем - соответственно сигналу на знаковом входе меньших углов 63. Триггеры 53 и 54 устанавливаются в зависимости от входных состояний и от предыдущих состояний узла синхронизации 56, что обеспечивается генератором импульсов 55, с первого и второго выхода которого импульсы подаются в противофазе соответственно на синхронизирующим входом узла 56 и на входы сброса триггеров 53 и 54, таким образом к моменту смены состояния триггеров 53 и 54 состояния их входов имеют установившееся значение. Кроме того импульсы, вырабатываемые на третьем выходе генератора 55, поступают на шестой тактовый выход блока управления 21, а остальные тактовые импульсы на тактовых выходах блока 21 вырабатываются узлом 56 из импульсов, поступающих на вход синхронизации узла 56. Устройство преобразования координат прекращает функционирование, если на вход 58 не подается очередной сигнал "Разрешение счета".

(56) Авторское свидетельство СССР N 1695294, кл. G 06 F 7/548, 1989.

Авторское свидетельство СССР N 1295386, кл. G 06 F 7/544, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| Устройство для преобразования координат | 1989 |

|

SU1695294A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА | 1998 |

|

RU2125291C1 |

| Устройство для преобразования координат | 1985 |

|

SU1295386A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ МАТРИЦ | 2000 |

|

RU2168760C1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для деления | 1980 |

|

SU949653A1 |

| Многофункциональный преобразователь | 1986 |

|

SU1429128A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

Изобретение относится к вычислительной технике, а именно к устройствам преобразования координат, и может быть использовано в специализированных вычислителях при преобразовании адресов телевизионного дисплея. Цель изобретения - расширение класса решаемых задач за счет возможности поворота части изображения и его отдельных точек относительно произвольного центра поворота. Устройство для преобразования координат содержит блок 1 поворота вектора, состоящий из двух арифметических узлов 2, 3, регистров 4, 5, абсциссы и ординаты с соответствующими функциональными связями, а также регистр 6 начального значения абсциссы, регистр 7 смещения по абсциссе, регистр 8 начального значения ординаты, регистр 9 смещения по ординате, регистр 10 дистанции, два регистра 11, 12 угла, счетчик 13 асбциссы, счетчик 14 ординаты, счетчик 15 дистанции, два счетчика 16, 17 угла, три дешифратора 18, 19, 20 и блок 21 управления, соединенные между собой функционально. 2 з. п. ф-лы, 3 ил.

Авторы

Даты

1994-02-15—Публикация

1991-04-02—Подача