тов И, блок 10 элементов ИЛИ, первый 11 и второй 12 элементы И, элемент ИЛИ-НЕ 13, элемент ИЛИ 14, 2+п-разрядную входную- выходную шину 15 данных, входы 16 двух младших разрядов кода одного из сомножителей операции умножения кодов без знаков, вход 17 управления вводом данных, вход 18 старшего и вход 19 младшего разрядов двухразрядного кода операции, вход 28 выбора устройства, четыре информационных выхода (с первого 21 по четвертый 24) и управляющий выход 34. Устройство может

быть использовано при построении функционально ориентированных процессоров (ФОЛ) с программируемой логикой, алгоритмы которых реализуются с широким использованием модификаций операций умножения и деления, например, при построении ФОП управления векторным или растровым электронно-лучевым индикатором устройства отображения информационной сложной информации системы типа метеорадиолокатора. 2 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1728860A1 |

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Устройство для вычисления массы нефте-пРОдуКТОВ B РЕзЕРВуАРАХ | 1979 |

|

SU845159A1 |

Устройство для деления относится к вычислительной технике и предназначено для выполнения операции умножения кодов без знаков, операции умножения в прямом коя (г) де, операции деления в прямом коде с определением делимого и делителя, не меньшего делимого по модулю, и операции деления в прямом коде по заданным делимому и делителю. Цель изобретения - расширение класса решаемых задач за счет обеспечения дополнительных возможностей выполнения операции умножения кодов без знаков, операции умножения в прямом коде и операции деления в прямом коде с определением делимого и делителя, не меньшего делимого по модулю. Устройство содержит блок 1 управления, умножитель 2, сумматор 3. регистр 4, блок 5 памяти. Новым в устройстве является то, что Оно содержит формирователь 6 информационных сигналов, компаратор 7, коммутатор 8, блок 9 злеменСО С 2 ON СО XJ 00

Изобретение относится к вычислительной технике, предназначено для выполнения операции умножения кодов без знаков, операции умножения в прямом коде, операции деления в прямом коде с определением делимого и делителя не меньше делимого по модулю и операции деления в прямом коде по заданным делимому и делителю и может быть использовано при построении функционально ориентированных процессоров с программируемой логикой, алгорит- мы которых реализуются с широким использованием модификаций операций умножения и деления, например, при построении функционально ориентированного процессора (ФОП) управления векторным или растровым электронно-лучевым индикатором устройства отображения информации (УОИ) сложной инфдрмацион- ной системы типа метеорадиолокатора (МРЛ).

Известный индикатор на электроннолучевой трубке с двухкоординатным электромагнитным управлением положением луча электронно-лучевой трубки и модуляцией его по яркости, клавиатуру для управления режимами функционирования УОИ, датчик координат маркера, формирователь кодограмм оператора и ФОП для связи УОИ с другими подсистемами МРЛ и управления индикатором в процессе синтеза информационной модели обстановки в зоне обзора МРЛ, причем ФОП содержит ряд устройств, в их числе цифро-аналоговый формирователь сигналов управления индикатором, устройство синхронизации и временных программ, устройство программного управления, запоминающее устройство оперативной и постоянной информации, микропроцессор для выполнения логических и коротких арифметических операций, устройство для быстрого выполнения требуемых модификаций операций умножения и

деления (с помощью этих операций в ФОП выполняются с требуемыми быстродействием и точностью все операции преобразования координат, например прямоугольных

координат в полярные координаты, полярных координат в прямоугольные координаты, прямоугольных координат при повороте осей, вычисление высоты и т.п.). устройство ввода-вывода и шины данных, адреса и управления.

Цель изобретения - расширение класса решаемых задач путем обеспечения дополнительных возможностей выполнения операции умножения кодов без знаков,

операции умножения в прямом коде и операции деления в прямом коде с определением делимого и делителя не меньшего делимого по модулю.

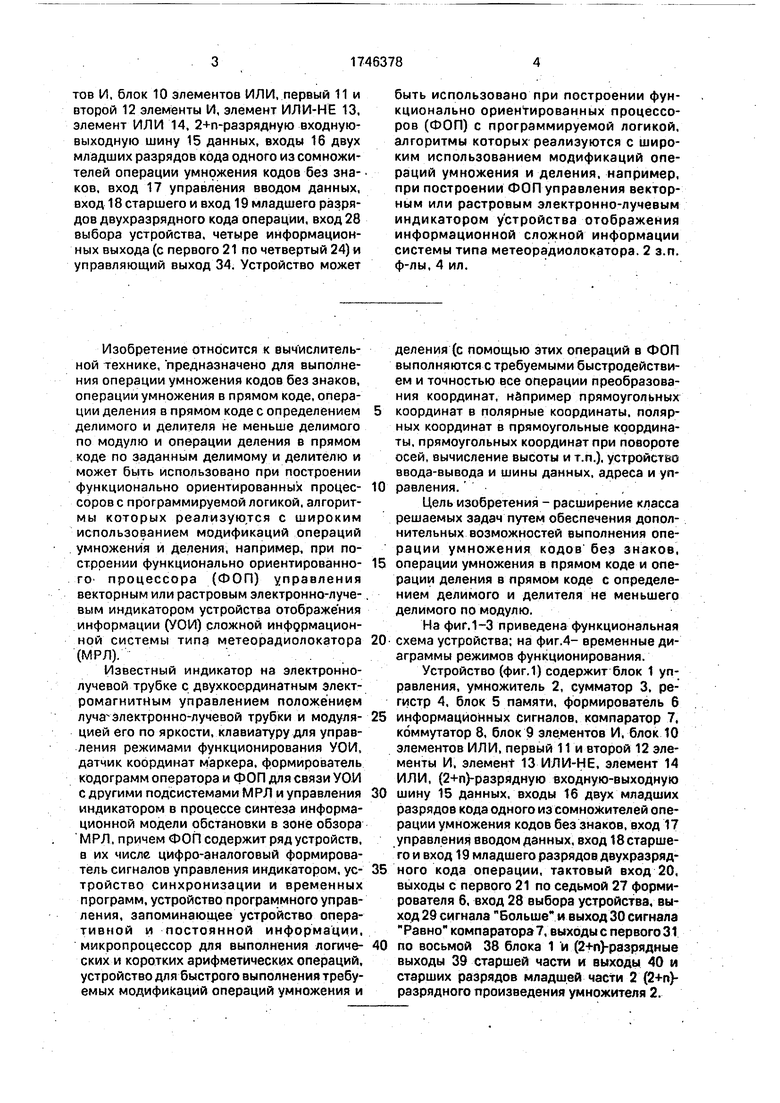

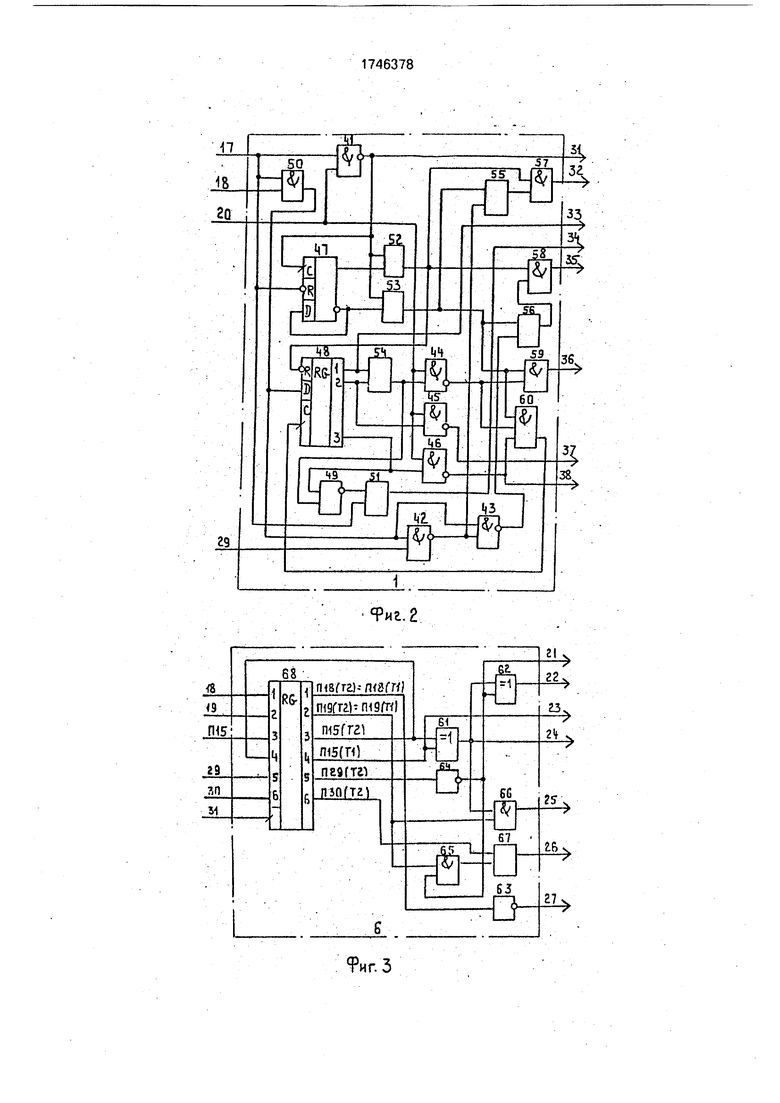

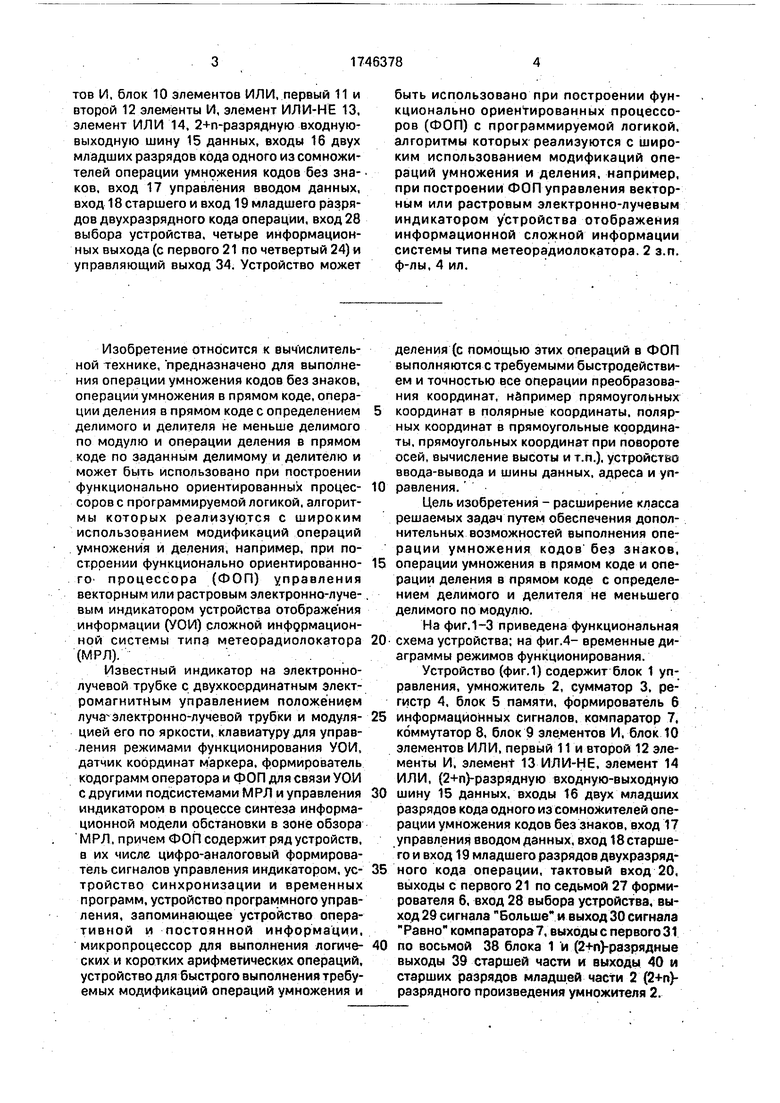

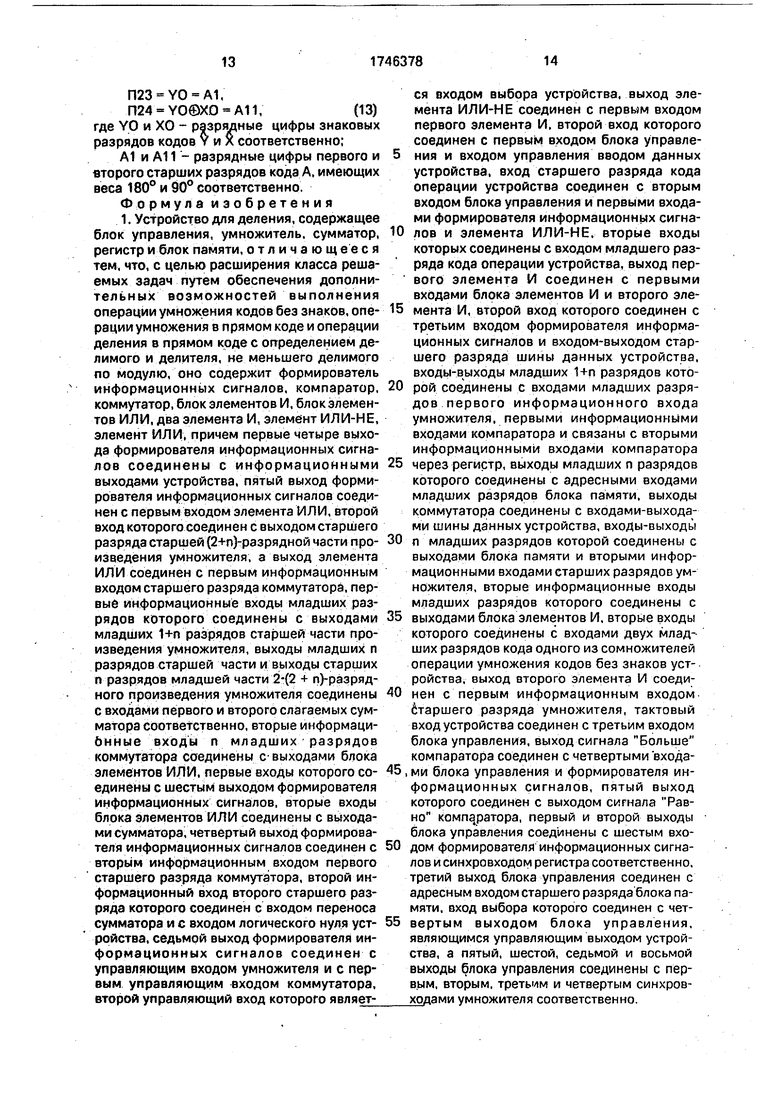

На фиг.1-3 приведена функциональная

- схема устройства; на фиг.4- временные диаграммы режимов функционирования.

Устройство (фиг.1) содержит блок 1 управления, умножитель 2, сумматор 3, регистр 4. блок 5 памяти, формирователь 6

информационных сигналов, компаратор 7, коммутатор 8, блок 9 элементов И, блок 10 элементов ИЛИ, первый 11 и второй 12 элементы И. элемент 13 ИЛИ-НЕ, элемент 14 ИЛИ, (2+п)-разрядиую входную-выходную

шину 15 данных, входы 16 двух младших разрядов кода одного из сомножителей операции умножения кодов без знаков, вход 17 управления вводом данных, вход старшего и вход 19 младшего разрядов двухразрядного кода операции, тактовый вход 20, выходы с первого 21 по седьмой 27 формирователя 6, вход 28 выбора устройства, выход 29 сигнала Больше и выход 30 сигнала Равно компаратора7, выходы с первого 31

по восьмой 38 блока 1 и (2+п)-разрядные выходы 39 старшей части и выходы 40 и старших разрядов младшей части 2 (2+п)- разрядного произведения умножителя 2.

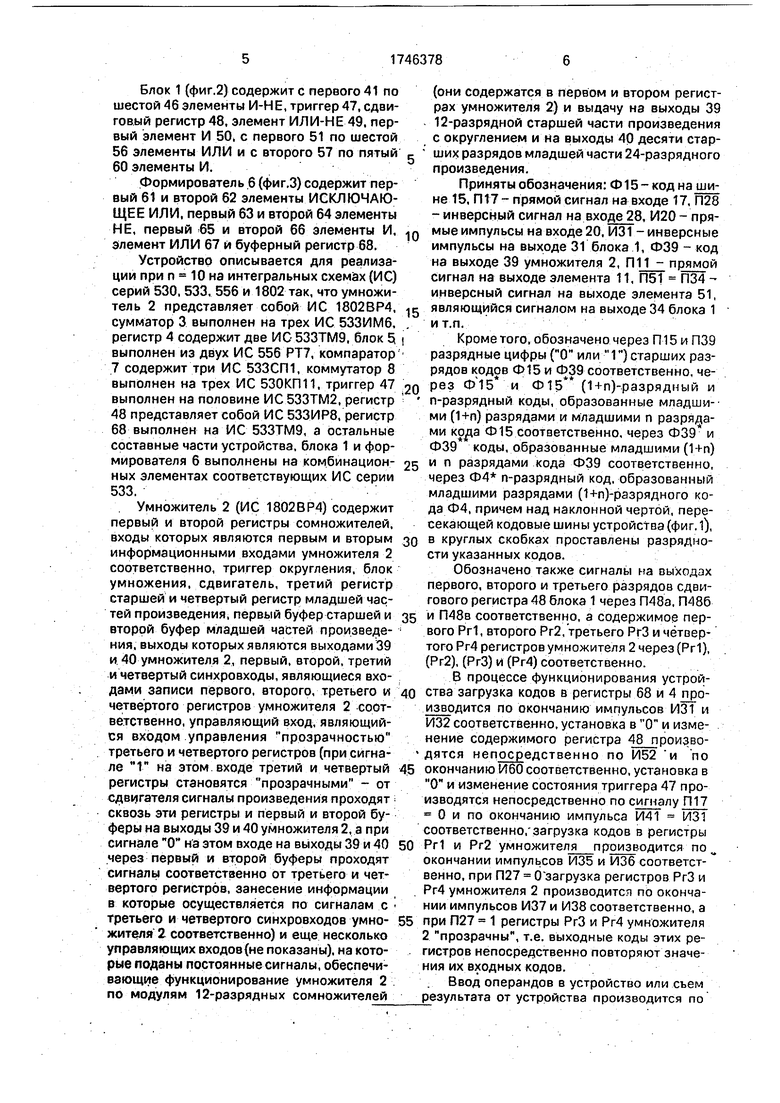

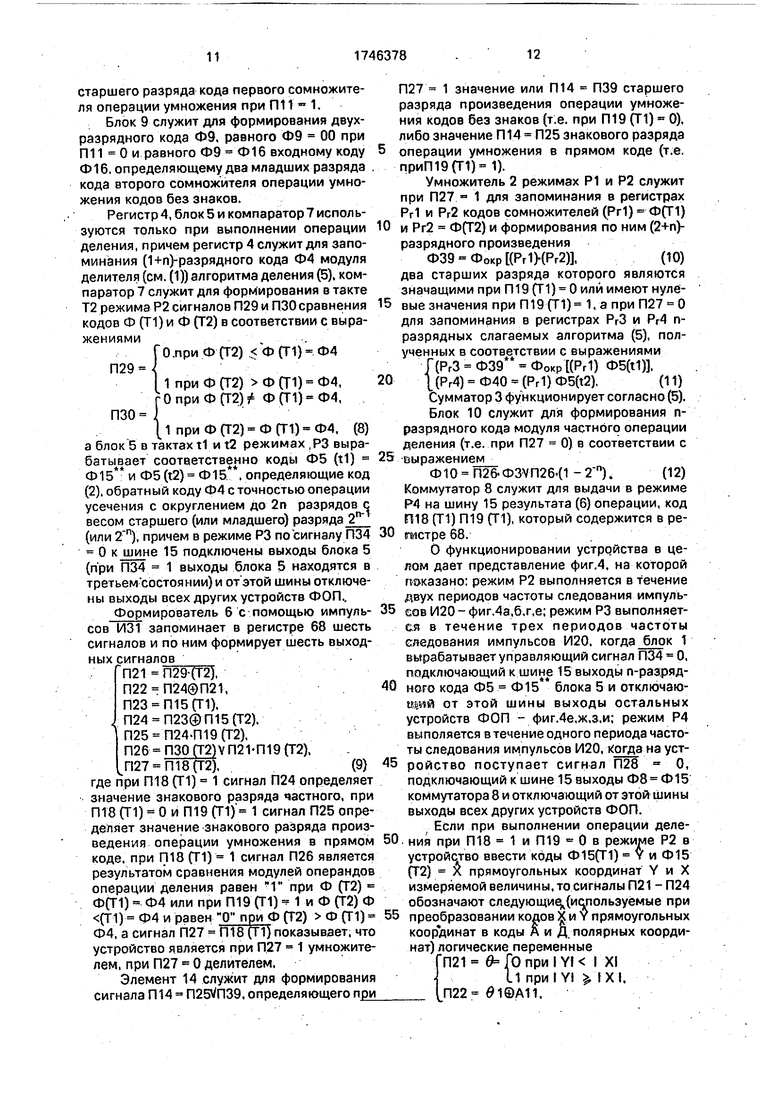

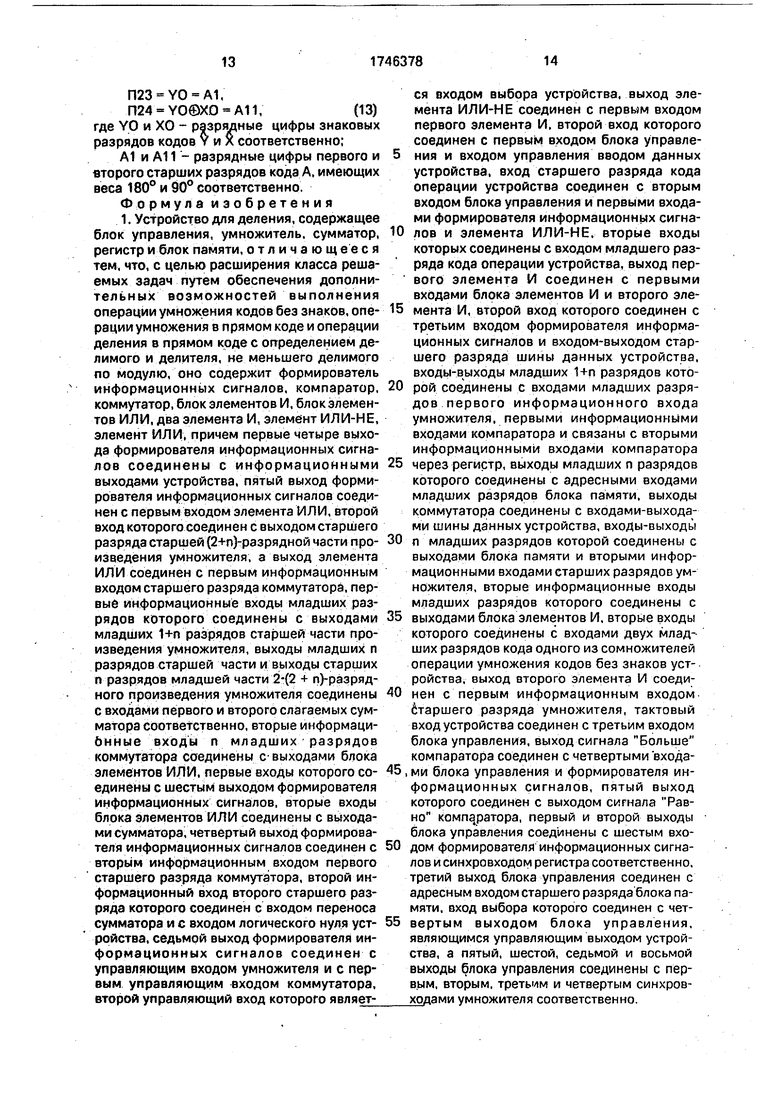

Блок 1 (фиг.2) содержит с первого 41 по шестой 46 элементы И-НЕ, триггер 47, сдвиговый регистр 48, элемент ИЛ И-НЕ 49. первый элемент И 50, с первого 51 по шестой 56 элементы ИЛИ и с второго 57 по пятый 60 элементы И.

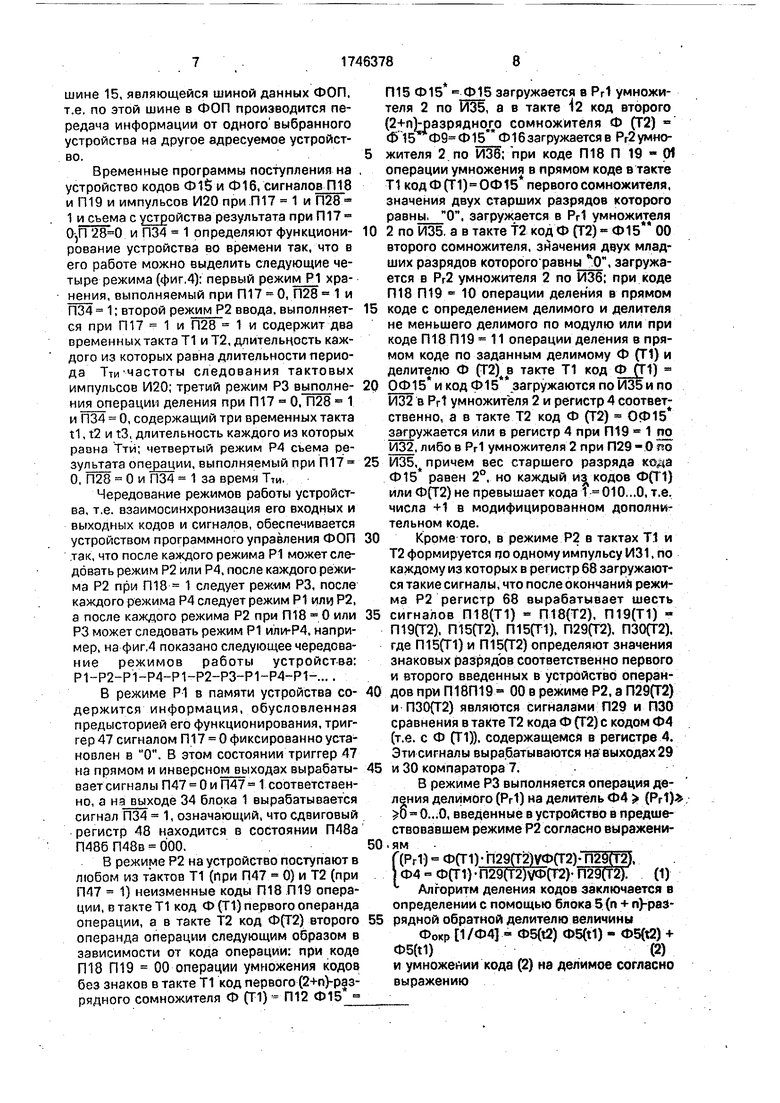

Формирователь 6 (фиг.З) содержит первый 61 и второй 62 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 63 и второй 64 элементы НЕ, первый 65 и второй 66 элементы И, элемент ИЛИ 67 и буферный регистр 68.

Устройство описывается для реализации при п 10 на интегральных схемах (ИС) серий 530, 533, 556 и 1802 так, что умножитель 2 представляет собой ИС 1802ВР4, сумматор 3 выполнен на трех ИС 533ИМ6, регистр 4 содержит две ИС 533ТМ9, блок 5, выполнен из двух ИС 556 РТ7, компаратор 7 содержит три ИС 533СП1, коммутатор 8 выполнен на трех ИС 530КП11, триггер 47 выполнен на половине ИС 533ТМ2, регистр 48 представляет собой ИС 533ИР8, регистр 68 выполнен на ИС 533ТМ9, а остальные составные части устройства, блока 1 и формирователя 6 выполнены на комбинацией- ных элементах соответствующих ИС серии 533.

Умножитель 2 (ИС 1802ВР4) содержит первый и второй регистры сомножителей, входы которых являются первым и вторым информационными входами умножителя 2 соответственно, триггер округления, блок умножения, сдвигатель, третий регистр старшей и четвертый регистр младшей частей произведения, первый буфер старшей и второй буфер младшей частей произведения, выходы которых являются выходами 39 и 40 умножителя 2, первый, второй, третий и четвертый синхровходы, являющиеся входами записи первого, второго, третьего и четвертого регистров умножителя 2 соответственно, управляющий вход, являющийся входом управления прозрачностью третьего и четвертого регистров (при сигнале 1 на этом входе третий и четвертый регистры становятся прозрачными - от сдвигателя сигналы произведения проходят сквозь эти регистры и первый и второй буферы на выходы 39 и 40 умножителя 2, а при сигнале О на этом входе на выходы 39 и 40 через первый и второй буферы проходят сигналы соответственно от третьего и четвертого регистров, занесение информации в которые осуществляется по сигналам с третьего и четвертого синхровходов умно- жителя 2 соответственно) и еще несколько управляющих входов (не показаны), на которые поданы постоянные сигналы, обеспечивающие функционирование умножителя 2 по модулям 12-разрядных сомножителей

(они содержатся в первом и втором регистрах умножителя 2) и выдачу на выходы 39 12-разрядной старшей части произведения с округлением и на выходы 40 десяти старших разрядов младшей части 24-разрядного произведения.

Приняты обозначения: Ф15-коднаши- не 15, П17 - прямой сигнал на входе 17, П28 - инверсный сигнал на входе 28, И20 - прямые импульсы на входе 20, И31 - инверсные импульсы на выходе 31 блока 1, Ф39 - код на выходе 39 умножителя 2, П11 - прямой сигнал на выходе элемента 11, П51 П34 - инверсный сигнал на выходе элемента 51, являющийся сигналом на выходе 34 блока 1 и т.п.

Кроме того, обозначено через П15 и П39 разрядные цифры (О или Г)старших разрядов кодов Ф15 и Ф39 соответственно, через Ф15 и Ф15 (1+п)-разрядный и n-разрядный коды, образованные младшими (1+п) разрядами и младшими п разрядами KOjfla Ф15 соответственно, через Ф39 и Ф39 коды, образованные младшими (1+п) и п разрядами кода Ф39 соответственно, через Ф4 n-разрядный код. образованный младшими разрядами (1+п)-разрядного кода Ф4, причем над наклонной чертой, пересекающей кодовые шины устройства (фиг. 1), в круглых скобках проставлены разрядности указанных кодов.

Обозначено также сигналы на выходах первого, второго и третьего разрядов сдвигового регистра 48 блока 1 через П48а. ГИ86 и П48в соответственно, а содержимое первого Рг1, второго Рг2, третьего РгЗ и четвертого Рг4 регистров умножителя 2 через (Рг1), (Рг2), (РгЗ) и (Рг4) соответственно.

В процессе функционирования устройства загрузка кодов в регистры 68 и 4 производится по окончанию импульсов И31 и И32 соответственно, установка в О и изменение содержимого регистра 48 произво- дятся непосредственно по И52 и по окончанию И60 соответственно, установка в О и изменение состояния триггера 47 производятся непосредственно по сигналу П17 0 и по окончанию импульса И41 И31 соответственно, загрузка кодов в регистры Рг1 и Рг2 умножителя производится по окончании импульсов ИЗБ и И36 соответственно, при П27 О загрузка регистров РгЗ и Рг4 умножителя 2 производится по окончании импульсов И37 и И38 соответственно, а при П27 1 регистры РгЗ и Рг4 умножителя 2 прозрачны, т.е. выходные коды этих регистров непосредственно повторяют значения их входных кодов.

Ввод операндов в устройство или съем результата от устройства производится по

шине 15, являющейся шиной данных ФОП, т.е. по этой шине в ФОП производится передача информации от одного выбранного устройства на другое адресуемое устройство.

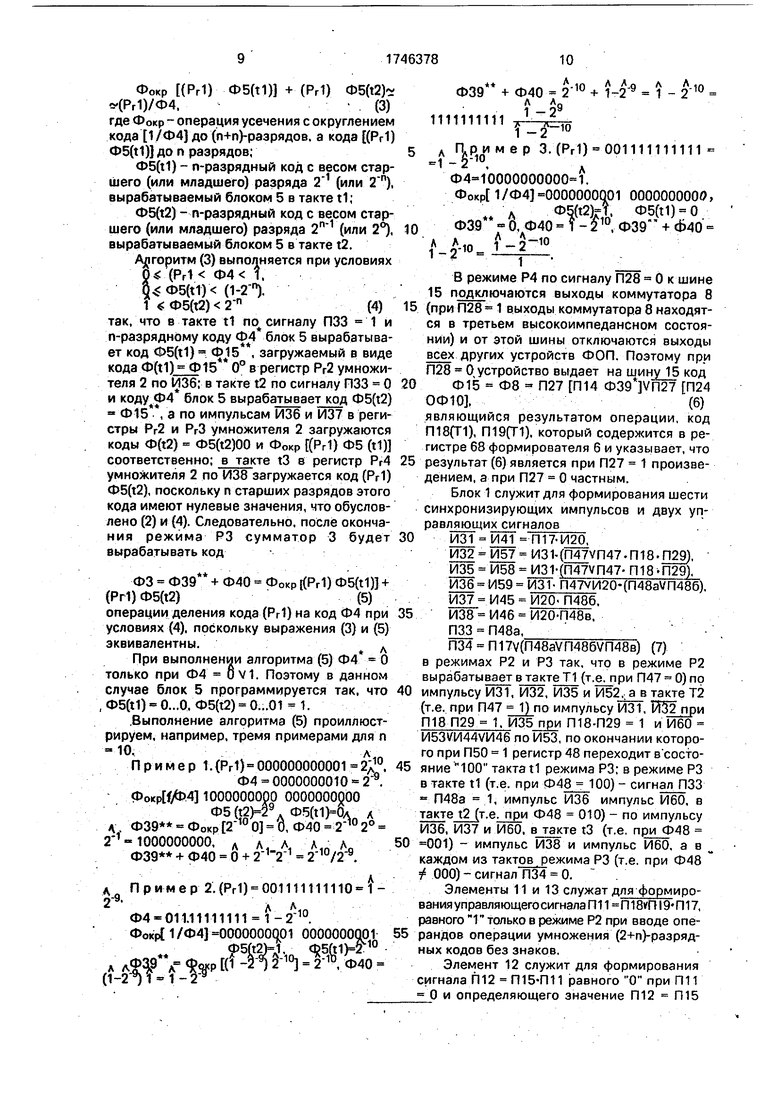

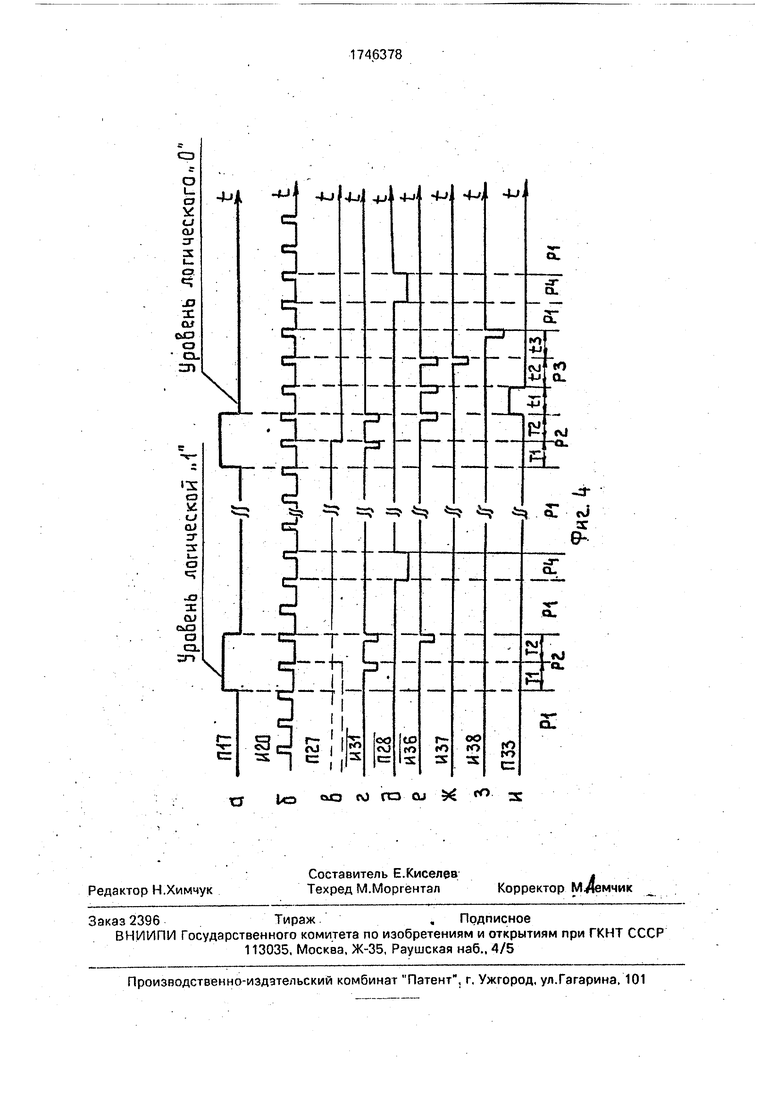

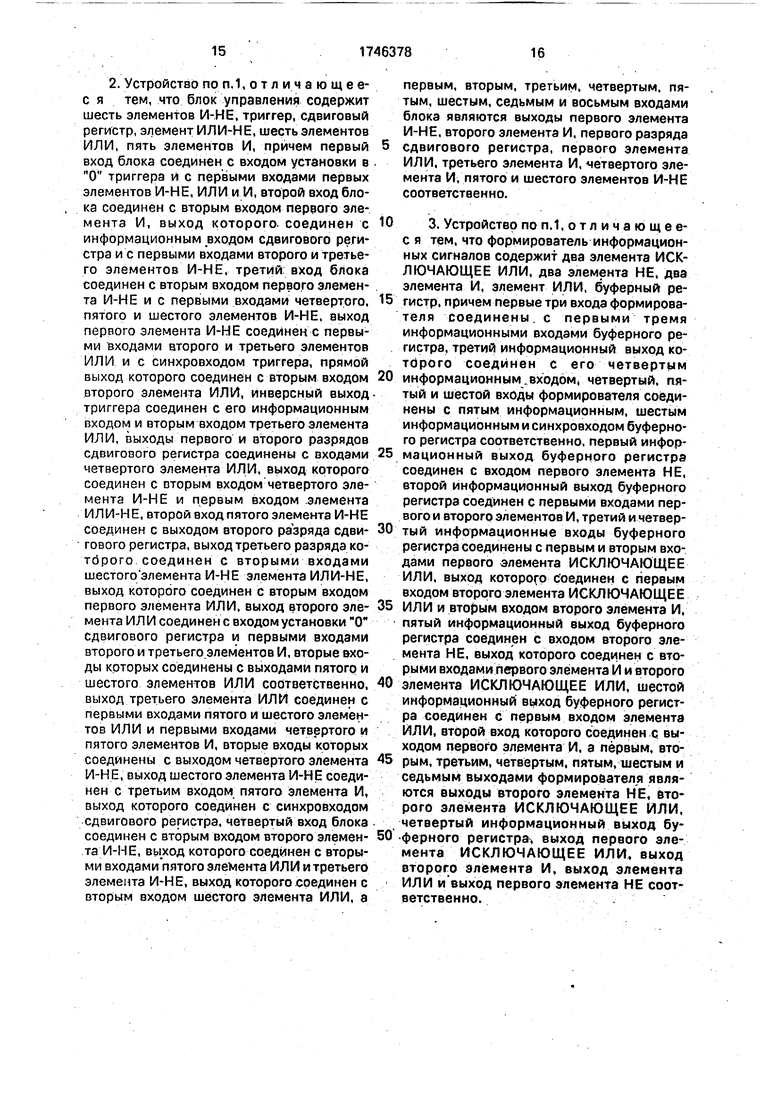

Временные программы поступления на устройство кодов Ф1б и Ф16, сигналов П18 и П19 и импульсов И20 при П17 1 и П28 - и сьема с устройства результата при П17 0,П и П34 1 определяют функционирование устройства во времени так, что в его работе можно выделить следующие четыре режима (фиг.4): первый режим Р1 хранения, выполняемый при П17 О, П28 1 и П34 1; второй режим Р2 ввода, выполняется при П17 1 и П28 1 и содержит два временных такта Т1 и Т2, длительность каждого из которых равна длительности периода Тти частоты следования тактовых импульсов 1420; третий режим РЗ выполнения операции деления при П17 О, П28 1 и П34 0, содержащий три временных такта t1, t2 и t3, длительность каждого из которых раина Тти; четвертый режим Р4 съема результата операции, выполняемый при П17 О, П28 0 и П34 1 за время Т™.

Чередование режимов работы устройства, т.е. взаимосинхронизация его входных и выходных кодов и сигналов, обеспечивается устройством программного управления ФОП так, что после каждого режима Р1 может следовать режим Р2 или Р4, после каждого режима Р2 при П18 1 следует режим РЗ, после каждого режима Р4 следует режим Р1 или Р2, а после каждого режима Р2 при П18 0 или РЗ может следовать режим Р1 или-Р4, например, на фиг,4 показано следующее чередование режимов работы устройства: Р1-Р2-Р1-Р4-Р1-Р2-РЗ-Р1-Р4-Р1-....

В режиме Р1 в памяти устройства содержится информация, обусловленная предысторией его функционирования, триггер 47 сигналом П17 0 фиксированно установлен в О. В этом состоянии триггер 47 на прямом и инверсном выходах вырабатывает сигналы П47 0 и П47 1 соответственно, а на выходе 34 блока 1 вырабатывается сигнал П34 1, означающий, что сдвиговый регистр 48 находится в состоянии П48а П486 П48в 000.

В режиме Р2 на устройство поступают в любом из тактов Т1 (при П47 « 0) и Т2 (при П47 1) неизменные коды П18 П19 операции, в такте Т1 код Ф (Т1) первого операнда операции, а в такте Т2 код Ф(Т2) второго операнда операции следующим образом в зависимости от кода операции: при коде П18 П19 00 операции умножения кодов без знаков в такте Т1 код первого (2+п)-раз- рядного сомножителя Ф (Т1) - П12 Ф15 g

0

П15 Ф15 Ф15 загружается в Рг1 умножителя 2 по И35, а в такте 2 код второго (2+п)-разрядно)г;о сомножителя Ф (Т2) Ф 15 Ф9 Ф 16 загружается в Рг2 умно- жителя 2 по ИЗб; при коде П18 П 19-01 операции умножения в прямом коде в такте Т1 код Ф(Т1)ОФ15 первого сомножителя, значения двух старших разрядов которого равны, О, загружается в РГ1 умножителя 2 по ИЗб. а в такте t2 код Ф (Т2) Ф15 00

второго сомножителя, значения двух младших разрядов которого равны 0, загружается в РГ2 умножителя 2 по И36; при коде П18 П19 10 операции деления в прямом

5 коде с определением делимого и делителя не меньшего делимого по модулю или при коде П18П19 11 операции деления в прямом коде по заданным делимому Ф (Т1) и делителю Ф (Т2)в такте Т1 код )

0 РФ 15 и код Ф15 загружаются по ИЗб и по И32 в Рг1 умножителя 2 и регистр 4 соответственно, а в такте Т2 код Ф (Т2) ОФ15 загружается или в регистр 4 при П19 ° 1 по И32. либо в РГ1 умножителя 2 при П29 -0 по

5 И35% причем вес старшего разряда кола Ф15 равен 2°. но каждый из кодов Ф(Т1) или Ф(Т2) не превышает кода 1 010...О, т.е. числа +1 в модифицированном дополнительном коде.

0 Кроме того, в режиме Р2 в тактах Т1 и Т2 формируется по одному импульсу И31, по каждому из которых в регистр 68 загружаются такие сигналы, что после окончания режима Р2 регистр 68 вырабатывает шесть

5 сигналов П18(Т1) - П18(Т2). П19(Т1) - П19(Т2), П15СТ2), П15(Т1), П29(Т2). ПЗО(Т2), где П15(Т1) и П15(Т2) определяют значения знаковых разрядов соответственно первого и второго введенных в устройство операн0 дов при П18П19 - 00 в режиме Р2, а П29(Т2) и ПЗО(Т2) являются сигналами П29 и ПЗО сравнения в такте Т2 кода Ф (Г2) с кодом Ф4 (т.е. с Ф (Т1)), содержащемся в регистре 4. Эти сигналы вырабатываются на выходах 29

5 и 30 компаратора 7,

В режиме РЗ выполняется операция деления делимого (Рг1) на делитель Ф4 (Prt) 0 0...О, введенные в устройство в предшествовавшем режиме Р2 согласно выражени0 ям

(РГ1) - Ф(Т1) П29(Т2)УФСГ2)- П29(Т2). Ф4 - ФСГ1) -П29СТ2)УФСТ2)- П29(Т2). (1) Алгоритм деления кодов заключается в определении с помощью блока 5 (п + п)-раз5 рядной обратной делителю величины

Фокр 1/Ф4 - Ф5(12) Ф5(П) - Ф5(Т2) + Ф5(1)(2)

и умножении кода (2) на делимое согласно выражению

. Я

f

Фокр (Рг1) Ф5(г1) + (РГ1) Ф5(12) ЦРг1)/Ф4, (3)

где Фокр - операция усечения с округлением кода 1/Ф4 до (п+п)-разрядов. а кода (Рг1) Ф5(т1)} до п разрядов;

Ф5(11) - n-разрядный код с весом старшего (или младшего) разряда 21 (или 2 п), вырабатываемый блоком 5 в такте t1;

Ф5(12) - n-разрядный код с весом старшего (или младшего) разряда (или 2, вырабатываемый блоком 5 в такте t2.

Алгоритм (3) выполняется при условиях б« (РгК Ф4 1. (t1) (1-2-).

1 «Ф5(|2)2 п(4)

так, что в такте t1 по+ сигналу ПЗЗ 1 и n-разрядному коду Ф4 блок 5 вырабатывает код Ф5(т1) Ф15 , загружаемый в виде кода Ф(|1) Ф15 0° в регистр РГ2 умножителя 2 по ИЗб; в такте t2 по сигналу ПЗЗ - 0 и коду Ф4 блок 5 вырабатывает код Ф5(т2) Ф15 , а по импульсам И36 и И37 в регистры Рг2 и РГ3 умножителя 2 загружаются коды Ф(12) - Ф5(12)00 и Фокр (Рг1) Ф5 (t1) соответственно; в такте t3 в регистр РГ4 умножителя 2 по И38 загружается код (РГ1) Ф5(|2), поскольку п старших разрядов этого кода имеют нулевые значения, что обусловлено (2) и (4). Следовательно, после окончания режима РЗ сумматор 3 будет вырабатывать код

ФЗ Ф39 + Ф40 Фокр (Рг1) Ф5(И) + (Рг1) Ф5(т2)(5)

операции деления кода (Рг1) на код Ф4 при условиях (4), поскольку выражения (3) и (5) эквивалентны. Л

При выполнении алгоритма (5) Ф4 О

только при Ф4 О V1. Поэтому в данном

случае блок 5 программируется так, что

, Ф5(И) 0...0, Ф5(т2) 0..,01 1.

Выполнение алгоритма (5) проиллюстрируем, например, тремя примерами для п - Ю.л..

Пример 1.(РГ1} 000000000001 2Я10.

о У

Ф4 0000000010 2 Фокр(уФ4 1000000000 0000000000

Ф5(й)-39 лФ-5( л Ф39 - Фокр 0 О, Ф40 2°

2 1 « 1000000000, Ф39 + Ф40

:8 + 2Л-1-2-1 2Л-10/2Ч

Пример 2.(Рг1)-001111111110-1-

д л Ф4-011.11111111 1-2

,-ю

А Л

(1-2

Фокр 1 /Ф4 0000000001 0000000001 05ft2W, D5ftlHr10 . Фокр (f-21 2-10 1А Ф40

Ф39 4111111111

Ф40 - 2

Л А.

1 -2s

ю

;-9

л - 2

ю

Г-

-10

е р 3.(Рг1) 001111111111

f.

П. р и м

$4

4 10000000000 Фокр 1/Ф4 0000000001 0000000000, Ф5(12)гТ, Ф5(1) 0 ) - 1 - 210, Ф39 + Ф40 Ф39

А

2

-ю,

4, .. М-

Ф40

1

15

20 25 0

5

0

5

В режиме Р4 по сигналу П28 0 к шине 15 подключаются выходы коммутатора 8 (при П28 1 выходы коммутатора 8 находятся в третьем высокоимпедансном состоянии) и от этой шины отключаются выходы всех других устройств ФОП. Поэтому при П28 0 устройство выдает на шину 15 код

Ф15 Ф8 - П27 П14 П24 ОФ10,(6)

являющийся результатом операции, код П18(Т1), П19(Т1), который содержится в регистре 68 формирователя 6 и указывает, что результат (6) является при П27 1 произведением, а при П27 0 частным.

Блок 1 служит для формирования шести синхронизирующих импульсов и двух управ лЈющи)сигнаЈов

И31 И41 П17-И20.

И32 И57 И31-(П47УП47.П18-П29).

И35 И58 - И31-(П47УП47- ).

И36 И59 И31- П47УИ20-(П48аУП48б).

И37 И45 И20 П486.

И38 И46 И20-П48в.

ПЗЗ П48а,

П34 П17у(П48аУП48б7П48в) (7) в режимах Р2 и РЗ так, что в режиме Р2 вырабатывает в такте Т1 (т.е. при П47 0) по

импульсу И31, И32, ИЗб и И52. а в такте Т2 (т.е. при П47 1) по импульсу И31, Р32 при П18П29 1..И35 при П18-П29 1 и И60 И53УИ44УИ46 по И53, по окончании которого при П50 1 регистр 48 переходит в состояние 100 тактах режима РЗ; в режиме РЗ в такте П (т.е. при Ф48 100) - сигнал ПЗЗ П48а 1, импульс И36 импульс И60, в такте 12 (т.е. при Ф48 010) - по импульсу И36, И37 и И60, в такте t3 (т.е при Ф48

0 001) - импульс И38 и импульс И60, а в каждом из тактов режима РЗ (т.е. при Ф48 + 000) - сигнал П34 0.

Элементы 11 и 13 служат для формиро- вания управляющего сигнала П11 19- П17, равного 1 только в режиме Р2 при вводе опе5 рандов операции умножения (2+п)-разряд- ных кодов без знаков.

Элемент 12 служит для формирования сигнала П12 П15-П11 равного О при П11 0 и определяющего значение П12 П15

старшего разряда кода первого сомножителя операции умножения при П11 - 1.

Блок 9 служит для формирования двухразрядного кода Ф9, равного Ф9 00 при П11 0 и равного Ф9 Ф16 входному коду Ф16, определяющему два младших разряда кода второго сомножителя операции умножения кодов без знаков.

Регистр4, блок 5 и компаратор 7 используются только при выполнении операции деления, причем регистр 4 служит для запоминания (1+п)-разрядного кода Ф4 модуля делителя (см. (1)) алгоритма деления (5), компаратор 7 служит для формирования в такте Т2 режима Р2 сигналов П29 и ЛЗО сравнения кодов Ф (Т1) и Ф (Т2) в соответствии с выражениями

{О при Ф (Т2) Ф (Т1) - Ф4 1 приФ(Т2) Ф(Т1) Ф4, гОприФ(Т2) Ф(Т1)Ф4, П30 J

1 приФ(Т2)Ф(Т1) Ф4, (8) а блок 5 в тактах t1 и t2 режимах ,РЗ вырабатывает соответственно коды Ф5 (t1) Ф15 и Ф5(г2) Ф15 . определяющие код (2). обратный коду Ф4 с точностью операции усечения с округлением до 2п разрядов с весом старшего (или младшего) разряда 2 (или ), причем в режиме РЗ по сигналу П34 0 к шине 15 подключены выходы блока 5 (при П34 1 выходы блока 5 находятся в третьем состоянии)и от этой шины отключены выходы всех других устройств ФОЛ..

Формирователь 6 с помощью импульсов И31 запоминает в регистре 68 шесть сигналов и по ним формирует шесть выходных сигналов

П21 П29-(Т2), П22 Л24©П21, П23 П15(Т1), Л24 П23©П15(Т2). П25 Л24.П19(Т2), П26 - ПЗО (Т2)У П2УП19 (Т2). чП27 П18(Т2),(9)

где при П18 (Т1) 1 сигнал П24 определяет значение знакового разряда частного, при П18 (Т1) 0 и П19 (Т1) 1 сигнал П25 определяет значение знакового разряда произведения операции умножения в прямом коде, при П18 (Т1) 1 сигнал П26 является результатом сравнения модулей операндов операции деления равен Г при Ф (Т2) Ф(Т1) Ф4 или при П19 (Т1) 1 и Ф (Т2) Ф (Т1) Ф4 и равен О при Ф (Т2) Ф (Т1) Ф4, а сигнал П27 П18 (Т1) показывает, что устройство является при П27 1 умножителем, при П27 0 делителем.

Элемент 14 служит для формирования сигнала Л14 П2&/П39. определяющего при

0

5

0

5

П27 1 значение или П14 П39 старшего разряда произведения операции умножения кодов без знаков (т.е. при П19 (Т1) 0), либо значение Л14 П25 знакового разряда операции умножения в прямом коде (т.е приП19(Т1)1).

Умножитель 2 режимах Р1 и Р2 служит при П27 1 для запоминания в регистрах Рг1 и РГ2 кодов сомножителей (Рг1) Ф(Т1) и Рг2 Ф(Т2) и формирования по ним (2+п)- разрядного произведения

Ф39 ФокР(Рг1НРг2),(10)

два старших разряда которого являются значащими при П19 (Т1) 0 или имеют нулевые значения при П19 (Т1) 1, а при П27 О для запоминания в регистрах РГ3 и РГ4 п- разрядных слагаемых алгоритма (5), полученных в соответствии с выражениями Г(РГ3 - Ф39 - Фокр (Рг1) 05(11), (РГ4) Ф40 - (РГ1) Ф5(12).(11)

Сумматор 3 функционирует согласно (5). Блок 10 служит для формирования п- разрядного кода модуля частного операции деления (т.е. при П27 0) в соответствии с выражением

(12)

.ФЗУП26.(). Коммутатор 8 служит для выдачи в режиме Р4 на шину 15 результата (6) операции, код П18 (Т1) П19 (Т1), который содержится в регистре 68.

О функционировании устройства в це- RQM дает представление фиг.4, на которой показано: режим Р2 выполняется в течение двух периодов частоты следования импульсов И20 - фиг.4а,б,г,е; режим РЗ выполняется в течение трех периодов частоты следования импульсов И20. когда блок 1 вырабатывает управляющий сигнал П34 О, подключающий к шине 15 выходы п-разряд- HOFO кода Ф5 Ф15 блока 5 и отключающий от этой шины выходы остальных устройств ФОЛ - фиг.4е.ж,з.и; режим Р4 выполяется в течение одного периода частоты следования импульсов И20, когда на устройство поступает сигнал П28 О, подключающий к шине 15 выходы Ф8 Ф15 коммутатора 8 и отключающий от этой шины выходы всех других устройств ФОЛ.

Если при выполнении операции деления при П18 1иП19 Ов режиме Р2 в устройство ввести коды Ф15(Т1) Y и Ф15 (Т2) X прямоугольных координат Y и X измеряемой величины, то сигналы П21 - П24 обозначают следующи(используемые при 5 преобразовании кодов Хит прямоугольных координат в коды Аид полярных координат) логические переменные

П21 0 ГОприт I XI

L1 при YI Ј. т. П22 01©А11,

0

5

0

5

0

П23 УО А1,

П24 УО©ХО А11,(13)

где YO и ХО - разрядные цифры знаковых разрядов кодов Y и X соответственно;

А1 и А11 - разрядные цифры первого и второго старших разрядов кода А, имеющих веса 180° и 90° соответственно. Формула изобретения 1. Устройство для деления, содержащее блок управления, умножитель, сумматор, регистр и блок памяти, отличающееся тем, что, с целью расширения класса решаемых задач путем обеспечения дополнительных возможностей выполнения операции умножения кодов без знаков, операции умножения в прямом коде и операции деления в прямом коде с определением делимого и делителя, не меньшего делимого по модулю, оно содержит формирователь информационных сигналов, компаратор, коммутатор, блок элементов И, блок элементов ИЛИ, два элемента И, элемент ИЛИ-НЕ, элемент ИЛИ, причем первые четыре выхода формирователя информационных сигналов соединены с информационными выходами устройства, пятый выход формирователя информационных сигналов соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом старшего разряда старшей (2+п)-разрядной части произведения умножителя, а выход элемента ИЛИ соединен с первым информационным входом старшего разряда коммутатора, первые информационные входы младших разрядов которого соединены с выходами младших 1+п разрядов старшей части произведения умножителя, выходы младших п разрядов старшей части и выходы старших п разрядов младшей части 2-{2 + п)-разряд- ного произведения умножителя соединены с входами первого и второго слагаемых сумматора соответственно, вторые информационные входы п младших разрядов коммутатора соединены с выходами блока элементов ИЛИ, первые входы которого соединены с шестым выходом формирователя информационных сигналов, вторые входы блока элементов ИЛИ соединены с выходами сумматора, четвертый выход формирователя информационных сигналов соединен с вторым информационным входом первого старшего разряда коммутатора, второй информационный вход второго старшего разряда которого соединен с входом переноса сумматора и с входом логического нуля устройства, седьмой выход формирователя информационных сигналов соединен с управляющим входом умножителя и с первым управляющим входом коммутатора, второй управляющий вход которого является входом выбора устройства, выход элемента ИЛИ-НЕ соединен с первым входом первого элемента И, второй вход которого соединен с первым входом блока управле- 5 ния и входом управления вводом данных устройства, вход старшего разряда кода операции устройства соединен с вторым входом блока управления и первыми входами формирователя информационных сигна0 лов и элемента ИЛЙ-НЕ. вторые входы которых соединены с входом младшего разряда кода операции устройства, выход первого элемента И соединен с первыми входами блока элементов И и второго эле5 мента И, второй вход которого соединен с третьим входом формирователя информационных сигналов и входом-выходом старшего разряда шины данных устройства, входы-выходы младших 1+п разрядов кото0 рой соединены с входами младших разрядов первого информационного входа умножителя, первыми информационными входами компаратора и связаны с вторыми информационными входами компаратора

5 через регистр, выходы младших п разрядов которого соединены с адресными входами младших разрядов блока памяти, выходы коммутатора соединены с входами-выходами шины данных устройства, входы-выходы

0 п младших разрядов которой соединены с выходами блока памяти и вторыми информационными входами старших разрядов умножителя, вторые информационные входы младших разрядов которого соединены с

5 выходами блока элементов И, вторые входы которого соединены с входами двух младших разрядов кода одного из сомножителей операции умножения кодов без знаков устройства, выход второго элемента И соеди0 йен с первым информационным входом старшего разряда умножителя, тактовый вход устройства соединен с третьим входом блока управления, выход сигнала Больше компаратора соединен с четвертыми входа5, ми блока управления и формирователя информационных сигналов, пятый выход которого соединен с выходом сигнала Равно компаратора, первый и второй выходы блока управления соединены с шестым вхо0 дом формирователя информационных сигналов и синхровходом регистра соответственно, третий выход блока управления соединен с адресным входом старшего разряда блока памяти, вход выбора которого соединен с чет5 вертым выходом блока управления, являющимся управляющим выходом устройства, а пятый, шестой, седьмой и восьмой выходы блока управления соединены с первым, вторым, третьим и четвертым синхров- ходами умножителя соответственно

первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами блока являются выходы первого элемента И-НЕ, второго элемента И, первого разряда сдвигового регистра, первого элемента ИЛИ. третьего элемента И, четвертого элемента И, пятого и шестого элементов И-НЕ соответственно.

информационным.входом, четвертый, пятый и шестой входы формирователя соединены с пятым информационным, шестым информационным и синхровходом буферного регистра соответственно, первый информационный выход буферного регистра соединен с входом первого элемента НЕ, второй информационный выход буферного регистра соединен с первыми входами первого и второго элементов И, третий и четвертыи информационные входы буферного регистра соединены с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. выход которого Соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ и вторым входом второго элемента И, пятый информационный выход буферного регистра соединен с входом второго элемента НЕ, выход которого соединен с вторыми входами первого элемента И и второго

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, шестой информационный выход буферного регистра соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а первым, вторым, третьим, четвертым, пятым, шестым и седьмым выходами формирователя являются выходы второго элемента НЕ, второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый информационный выход буферного регистра, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента И, выход элемента ИЛИ и выход первого элемента НЕ соответственно.

Фиг.З

Фиг. 2

fc 5Г cJ

гс ©

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-07-07—Публикация

1990-04-17—Подача