(54) ИМИТАТОР ДИСКРЕТНОГО КАНАЛА СВЯЗИ С ОШИБКАМИ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2005 |

|

RU2286597C1 |

| Имитатор дискретного канала связи | 1978 |

|

SU807312A1 |

| Имитатор дискретного канала связи | 1986 |

|

SU1425702A1 |

| Имитатор дискретного канала связи | 1985 |

|

SU1324033A1 |

| Имитатор дискретного канала связи | 1982 |

|

SU1075267A2 |

| Имитатор дискретного канала связи | 1988 |

|

SU1562926A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

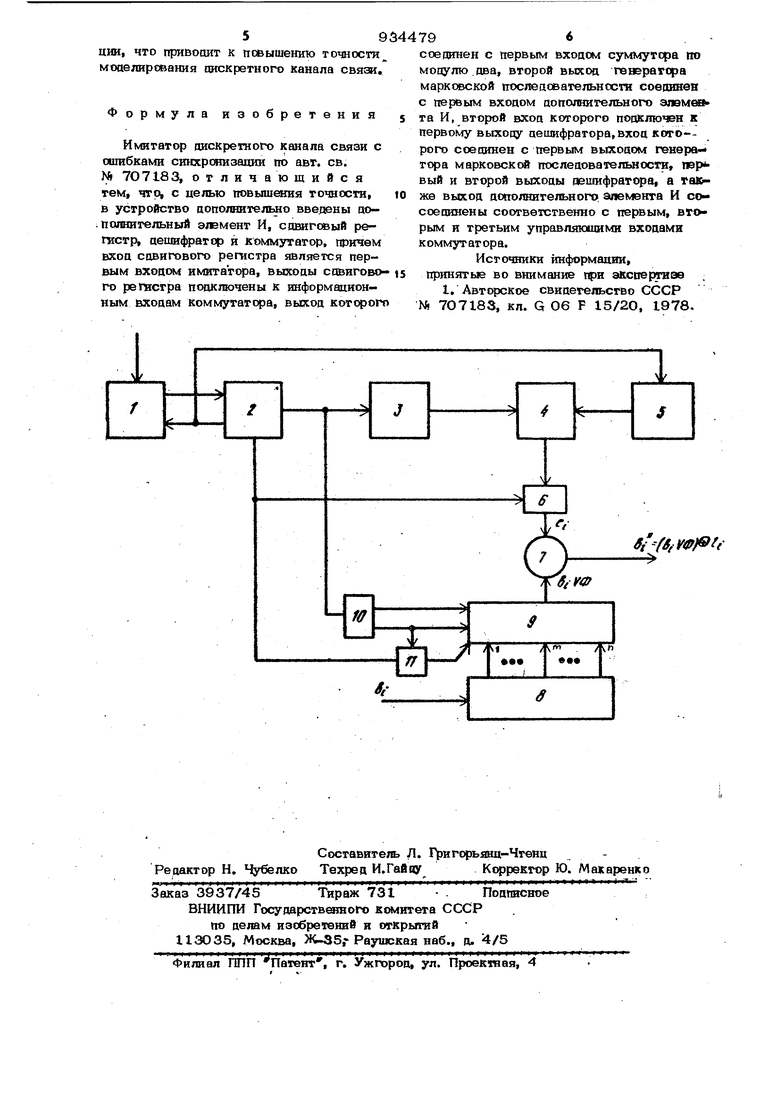

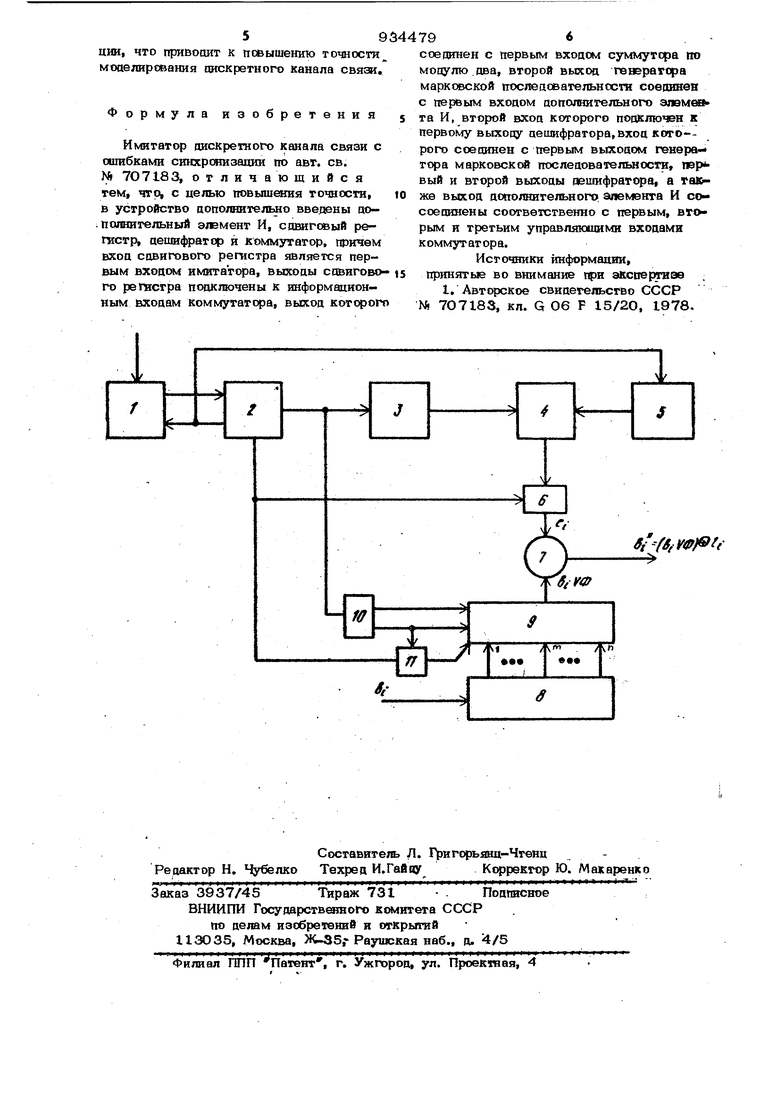

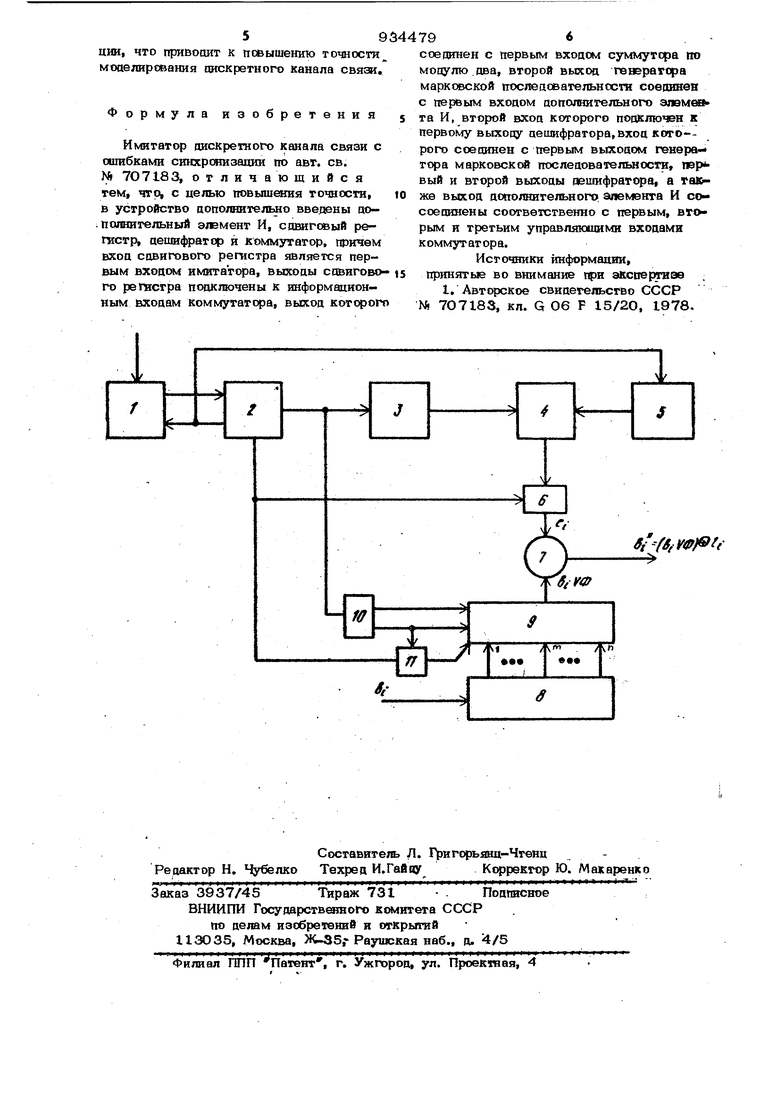

Изобретение относится к радиотетнике и может быть использовано для статистического моделирования систем передачи дискретных сообщений. По основному авт. св. N« 707183 известен имитатор дискретного канала связи с ошибками синхрснизашш, содержащий сумматор по модулю два, выход и первый вход которого явл5потся соагвез -. ственно вькодом и первым входом имитатора блок сшпронизашш, первый вход ко торого является вторым входом имитатора, а выход соединен с входом генерато ра марковской последовательности, первый выход Koii-oporo соединен с вторым входом блска сш1: ф6низеции и с входом датчика случайных чисел, блок щ)омежугочной памяти, псроговый сумматор и элемент И, выход которого соединен с вторым входом сумматора по модушо даа, а первый и второй входы элемента И подключены соответственно к выходу порогового сумматора и к второму выходу генератора марковской последовательности. третий выход которого блок промёжугочный памяти соединен с первым входом порогового сумматфа, второй вход которого подключен к выходу датчика сду айных чисел tl}. Недостатком.звестного имитатора яаляется го, что он моделирует только оиибки трансформации и не учитываем ошибки синхронизации, кЪторые проявляются в выпадении и вставках символов в информационную последовательность, что снижает достоверность моделирования дискретного канала связи. Цель изобретения - повышение точности. Поставленная цель достигается тем, что в имитатор введены дополнительный элемент И, сдвигсеый регистр, дешифратор и коммутатор, причем вход сдвигового регистра является первым взводом имитатора, выходы сдвиговогорегистра подключены к информационным входам комму татора, выход которого соединен с первым входом сумматора по кгоруто да а, второй выход генератора марковской последовательности ссеаинен с первым входом до- потвштепьного элемента И, второй вход ко торого подключен к первому выходу де шифратора, вход которого соединен с первым выходом генератора марковской посдановательности, первый и второй выходы дешифратора, а также выход дополнительного элемента И соеданены соответсг вешго с первым, вторым и третьим управ- л5Пся1шми Входами коммутатора. На чертеже представлен предлагаемый имитатор., Имитатор содержит блок I сйнхрониаации, генератор 2 марковской последшательности, блок 3 промежуточной памяти, пороговый сумматор 4, датчик 5 случайных чисел, элемент И 6, сумматор 7 по модулю два, с двигающий регистр 8, коммутатор 9 дешифратор 1О, элемент И 11. Имитатор работает следующим образом В начале работы внешний синхроимпуль запускает блок 1, которыйвырабатывает сигнал, запускающий генератор 2 марковской последовательности.На первом такте работы генератор 2 марковской последо- вательности на втором его выходе появляется сигнал, который опрашивает логический э;юмент И 6. Этим же сигналом через ключ 11, поскольку на его первый вход сигнал запрета с дешиф1ратора 10 не поступал, опрашивается реверсивный коммутатор 9, а так как в начале работы реверсивный коммутатор 9 находится в состо5шии т -jT , то фи опросе сн пропускает информацию с m разряда сдвигающего регистра 8 на вход сумматора 7 по модулю два. Поскольку на входы noptxгового сумматора 4 ничего не подавалось то на входе элемента И 6 присутствует низкий уровень, и при его опросе на вход сумматора 7 по модудю два сигнал не поступит. После окончания цикла поиска, состояние цепи Маркова на выходе генератора маркшской последовательности .по является код состояния цепи Маркова С , который заааег адрес ячейки промежуто ного блока 3 памяти, в которой храштся соответствующая условная вероятность ошибки . Кроме того, код сазто$а1ия поступает также на вход дешифратора 1О, на первом выходе которого появляется сигнал, переводящий реверсивный коммутатор из состояния т (nv-l), если код состояния цепи Маркова соответствует состоянию, в Котором происходит выпада|Ние симврла. На втором выходе дешифратора iO появляется сигнал, когда код СОСТОЯНИЯ соответствует вставке символа, и переводит реверсивный коммутатор 9 из w в (w+l), а также запрещает его опрос через Ключ 11. Если код не соответствует ни вставке, ни выпадению символа в информационной последовательности, то сигналов на выходе дешифратора Ю нет, и не изменяется состояние ре версивного коммутатора 9. При etxi опросе считывается информация с m разряда сдвигающего регистра 8, информация в котором автоматически сдвигается по приходу следующего информационного симво-; ла t) . Одновременно с кодом состояния на третьем выходе генератора 2 марковской последовательности появляется сигнал, который подготавливает блок 1 к новому циклу и опрашивает датчик 5 случайных чисел, который свырабатывает сдгчайное равнорозпределенное число. Это число подается на вход порогшого сумматора 4, на второй вход которого поступает из блока 3 памяти соответствующая условная вероятность ошибки. Сигнал на выходе порогового сумматора 4 появляется в том случае, когда сумма этих двух чисел больше единицы. С приходом следующего синхроимпульса снова запускается генератор 2 марковской последовательности, и на втором такте его работы опрашивается логический элемент И 6, а через ключ 11 - реверсивный коммутатор 9. В результате на выходе элемента И 6 появляется сигнал ошибки, а на выходе реверсивного коммутатора 9 информационный сигнал, которье поступают на входы сумматора 7 по модулю два, где происходит сложение информационного сигнала с сигналами ошибки. Если код состояния соответствует &ыгпаданшо символа, то на выходе реверсивного комкутатора 9 находится информация из (m-l) разряда, а на выходе элемента И 6 - всегда , так как в блоке 3 памяти для этого состояния записана условная вероятность, ршная О. Если код состояния соответствует вставке, то на выходе реверсивного коммутатора 9 находится О, так как его опрос запрещен сигналом с выхода дешифратс а 1О на Ключ И, гфичем состояние реверсивного коммутатора 9 увеличивается на единицу, а на выходе элемента И 6 находится сигна:л вставки либо I с вероятностью ., либо О с вероятностью (1 ..}Включение в схему дешифратора, сдвигающего регистра, ключа и реверсивного оммутатора позволяет моделировать как сшибки трансфсрмашш, так и синхрдаизации, что привооиг к повышению точности моаелирования союкретного канала связи.

Ф

ормула изобретения ;

Имитатор дискретного канала связи с ошибкамя синхрдаизации по авт. св. J 7О7183, отличающийся тем, чтр с целью повышения точностИ| в устройство аополштельно введены ао- . полнительный элемент И, совигсеый регистр, дешифратор и коммутатор, причем вхоа сдвигового регистра является пер вым входом имитатора, выходы совигового регистра подключены к информационным входам коммутатора, выход которого

соединен с первым входом суммутсра по модулю.два, второй выход гвшратора марковской послещвательностя соединен с первым входом дополнительного эпамо та И, второй вхоц которого подключен к первому выходу дешифратора, вход кото-рого соединен с первым выходом генератора марковской последовательности, пэр вый и второй выходы дешифратора, а также выход дополнительного, элемента И со соединены соответственно с первым, вторым и третьим управляющими входами коммутатора.

Источники информации, принятые во внимание при экспертиза 1. Авторское свидетельство СССР N 7О7183, кл. G 06 F 15/2О. 1978.

Авторы

Даты

1982-06-07—Публикация

1980-03-03—Подача