Изобретение относится к вычислительной и измерительной технике и может быть использовано для получения распределения случайных чисел, представленных в некоторой разрядной системе, например двоичной.

Целью изобретения является расширение функциональных возможностей устройства путем формирования производной гистограммы и вычисления интегральной функции распределения.

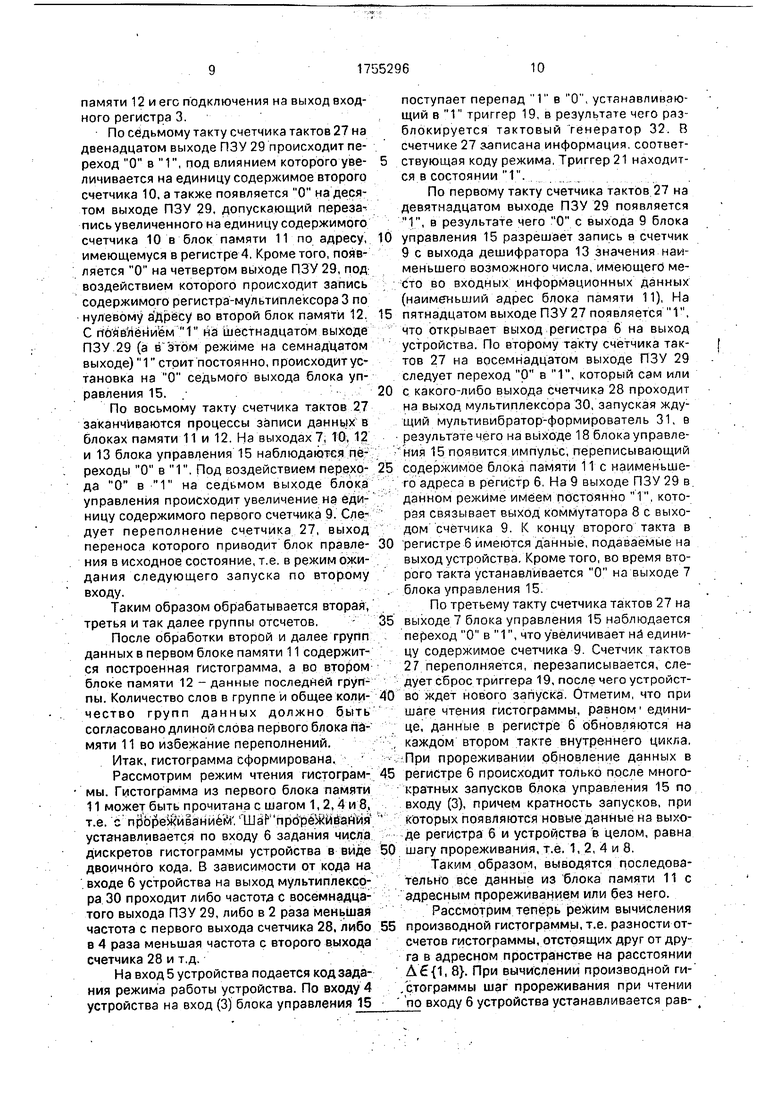

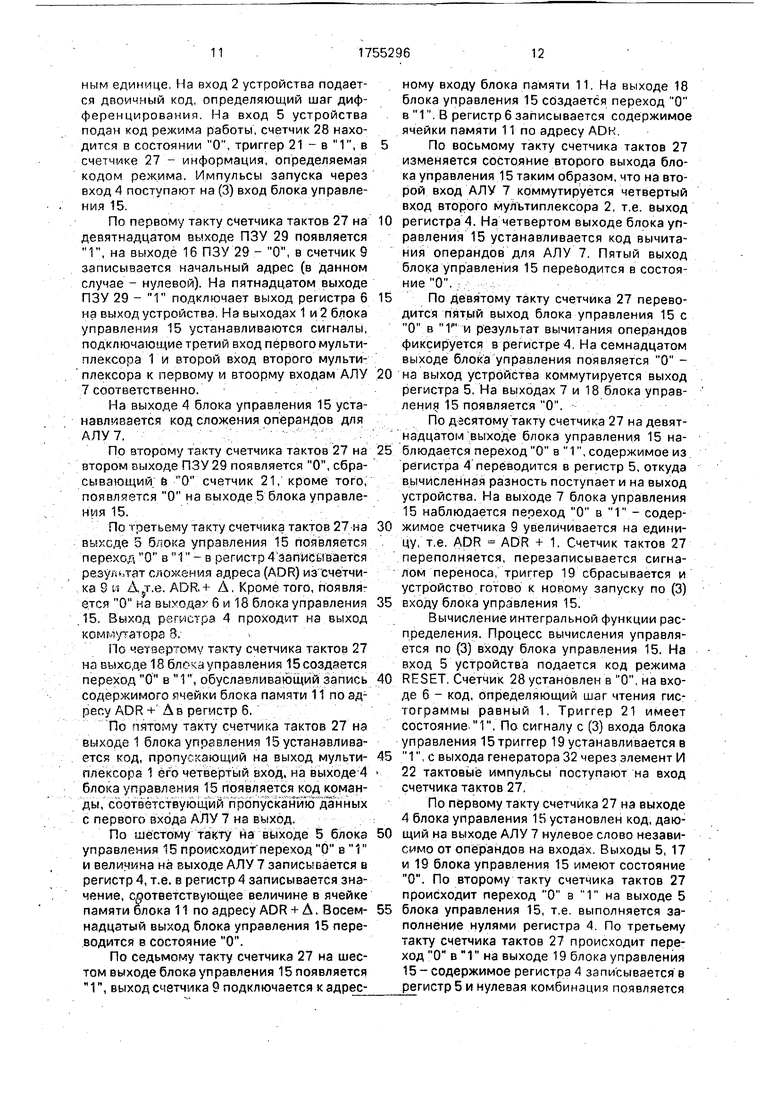

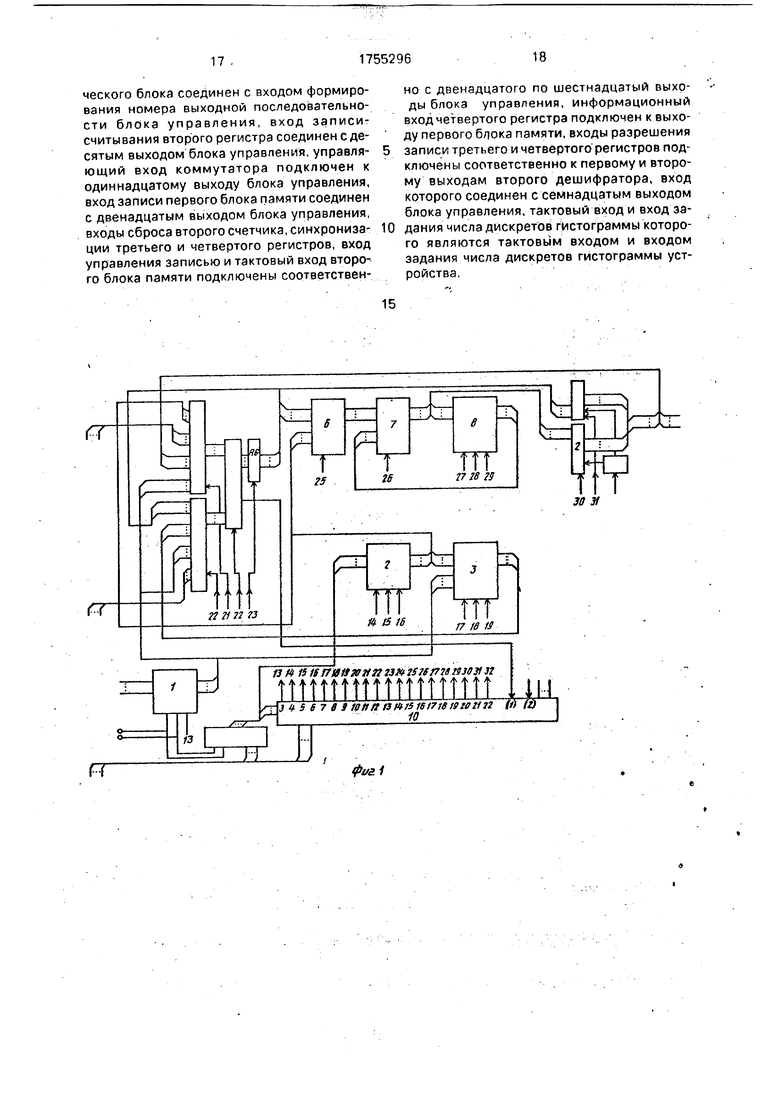

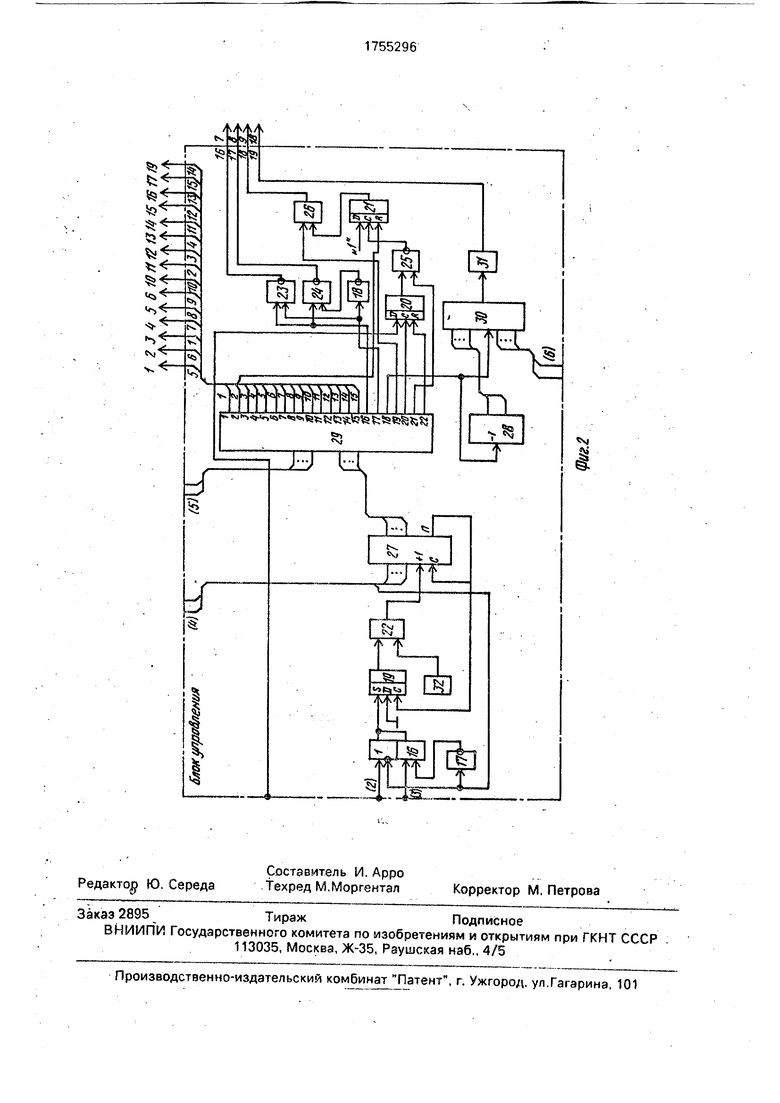

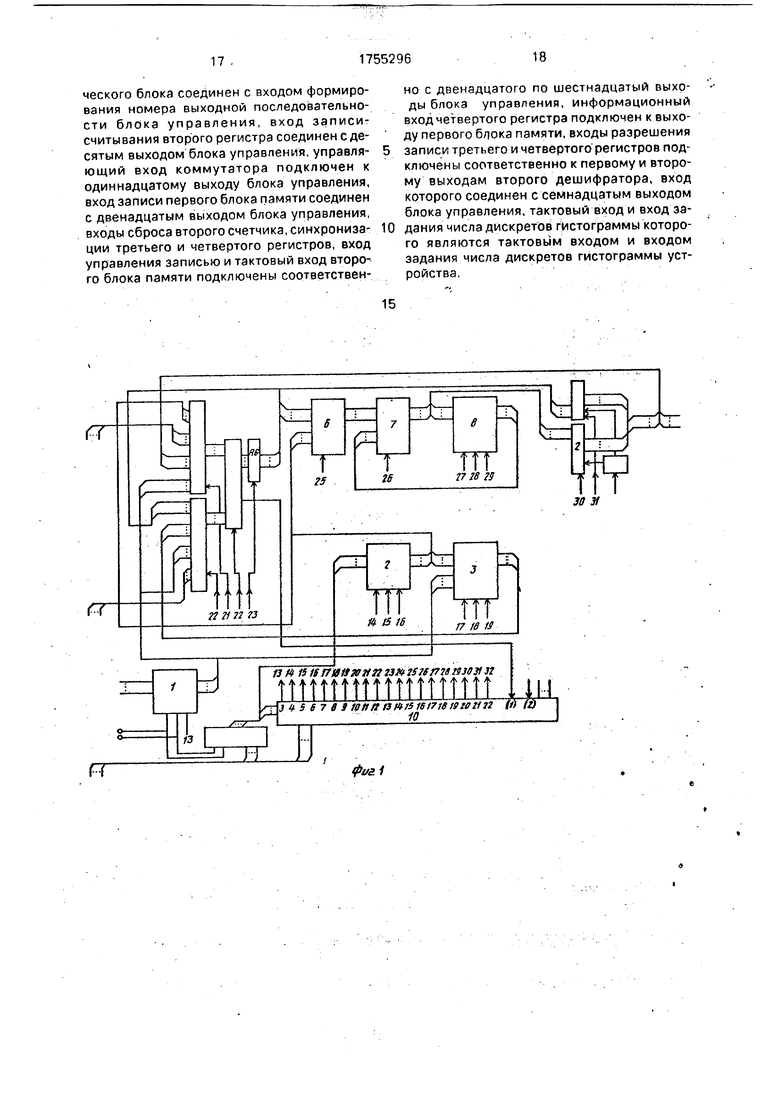

На фиг.1 изображена принципиальная схема устройства; на фиг.2 - принципиальная схема блока управления.

Устройство содержит первый 1 и второй 2 мультиплексоры, первый 3, второй 4, третий 5 и четвертый 6 регистры, арифметический блок 7, коммутатор 3, первый 9 и второй 10 счетчики, первый 11 и второй 12 блоки памяти, первый 13 и второй 14 дешифраторы и блок управления 15. Информационный вход первэго регистра 3 является информационным входом (Вход 0)устройства, а выход регистра 3 подключен к первым

информационным входам первого 1 ивторо- го 2 мультиплексоров, а также к информационному входу второго 12 блока памяти, а вход управления входной разрядностью и вход управления выходной разрядностью регистра 3 соединены соответственно с вторым и третьим входами первого дешифратора 13 и они образуют также вход управления масштабированием (Вход 3) устройства.

Второй информационный вход мультиплексора 1 подключен к входу задания вероятностей EI и Е (Вход 1) устройства, а второй информационный вход мультиплексора 2 подключен к входу задания шага дифференцирования в режиме дифференцирования (Вход 2) устройства. Третий информационный зход мультиплексора 1 соединен с первым информационным входом коммутатора 8, а выходом первого счетчика 9 - и с адресным входом второго блока памяти 12. Четвертый информационный вход мультиплексора 1 соединен с объединенными через монтажное ИЛИ (не показано) выходами регистров 5 и 6, что

te

vj СЛ

В

чэ о

одновременно является и выходом устройства. Третий информационный вход мультиплексора 2 соединен с выходом второго блока памяти 12, а четвертый информационный вход того же мультиплексора подклю- чен к выходу второго регистра 4, к второму информационному входу коммутатора 8 и к информационному входу регистра 5. Выходы мультиплексоров 1 и 2 подключены соответственено к первому и второму ин- формационным входам арифметического блока 7, выход которого подключен к информационному входу регистра 4, а выход знака подключен к входу (1) формирования номера выходной последовательности блока уп- равления 15,

Выход коммутатора 8 подключен к адресному входу первого блока памяти 11, выход которого подключен к информацион- ным входам соответственно второго счетчи- ка 10 и регистра 6. Выход счетчика 10 подключен к информационному входу блока памяти 11. Входы разрешения записи регистров 5 и 6 подключены соответственно к первому и второму выходам второго дешиф- ратора 14.

Первый вход дешифратора 13 объединен с входом (5) задания режима работы блока управления 15 и одновременно является входом задания режима работы уст- ройства (Вход 5), а выход дешифратора 13 подключен к информационному входу первого счетчика 9 и к входу (4) задания количества шагов блока управления 15.

Вход внешней синхронизации (Вход 4) устройства является одновременно и входом внешней синхронизации (2) (3) блока управления 15, а вход задания числа дискретов гистограммы (Вход 6) устройства является одновременно таким же входом (6) блока управления 15,

Первый выход блока управления 15 подключен к управляющему входу мультиплексора 1, второй - к управляющему входу мультиплексора 2, третий - к входу синхро- низации входного отсчета регистра 3, четвертый - к входу задания кода операции арифметического блока 7, пятый - к входу записи/считывания регистра 4, шестой - к управляющему входу коммутатора 8, седь- мой, восьмой и девятый - соответственно к входу управления прямым счетом, к входу управления инверсным счетом и к входу записи счетчика 9, десятый - к входу записи блока памяти 11, одиннадцатый, двенадца- тый и тринадцатый - соответственно к тактовому входу, входу записи и к входу управления записи блока памяти 12, четырнадцатый, пятнадцатый и шестнадцатый соответственно к входу сброса, к входу

управления прямым счетом и к входу записи счетчика 10, семнадцатый - к управляющему входу дешифратора 14,восемнадцатый и девятнадцатый - к входам синхронизации соответственно регистров 6 и 5

Блок управления 15 (фиг.2) содержит двухвходовый коммутатор 16, инверторы 17 и 18, триггеры 19, 20 и 21, элемент И 22, элементы И-НЕ 23, 24, 25 и 26, счетчики 27 и 28, постоянное запоминающее устройство 29, мультиплексор 30, ждущий мультивибратор 31 в качестве формирователя импульса и тактовый генератор 32.

Первый вход коммутатора 16 является первым информационным и он соединен со вторым (2) входом блока управления, второй вход коммутатора 16 является первым управляющим входом (уровень логического О на нем коммутирует на выход первый информационный вход) и он соединен с входом инвертора 17 и с входом (4) задания количества шагов, который в свою очередь соединен с информационным входом счетчика 27. Третий вход коммутатора 16 является вторым информационным входом и подключен к третьему (3) входу блока управления 15, четвертый вход этого коммутатора является вторым управляющим входом (уровень логического О на нем коммутирует на выход второй информационный вход) и он соединен с выходом инвертора 17.

Выход коммутатора 16 подключен к зхо- ду установки в 1 триггера 19, второй вход которого является информационным и соединен с общей шиной устройства, а третий вход является входом синхронизации и соединен с выходом переноса счетчика 27 и с его входом разрешения записи. Выход триггера 19 подключен к первому входу элемента И 22, к второму входу которого подключен выход тактового генератора 32, а выход элемента И 22 подключен к счетному входу счетчика 27, выход которого подключен к второму адресному входу ПЗУ 29, первый адресный вход которого соединен с входом

(5)задания режима блока управления,

Первый информационный вход мультиплексора 30 подключен к входу счетчика 28, а его второй информационный вход - к восемнадцатому выходу ПЗУ 29 и к входу обратного счета счетчика 28. Управляющий вход мультиплексора 30 соединен с входом

(6)задания числа дискретов гистограммы блока управления, а его выход - с входом запуска ждущего мультивибратора 31, выход которого соединен с восемнадцатым выходом блока управления.

Шестнадцатый выход ПЗУ 29 подклю- чен к первым входам элементов И-НЕ 23 и 24, а семнадцатый выход - к второму входу

элемента И-НЕ 23 и через инвертор 18 ла второй вход элемента И-НЕ 24. Выходы элементов И-НЕ 23 и 24 соединены соответственно с выходами 7 и 8 блока управления.

Девятнадцатый выход ПЗУ 29 подключен к первому входу элемента И-НЕ 26, второй вход которого соединен с. выходом триггера 21, а выход соединен с девятым выходом блока управления.

Двадцатый выход ПЗУ 29 подключен к синхронизирующему входу триггера 20, информационный вход которого соединен с входом (1) формирования номера выходной последовательности, а вход сброса в О подключен к двадцать второму выходу ПЗУ 29. Выход триггера 20 подключен к первому входу элемента И-НЕ 25, второй вход которого соединен с двадцать первым выходом ПЗУ 29, а выход - с синхронизирующим входом триггера 21.

Вход сброса в О триггера 21 подключен к второму выходу ПЗУ 29, а на его информационном входе постоянно установлен уровень логической 1.

Выходы ПЗУ 29 с первого по пятнадцатый соединены соответственно с выходами 3, 11, 12, 13. 1, 2, 4, 5, 6, 10, 14, 15, 16, 19 и 17 блока управления.

Устройство имеет два основных режима работы: формирование гистограммы, обработка гистограммы.

Режим обработки гистограммы включает в себя следующие виды: 2.1 чтение гистограммы; 2.2 вычисление производной гистограммы; 2.3 вычисление интегральной функции распределения; 2,4 вычисление порога по заданной вероятности ложных тревог Рлт.

Первым режимом работы устройства всегда является формирования гистограммы. Входные данные представляются в виде последовательности одинаковых по объему (количеству слов) групп. Количество слов в группе определяет адресное пространство второго блока памяти 12. Гистограмма формируется поэтапно в первом блоке памяти 11. На первом этапе формирования гистограммы осуществляется обнуление первого блока памяти 11 и запись первой группы данных во второй блок памяти 12. На последующих этапах происходит чтение данных предыдущей группы из второго блока памяти 12 и запись на освободившиеся адреса данных текущей группы, В то же время с выхода второго блока памяти 12 и входного (первого) регистра 1 данные предыдущей и текущей групп через первый и второй мультиплексоры 1 и 2 синхронно поступают на информационные входы

арифметико-логического устройства 7. Во втором регистре 4 фиксируется результат операции арифметико-логического устройства 7. Гистограмма строится в первом блоке памяти 11 по выходным данным второго регистра 4. Конкретный вид данных во втором регистре 4 определяется кодом операции на управляющем входе 4 арифметико-логического устройства 7. Таким обра0 зом можно построить гистограммы по данным, определенным как результат функционального преобразования арифметико- логического устройства над данными предыдущей и текущей групп. Если код опе5 рации арифметико-логического устройства соответствует вычитанию, то в устройстве реализуется режим черезпериодной компенсации и, например, при использовании данного устройства в системах измерения

0 дальности неподвижных объектов во втором регистре 4 формируются данные, соответствующие сопутствующим полезному сигналу помехам, и образующаяся в первом блоке памяти 11 гистограмма позволяет оп5 «ределить порог обнаружения соответствующей заданной вероятности ложных тревог F и помеховой ситуации во временном интервале обработки.

Остановимся теперь более подробно на

0 двух принципиально разных этапах формирования гистограммы,

Начальный этап, На входе 5 устанавливается код режима (каждый режим имеет свое обозначение в виде двоичного числа).

5 В первый счетчик 27 блока управления записывается предварительная информация, соответствующая режиму. Второй счётчик 28 сбрасывается в О, Триггер 21 устанавливается в 1, триггеры 19 и 20 - в О. На

0 вход 3 подается сигнал управления масштабированием, Устройство готово к работе.

Источник данных генерирует на информационном входе (Вход 0) двоичные слова, сопровождая их сигналом (короткий им5 пульс) готовности, которые используют через вход 4 на тактовый вход (2) блока управления 15. Исходя из кода режима на первом управляющем входе коммутатора 16 блока управления 15 стоит О, что соответ0 ствует пропусканию на первый вход триггера 19 сигнала с второго входа блока управления 15. Этот сигнал устанавливает в 1 триггер 19. 1 на выходе триггера 19 открывает элемент И 22 и тактовая частота

5 с выхода генератора .32 поступает на счетный вход счетчика тактов 27. По первому такту счетчика тактов 27 на 19 выходе ПЗУ 29 появляется 1, которая проходит через he- мент И-НЕ 26 на выход 9 блока управления 15 и записывает в первый счетчик 9 начальный адрес (в данном режиме - нулевой). Кроме того, на первый выход ПЗУ 29 следует положительный фронт (переход от О в 1), записывающий в регистр-мультиплексор 3 входные данные, В зависимо- сти от информации на входе 3 устройства данные проходят на выход регистра-мультиплексора 3 со сдвигом на 0, 1, 2 или 3 разряда. Так выполняется масштабирование и согласование адресного пространства пер- вого блока памяти 11 с разрядностью входных данных.

По второму такту счетчика тактов 27 на втором выходе ПЗУ 29 появляется О, который сбрасывает в О триггер 21, чем блоки- рует элемент И-НЕ 26.

По третьему такту счетчика тактов 27 на третьем выходе ПЗУ 29 появляется О, открывая тем самым информационный вход второго блока памяти 12, Кроме того, на шестнадцатом выходе ПЗУ 29 появляется 1, а так как в данном режиме на семнадцатом выходе ПЗУ 29 стоит 1 постоянно, то на выходе 7 блока управления 15 появля- ется О. Также появляется О на четвертом выходе ПЗУ 29, который перепишет содержимое регистра-мультиплексора 3 в блок памяти 12 в нулевую ячейку. Под воздействием О на десятом выходе ПЗУ 29 проис- ходит перезапись содержимого второго счетчика 10 в нулевую ячейку первого блока памяти 11, а поскольку на выходе 14 блока управления 15 стоит 1, счетчик 10 блокирован, т.е. на протяжении всего цикла его содержимое равно О.

По четвертому такту счетчика тактов 27 процессы записи в блоки памяти 11 и 3 заканчиваются, на выходах 7 и 13 блока управления 15 появляются положительные фронты, увеличивая на 1 содержимое, первого счетчика 9. Следует переполнение счетчика 27, выход переноса которого управляет перезаписью счетчика 27 и сбрасывает в О триггер 19, чем блокируется элемент И 22 и устройство ждет нового запуска по второму входу блока управления 15.

Аналогично проходят все последующие циклы в пределах первой группы исходных данных. По завершении приема первой группы блок памяти 11 заполнен нулями, а второй блок памяти 12 - данными первой группы.

Далее на вход 5 подается новый код режима, под воздействием которого происходит формирование гистограммы для всех последующих групп исходных данных.

На информационный вход 0 устройства подано первое слово второй группы с сопровождающим импульсом по второму вход блока управления 15.

Триггеры 19 и 21 снова устанавливаются в 1. Тактовые импульсы с выхода тактового генератора 32 поступают на счетный вход счетчика 27.

По первому такту счетчика тактов 27 на девятнадцатом выходе ПЗУ 29 появляется Г, на выходе 9 блока управления 15 появляется О, в первый счетчик 9 записывается значение начального адреса, в данном случае - нулевого. На входе 3 устройства стоит сигнал управления масштабированием. На первом выходе ПЗУ 29 возникает переход О в 1, под воздействием которого входное информационное слово записывается в первый регистр 3.

По второму такту счетчика тактов 27 на втором выходе ПЗУ 29 появляется О, что сбрасывает в О триггер 21.

По третьему такту счетчика тактов 27 на втором выходе ПЗУ 29 появляется переход О в 1 по которому осуществляется перезапись нулевой ячейки памяти в выходной регистр блока памяти, 12. Кроме того появляется О на восьмом выходе ПЗУ 29.

По четвертому такту счетчика тактов 27 на восьмом выходе ПЗУ 29 происходит переход О в 1, переписывающий результат операции АЛУ 7 во второй регистр 4. На 4 входе АЛ У 7 стоит, например, код вычитания операндов, а на управляющие входы мультиплексоров 1 и 2 поданы сигналы управления 1 и 2 соответственно такие, что первый мультиплексор пропускает сигнал по первому, а второй по третьему информационному входу. При этом первый информационный вход первого мультиплексора 1 связан с выходом входного регистра 3, а третий информационный вход второго мультиплексора связан с выходом (выходного регистра) второго блока памяти 12,

По пятому такту счетчика тактов 27 на тринадцатом выходе ПЗУ 29 появляется О, под воздействием которого происходит перезапись содержимого ячейки первого блока памяти 11 по адресу, равному числу, записанному во втором регистре 4, во второй счетчик 10. На коммутатор 6 подан управляющий сигнал, равный нулю, обеспечивая тем самым пропуск данных второго информационного входа, связанного выходом регистра 4.

По шестому такту счетчика тактов 27 на тринадцатом выходе ПЗУ 29 появляется переход О в 1, что означает окончание записи в счетчике 10, на двенадцатом выходе ПЗУ 29 появляется О. О появляется и на третьем выходе ПЗУ 29, что означает открытие информационнеого входа второго блока

памяти 12 и ere подключения на выход входного регистра 3.

По седьмому такту счетчика тактов 27 на двенадцатом выходе ПЗУ 29 происходит переход О в 1, под влиянием которого увеличивается на единицу содержимое второго счетчика 10, а также появляется О на десятом выходе ПЗУ 29, допускающий перезапись увеличенного на единицу содержимого счетчика 10 в блок памяти 11 по адресу, имеющемуся в регистре 4. Кроме того, появляется О на четвертом выходе ПЗУ 29, под воздействием которого происходит запись содержимого регистра-мультиплексора 3 по нулевому адресу во второй блок памяти 12 С появлением 1 на шестнадцатом выходе ПЗУ 29 (а в этом режиме на семнадцатом выходе) 1 стоит постоянно, происходит установка на О седьмого выхода блока управления 15.

По восьмому такту счетчика тактов 27 заканчиваются процессы записи данных в блоках памяти 11 и 12. На выходах, ТО, 12 и 13 блока управления 15 наблюдаются переходы О в 1. Под воздействием перехода О в 1 на седьмом выходе блока управления происходит увеличение на единицу содержимого первого счетчика 9. Следует переполнение счетчика 27, выход переноса которого приводит блок правления в исходное состояние, т.е. в режим ожидания следующего запуска по второму входу.

Таким образом обрабатывается вторая, третья и так далее группы отсчетов,

После обработки второй и далее групп данных в первом блоке памяти 11 содержится построенная гистограмма, а во втором блоке памяти 12 - данные последней группы. Количество слов в группе и общее количество групп данных должно быть согласовано длиной слова первого блока памяти 11 во избежание переполнений.

Итак, гистограмма сформирована.

Рассмотрим режим чтения гистограммы. Гистограмма из первого блока памяти 11 может быть прочитана с шагом 1, 2,4 и 8, т.е. с прореживанием LLJaf1 прореживания устанавливается по входу б задания числа дискретов гистограммы устройства в виде двоичного кода. В зависимости от кода на входе 6 устройства на выход мультиплексора 30 проходит либо частота с восемнадцатого выхода ПЗУ 29, либо в 2 раза меньшая частота с первого выхода счетчика 28, либо в 4 раза меньшая частота с второго выхода счетчика 28 и т.д.

На вход 5 устройства подается код задания режима работы устройства. По входу 4 устройства на вход (3) блока управления 15

поступает перепад Ч в О, устанавливающий в 1 триггер 19, в результате чего разблокируется тактовый генератор 32 В счетчике 27 записана информация соответ- ствующая коду режима Триггер 21 находится в состоянии 1.

По первому такту счетчика тактов 27 на девятнадцатом выходе ПЗУ 29 появляется 1, в результате чего О с выхода 9 блока

0 управления 15 разрешает запись а счетчик 9 с выхода дешифратора 13 значения наименьшего возможного числа, имеющего место во входных информационных данных (наименьший адрес блока памяти 11), На

5 пятнадцатом выходе ПЗУ 27 появляется 1, что открывает выход регистра 6 на выход устройства. По второму такту счетчика тактов 27 на восемнадцатом выходе ПЗУ 29 следует переход О в 1, который сам или

0 с какого-либо выхода счетчика 28 проходит на выход мультиплексора 30, запуская ждущий мультивибратор-формирователь 31, в результате чего на выходе 18 блока управле- ния 15 появится импульс, переписывающий

5 содержимое блока памяти 11 с наименьшего адреса в регистр 6 На 9 выходе ПЗУ 29 в данном режиме имеем постоянно 1, которая связывает выход коммутатора 8 с выходом счетчика 9. К концу второго такта в

0 регистре б имеются данные, подаваемые ча выход устройства. Кроме того, во время второго такта устанавливается О на выходе 7 . блока управления 15

По третьему такту счетчика тактов 27 на

5 выходе 7 блока управления 15 наблюдается переход О в 1, что увеличивает ни единицу содержимое счетчика 9 Счетчик тактов 27 переполняется, перезаписывается, следует сброс триггера 19, после чего устройст0 во ждет нового запуска Отметим, что при шаге чтения гистограммы, равном единице, данные в регистре 6 обновляются на каждом втором такге внутреннего цикла, При прореживании обновление данных в

5 регистре 6 происходит только после многократных запусков блока управления 15 по входу (3), причем кратность запусков, при которых появляются новые данные на выходе регистра 6 и устройства в целом, равна

0 шагу прореживания, т.е. 1, 2, 4 и 8.

Таким образом, выводятся последовательно все данные из блока памяти 11с адресным прореживанием или без него. Рассмотрим теперь режим вычисления

5 производной гистограммы, т.е. разности отсчетов гистограммы, отстоящих друг от друга в адресном пространстве на расстоянии АЈ{1, 8}. При вычислении производной ги- /стограммы шаг прореживания при чтении по входу 6 устройства устанавливается равным единице. На вход 2 устройства подается двоичный код, определяющий шаг дифференцирования. На вход 5 устройства подан код режима работы, счетчик 28 находится в состоянии О, триггер 21 - в 1, в счетчике 27 - информация, определяемая кодом режима. Импульсы запуска через вход 4 поступают на (3) вход блока управления 15.

По первому такту счетчика тактов 27 на девятнадцатом выходе ПЗУ 29 появляется 1, на выходе 16 ПЗУ 29 - О, в счетчик 9 записывается начальный адрес (в данном случае - нулевой). На пятнадцатом выходе ПЗУ 29 - 1 подключает выход регистра 6 на выход устройства. На выходах 1 и 2 блока управления 15 устанавливаются сигналы, подключаюидие третий вход первого мультиплексора 1 и второй вход второго мульти- плексора к первому и втоорму входам АЛУ 7 соответственно.

На выходе 4 блока управления 15 устанавливается код сложения операндов для АЛУ 7.

По второму такту счетчика тактов 27 на втором выходе ПЗУ 29 появляется О, сбрасывающий в О счетчик 21, кроме того, появляется О на выходе 5 блока управления 15.

По третьему такту счетчика тактов 27 на выходе 5 блока управления 15 появляется переход О в 1 - в регистр 4 записывается результат сложения адреса (ADR) из счетчика 9 и AjT.e. ADR.+ А. Кроме того, появляется О на выходах б и 18 блока управления 15. Выход регистра 4 проходит на выход комглутаюра В.

По четвертому такту счетчика тактов 27 на выходе 18 блока управления 15 создается переход О в 1, обуславливающий запись содержимого ячейки блока памяти 11 по адресу ADR + Д в регистр б.

По пятому такту счетчика тактов 27 на выходе 1 блока управления 15 устанавливается код, пропускающий на выход мультиплексора 1 его четвертый вход, на выходе 4 блока управления 15 появляется код команды, соответствующий пропусканию данных с первого входа АЛУ 7 на выход.

По шестому такту на выходе 5 блока управления 15 происходит переход О в 1 и величина на выходе АЛУ 7 записывается в регистр 4, т.е. в регистр 4 записывается значение, соответствующее величине в ячейке памяти блока 11 по адресу ADR + Л. Восемнадцатый выход блока управления 15 переводится в состояние О.

По седьмому такту счетчика 27 на шестом выходе блока управления 15 появляется 1, выход счетчика 9 подключается к адресному входу блока памяти 11. На выходе 18 блока управления 15 создается переход О в 1. В регистр 6 записывается содержимое ячейки памяти 11 по адресу ADH.

По восьмому такту счетчика тактов 27

изменяется состояние второго выхода блока управления 15 таким образом, что на второй вход АЛУ 7 коммутируется четвертый вход второго мультиплексора 2, т.е. выход

0 регистра 4. На четвертом выходе блока управления 15 устанавливается код вычитания операндов для АЛУ 7. Пятый выход блока управления 15 переводится в состояние О.

5 По девятому такту счетчика 27 переводится пятый выход блока управления 15 с О в и результат вычитания операндов фиксируется в регистре 4. На семнадцатом выходе блока управления появляется О 0 на выход устройства коммутируется выход регистра 5. На выходах 7 и 18 блока управления 15 появляется О.

По десятому такту счетчика 27 на девятнадцатом выходе блока управления 15 на5 блюдается переход О в 1, содержимое из регистра 4 переводится в регистр 5, откуда вычисленная разность поступает и на выход устройства. На выходе 7 блока управления 15 наблюдается переход О в 1 - содер0 жимое счетчика 9 увеличивается на единицу, т.е. ADR - ADR + 1. Счетчик тактов 27 переполняется, перезаписывается сигналом переноса, триггер 19 сбрасывается и устройство готово к новому запуску по (3)

5 входу блока управления 15.

Вычисление интегральной функции распределения. Процесс вычисления управляется по (3) входу блока управления 15. На вход 5 устройства подается код режима

0 RESET. Счетчик 28 установлен в О, на входе 6 - код, определяющий шаг чтения гистограммы равный 1. Триггер 21 имеет состояние 1. По сигналу с (3) входа блока управления 15триггер устанавливается в

5 1, с выхода генератора 32 через элемент И 22 тактовые импульсы поступают на вход счетчика тактов 27.

По первому такту счетчика 27 на выходе 4 блока управления 1й установлен код, даю0 щий на выходе АЛУ 7 нулевое слово независимо от операндов на входах. Выходы 5, 17 и 19 блока управления 15 имеют состояние О. По второму такту счетчика тактов 27 происходит переход О в 1 на выходе 5

5 блока управления 15, т.е. выполняется заполнение нулями регистра 4. По третьему такту счетчика тактов 27 происходит переход 0й в 1 на выходе 19 блока управления 15 - содержимое регистра 4 записывается в регистр 5 и нулевая комбинация появляется

на выходе устройства. Четвертый такт сбрасывает счетчик 27, триггер 19 переходит в состояние О и устройство готово к работе,

На вход 5 устройства загружается код режима вычисления интегральной функции распределения.

По сигналу (3) на входе блока управления 15 на вход счетчика тактов 27 поступают от генератора 32 тактовые импульсы. По первому такту счетчика тактов 27 на 19 выходе ПЗУ 29 установится 1, в результате чего О с выхода 9 блока управления 15 запишет начальный адрес в счетчик 9 (в данном случае наименьший адрес гистог- раммы). На 17 и 18 выходах блока управления 15 устанавливаются 1 и О соответственно. На 6 выходе блока управления стоит 1, соединяющая выход счетчика 9 через коммутатор 8 с адресным входом блока па- имяти 11.

По второму такту счетчика тактов 27 происходит переход О в 1 на 18 выходе блока управления 15, т.е. в регистр б записывается содержимое ячейки памяти блока 11 по адресу, имеющемуся в счетчике 9. Выход регистра 6 открыт на выход устройства. На выходе 1 блока управления 15 устанавливается код, соединяющий четвертый вход мультиплексора 1 с первым входом АЛУ 7, На 4 выходе блока управления 15 устанавливается код, определяющий пропуск операнда на первом входе АЛУ 7 на выход. Выход 5 блока управления 15 приводится в состояние О. На выход 2 блока управления 15 подается код, соединяющий четвертый вход второго мультиплексора 2 с вторым информационным входом АЛУ 7,

По третьему такту счетчика тактов 27 происходит переход О в 1 на 5 выходе блока управления 15, т.е. в регистр 4 записывается содержимое регистра 6. По четвертому такту счетчика тактов 27 устанавливается О на 17 выходе блока управления 15 - на выход устройства и на 4 вход мультиплексора 1 поступает содержимое регистра 5 (в данном случае нули). На 4 выход блока управления 15 подается код сложения операндов для АЛУ 7. Девятнадцатый и пятый выходы блока управления 15 приводятся в состояние О.

По пятому такту счетчика тактов 27 наблюдается переход О в 1 на 5 выходе блока управления 15, т.е. в регистр 4 записывается сумма операндов, взятых из ре- гистров 4 (имеет содержимое регистра 6) и 5.

По шестому такту счетчика тактов 27 происходит переход О в 1 на 19 выходе блока управления 15, т.е. содержимое регистра 4 фиксируется в регистре 5 и поступает на выход устройства. На выходе 7 блока управления 15 наблюдается переход О в 1, содержимое счетчика 9 увеличивается на единицу. Счетчик тактов 27 переполняется, перезаписывается сигналом переноса, триггер 19 сбрасывается и устройство готово к новому запуску по (3) входу блока управления 15.

По мере поступления сигналов запуска на выходе устройства наблюдается результат последовательного накопления суммы операндов, поступающих из блока памяти 11, что. и соответствует интегральному распределению.

При определении порога по заданной вероятности ложных тревог на вход 1 устройства подается величина F 1 - Рлт.

Аналогично предыдущему режиму сначала реализуется режим RESET.

После этого на вход 5 устройства подается код режима вычисления порога. Под действием этого режима пять первых внутренних тактов, выполняемых под управлением счетчика тактов 27, полностью совпадают с предыдущим. Поэтому продолжаем описание процедур, начиная с шестого такта счетчика 27.

По шестому такту счетчика тактов 27 на первом выходе блока управления устанавливается код, коммутирующий на выход мультиплексора 1 его второй вход. На выход 4 блока управления 15 подается команда вычитания операндов. Выход 5 блока управления 15 приводится в состояние О, Переход О в 1 на 19 выходе блока управления 15 обеспечивает перенос содержимого из регистра 4 в регистр 5.

По седьмому такту счетчика тактов 27 может выполняться условный переход. Если результат разности F - Р (Р - содержимое регистра 5, т.е. равняется текущему значению интегральной функции распределения) больше нуля, то на (1) входе блока управления 15 имеется О, и на выходе 9 блока управления 15 также имеется О. На выходе 7 блока управления 15 наблюдается переход О в 1 и содержимое счетчика 9 увеличивается на единицу.

Если результат F - Р 0 (т.е. Р становится больше F) на (1) входе блока управления 15 устанавливается 1, что переводит выход 9 блока управления 15 в 1 до снятия данного режима с входа 5 устройства. Это означает, что при появлении 1 на (1) входе блока управления 15 в данном режиме блокируется запись в счетчик 9 и в нем фиксируется адрес того момента, когда F - Р стал отрицательным, что и соответствует искомому порогу.

Счетчик тактов переполняется, перезаписывается сигналом переноса, триггер 19 сбрасывается и устройство готово к новому запуску по (3) входу блока управления 15

Проводя анализ выходных данных, мо- мент превышения Р заданного F определяют после трех дополнительных запусков, можно однако выполнить запуски в полном объеме адресного пространства блока памяти 11 После этого следует подать на вход 5 устройства режим чтения порога. Запуск осуществляется по (3) входу блока управления 15, По сигналу с (3) входа блока управления 15 триггер 19 установится в 1, с выхода генератора 32 через элемент И 22 тактовые импульсы поступают на вход счетчика 27.

По первому такту счетчика тактов 27 на 1 вход блока управления 15 устанавливается код, подключающий на первый вход АЛУ 7 третий вход мультиплексора 1, На выходе 4 блока управления устанавливается код, пропускающий операнд с первого входа АЛУ 7 на выход. Выходы 5, 17 и 19 блока управления 15 принимают состояние О. На 9 выходе блока управления 15 имеется 1.

По второму такту счетчика тактов 27 наблюдается переход О в 1 на пятом выходе блока управления, т.е. в регистр 4 заносится содержание счетчика 9 (найденный порог).

По третьему такту счетчика 27 происходит переход О в 1 на 19 выходе блока управления 15, т.е. значения) порога из ре- гистра 4 перепишутся в регистр 5, выход которого в данной ситуации является выходом устройства.

По четвертому такту счетчика тактов 27 он переполняется, перезаписывается сиг- налом переноса, триггер 19 сбрасывается и устройство готовд к новому запуску по (3) входу блока управления 15.

Отметим, что режимы обработки гистограммы не разрушают ее в блоке памяти 11 и могут быть использованы разными входными параметрами многократно.

Формула изобретения Устройство для формирования и обра- ботки гистограмм, содержащее коммутатор, первый блок памяти, два счетчика и блок управления, выход первого счетчика соединен с первым информационным входом коммутатора, выход которого подключен к адресному входу первого блока памяти, информационный вход которого соединен с выходом второго счетчика, выход первого блока памяти подключен к информационному входу второго счетчика, входы записи и

управления прямым счетом первого и второго счетчиков подключены соответственно к первому, второму, третьему и четвертому выходам блока управления, о т- личающееся тем, что, с целью расширения функциональных возможностей путем формирования производной гистограммы и вычисления интегральной функции распределения, в него введены второй блок памяти, два дешифратора, два мультиплексора, арифметический блок и четыре регистра, информационный вход первого регистра является информационным входом устройства, выход первого регистра подключен к первым информационным входам первого и второго мультиплексоров и к информационному входу второго блока памяти, вход записи которого соединен с пятым выходом блока управления, вход первого дешифратора объединен с входом задания режима работы блока управления и является входом задания режима работы устройства, выход первого дешифратора подключен к входу задания количества шагов блока управления и к информационному входу первого счетчика, выход которого соединен с адресным входом второго блока памяти, вход управления инверсным счетом первого счетчика соединен с шестым выходом блока управления, вторые информационные входы первого и второго мультиплексоров являются соответственно входами задания значений вероятностей и шага дифференцирования в режиме дифференцирования устройства, выход второго блока памяти подключен к третьему информационному входу второго мультиплексора, третий информационный вход первого мультиплексора соединен с выходом первого счетчика, четвертый информационный вход первого мультиплексора соединен с объединенными через монтажное ИЛИ выходами третьего и четвертого регистров, являющимися выходом устройства, четвертый информационный вход второго мультиплексора подключен к выходу второго регистра, соединенному с вторым информационным входом коммутатора и с информационным входом третьего регистра, управляющие входы первого и второго мультиплексоров соединены соответственно с седьмым и восьмым выходами блока управления выходы мультиплексоров подключены соответственно к первому и второму информационным входам арифметического блока, вход задания кода операции которого соединен с девятым выходом блока управления, выход арифметического блока подключен к информационному входу второго регистра а выход знака арифметического блока соединен с входом формирования номера выходной последовательности блока управления, вход записи- считывания второго регистра соединен с десятым выходом блока управления, управляющий вход коммутатора подключен к одиннадцатому выходу блока управления, вход записи первого блока памяти соединен с двенадцатым выходом блока управления, входы сброса второго счетчика, синхронизации третьего и четвертого регистров, вход управления записью и тактовый вход второго блока памяти подключены соответствен0

но с двенадцатого по шестнадцатый выходы блока управления, информационный вход четвертого регистра подключен к выходу первого блока памяти, входы разрешения записи третьего и четвертого регистров подключены соответственно к первому и второму выходам второго дешифратора, вход которого соединен с семнадцатым выходом блока управления, тактовый вход и вход задания числа дискретов гистограммы которого являются тактовым входом и входом задания числа дискретов гистограммы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство управления | 1983 |

|

SU1166108A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Измеритель линейных перемещений | 1986 |

|

SU1401273A1 |

| Логический анализатор | 1981 |

|

SU1032457A1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано для получения распределения случайных чисел, представленных в некоторой разрядной системе, а так:ке для математической обработки полученного распределения. Це/ью изобретения является расширение функциональных возможностей устройства за счет обеспечения формирования производной гистограммы и вычисления интегральной функции распределения. Устройство содержит мультиплексоры, регистры, счетчики, арифметический блок, блок памяти, блок управления, коммутатор и дешифраторы. 2 ил.

1зяим1тю11янп1э г5мгп8гззоз1п

mmtmtmmm UN

-тр 4 s s 7 e з юна iswrstetrteazt гаг //ГТгГ

10

ст

У-К

bd

;

ттт

17 J8 29

flY

30 3f

фиг 1

м &

| Статистический анализатор отклонений напряжения сети | 1985 |

|

SU1262524A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1989-04-18—Подача