75

СП ОИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении контролируемых систем.|

Целью изобретения является расширение области применения устройства,

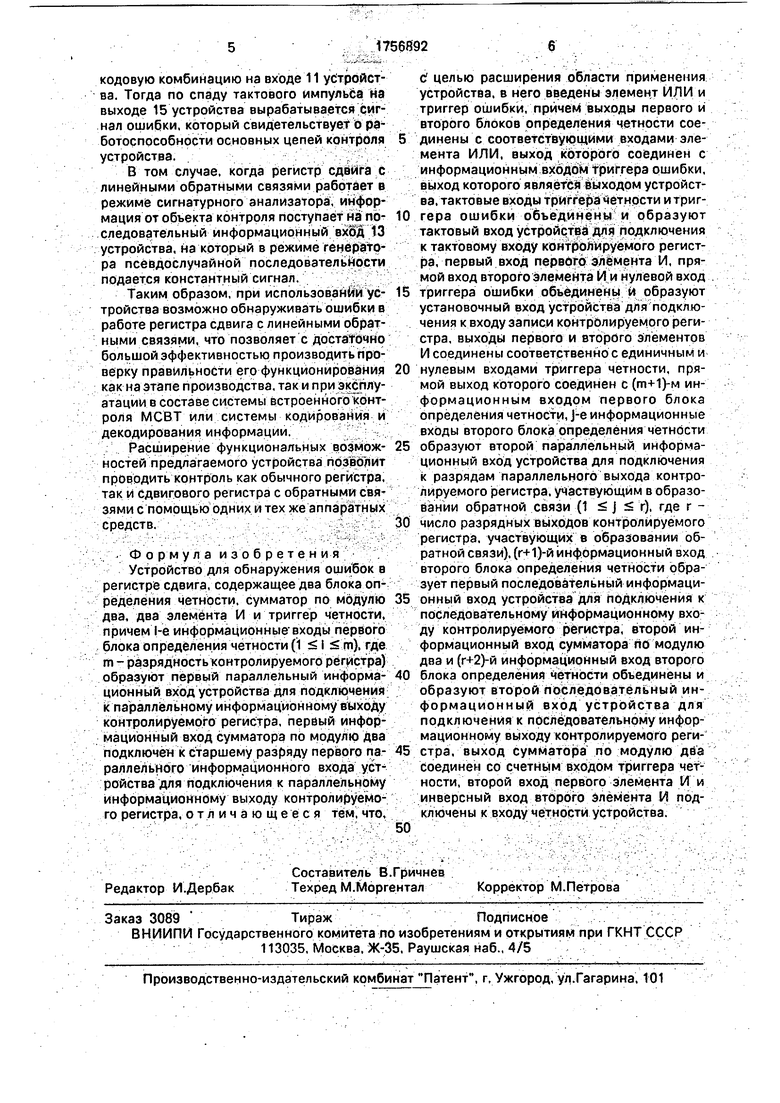

На чертеже приведена функциональная схема устройства.

Устройство содержит контролируемый регистр 1, первый 2 и второй 3 блоки определения четности, сумматор м одулю два, элемент ИЛИ 5, элементы И 6 и 7, триггер 8 ошибки, триггер 9 четности, тактовый вход 10, параллельный информационный вход 11, вход 12 строба записи и последова- тельный информационный вход 13 контролируемого регистра 1, вход 14 четности устройства, выход 15 устройства, сдвиговый регистр 16 контролируемого регистра 1, сумматор 17 по мбдулю два контролируемого регистра 1. i

Контролируемый решстр 1 сдвига представляет собой сиг натурный анализатор, который состоит из сдвигового регистра 16 и сумматора 17 по модулю два, с помощью которого осуществляется сложение по модулю два содержимого разрядов, участвующих в обратной с вязи, и подаче результата сложения на вход младшего разряда регистра 16.|

Устройство работает следующим образом.

Информация в параллельном коде выставляется на параллельном информационном входе 11 устройства, при этом на вход 14 четности устройства подается бит, дополняющий параллельный код на входе 11 устройства до четности. В зависимости от значения бита четности открывается либо элемент И 6, либо элемент И 7. По единичному импульсу, поступающему на вход 12 строба записи устройства, информация с параллельного информационного входа 11 устройства заносится в регистр 16 контролируемого регистра 1 сдвига, сбрасывается (устанавливается в нулевое состояние) триггер 8 ошибки и триггер 9 четности переходит в состояние, дополняющее состояние регистра 16 до четности. Первый блок 2 определения четности вычисляет четность ( содержимого регистра 16 и триггера 9 четности, Если содержимое четно, то на информационный вход триггера 8 ошибки через элемент ИЛИ 5 поступает нулевой сигнал, в противном случае - единичный. По фронту тактового импульса, поступающего на вход 10 устройства, происходит сдвиг содержимого регистра 16, а также изменение состояния триггера 9 четности на Ьротово- положное при наличии единичного сигнала

на его счетном входе. Такая необходимость может возникнуть, если сдвиг содержимого регистра (для определенности положим, что сдвиг осуществляется в сторону старшего

разряда) приводит к изменению четности содержимого регистра 16 и триггера 9 четности. Если при сдвиге содержимого реги-- стра 16 утеряно (сдвинуто) значение старшего разряда, равное 1 (О), а в млад0 ший разряд заносится значение О (1), то для сохранения четности содержимого системы регистр 16 - три(гер 9 четности необходимо заменить состояние последнего на противоположное.

5 Таким образом, по фронту импульса, подаваемого на тактовый вход 10 устройства, происходит сдвиг содержимого регистра 16 сдвига и синхронизация записи информации, подаваемой с выхода сумматора 4 по

0 модулю два на счетный вход триггера 9 четности. По спаду тгктового импульса происходит запись информации по информационному входу в триггер 8 ошибки, Если переходы регистра состояния в состо5 яние выполняются верно, то на выходе пер- вого блока 2 определения четности поддерживается нулевой сигнал и триггер 8 ошибки остается в нулевом состоянии. При возникновении ошибки в переходах регист0 ра 16 контролируемого регистра 1 нарушается четность его содержимого и триггера 9 четности, что переключает триггер 8 ошибки в единичное состояние, которое вызывает появление сигнала ошибки на выходе 15

5 уст ройства. В этом случае, когда возникает ошибка в работе сумматора 17 по модулю два. входящего в состав контролируемого регистра 1 сдвига с линейными обратными связями, на выходе второго блока 3 опреде0 ления четности появляется единичный сигнал несравнения, который через элемент ИЛИ 5 поступает на информационный вход триггера 8 ошибки и по спаду тактового импульса на выходе 15 устройства появляется

5 единичный сигнал ошибки.

При использовании устройства в составе системы встроенного контроля МСВТ сигнал с выхода 15 может быть подан на вход прерывания микропроцессора, кото0 рый. прекратив выполнение основной программы, переходит к программе обработки прерывания для выявления причин его возникновения,

В устройстве предусмотрена возмож5 ность Организации самоконтроля. Для этого одновременно с подачей информации на параллельный информационный вход 11 устройства на вход 14 четности устройства необходимо принудительно подать сигнал (1 или О), дополняющий до нечетности

кодовую комбинацию на входе 11 устройства. Тогда по спаду тактового импульса на выходе 15 устройства вырабатывается сигнал ошибки, который свидетельствует о работоспособности основных цепей контроля устройства.

В том случае, когда регистр сдвига с линейными обратными связями работает в режиме сигнатурного анализатора, информация от объекта контроля поступает на последовательный информационный вход 13 устройства, на который в режиме генератора псевдослучайной последовательности подается константный сигнал.

Таким образом, при использовании устройства возможно обнаруживать ошибки в работе регистра сдвига с линейными обратными связями, что позволяет с достаточно большой эффективностью производить проверку правильности его функционирования как на этапе производства, так и при эксплуатации в составе системы встроенного контроля МСВТ или системы кодирования и декодирования информации.

Расширение функциональных возможностей предлагаемого устройства позволит проводить контроль как обычного регистра, так и сдвигового регистра с обратными связями с помощью одних и тех же аппаратных средств.

Формула изобретения Устройство для обнаружения ошибок в регистре сдвига, содержащее два блока определения четности, сумматор по модулю два, два элемента И и триггер четности, причем 1-е информационные входы первого блока определения четности (1 S i m), где m - разрядность контролируемого регистра) образуют первый параллельный информационный вход устройства для подключения к параллельному информационному выходу контролируемого регистра, первый информационный вход сумматора по модулю два подключен к старшему разряду первого параллельного информационного входа устройства для подключения к параллельному информационному выходу контролируемого регистра, отличающееся тем, что,

с1 целью расширения области применения устройства, в него введены элемент ИЛИ и триггер ошибки, причем выходы первого и второго блоков определения четности соединены с соответствующими входами элемента ИЛИ, выход которого соединен с информационным входом триггера ошибки, выход которого является выходом устройства, тактовые входы триггера четности и триггера ошибки объединены и образуют тактовый вход устройства для подключения к тактовому входу контролируемого регистра, первый вход первого элемента И, прямой вход второго элемента И и нулевой вход

триггера ошибки объединены и образуют установочный вход устройства для подключения к входу записи контролируемого регистра, выходы первого и второго элементов И соединены соответственно с единичным и

нулевым входами триггера четности, прямой выход которого соединен с (т+1)-м информационным входом первого блока определения четности, j-e информационные входы второго блока определения четности

образуют второй параллельный информационный вход устройства для подключения к разрядам параллельного выхода контролируемого регистра, участвующим в образовании обратной связи (1 j г), где г число разрядных выходов контролируемого регистра, участвующих в образовании обратной связи), (г+1)-й информационный вход второго блока определения четности образует первый последовательный информационный вход устройства для подключения к последовательному информационному входу контролируемого регистра, второй информационный вход сумматора по модулю два и (г+2)-й информационный вход второго

блока определения четности объединены и образуют второй последовательный информационный вход устройства для подключения к последовательному информационному выходу контролируемого регистра, выход сумматора по модулю два соединен со счетным входом триггера четности, второй вход первого элемента И и инверсный вход второго элемента И подключены к входу четности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| ДВУХУРОВНЕВОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК | 1992 |

|

RU2037891C1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля регистра сдвига | 1981 |

|

SU964646A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| Устройство для контроля кода на четность | 1988 |

|

SU1529224A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Многоканальное устройство исправления ошибок для магнитных накопителей | 1986 |

|

SU1383440A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении контролируемых систем. Цель изобретения - расширение области применения устройства. На первый блок 2 определения четности заводятся выходы всех разрядов контролируемого регистра 1 сдвига, который представляет собой сигнатурный анализатор, и выход триггера 9 четности, где формируется предсказанный сигнал четности. Единичный сигнал с выхода блока 2 через элемент ИЛИ 5 поступает на информационный вход триггера 8 ошибки, формируя сигнал неисправности на выходе 15 устройства. Работа сумматора 17 по модулю два контролируемого регистра 1 дублируется вторым блоком 3 определения четности, единичный сигнал с выхода которого через элемент ИЛИ 5 также поступает на вход триггера 8 ошибки. Начальная установка триггера 9 четности осуществляется с помощью элементов И 6, 7. Изменение состояния триггера 9 при сдвиге информации в контролируемом регистре 1 осуществляется с помощью сумматора 4 по модулю два. 1 ил. (Л С

| Устройство для обнаружения ошибок в регистре сдвига | 1982 |

|

SU1048477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения ошибок в регистре сдвига | 1978 |

|

SU710043A2 |

Авторы

Даты

1992-08-23—Публикация

1990-05-14—Подача