Изобретение относится к радиоизмерительной технике и может быть использовано для синхронизации фазы одного генератора по фазе другого.

Известно устройство синхронизации фаз двух генераторов, содержащее последовательно соединенные местный генератор, управляемую линию задержки и преобразователь частоты, а также опорный генератор и фазовый дискриминатор, по- следовательно соединенные реверсивный счетчик и дешифратор, элемент И и три ключа, преобразователь код-напряжение, амплитудный компаратор, блок анализа, коммутируемую зарядно-разрядную цепь, блок коммутируемых источников постоянного напряжения и блок коммутируемых запоминающих элементов,

В данном устройстве синхронизации фаз в режиме слежения одновременно ра- ботают две следящие системы -- за фазой выходного сигнала и за напряжением на рабочем конденсаторе. Дополнительная следящая система в режиме слежения обеспечивает непрерывную работу основной следящей системы при превышении разности фаз между сигналами опорного и местного генераторов величины 2 п (диапазона перестройки управляемой линии задержки), Кроме того, дополнительная следящая сие- тема обеспечивает длительное хранение фазы опорного генератора с высокой точностью.

Недостатками устройства являются невысокие спектральные характеристики выходного сигнала, а, кроме того, при влиянии дестабилизирующих факторов, например температуры окружающей среды, изменится величина задержки линии (2 ), что приведет, в случае уменьшения времени задержки, к возникновению в момент переключения колебательного процесса. Таким образом, устройство обладает малым запасом устойчивости и не может надежно синхронизиро- вать фазы двух генераторов.

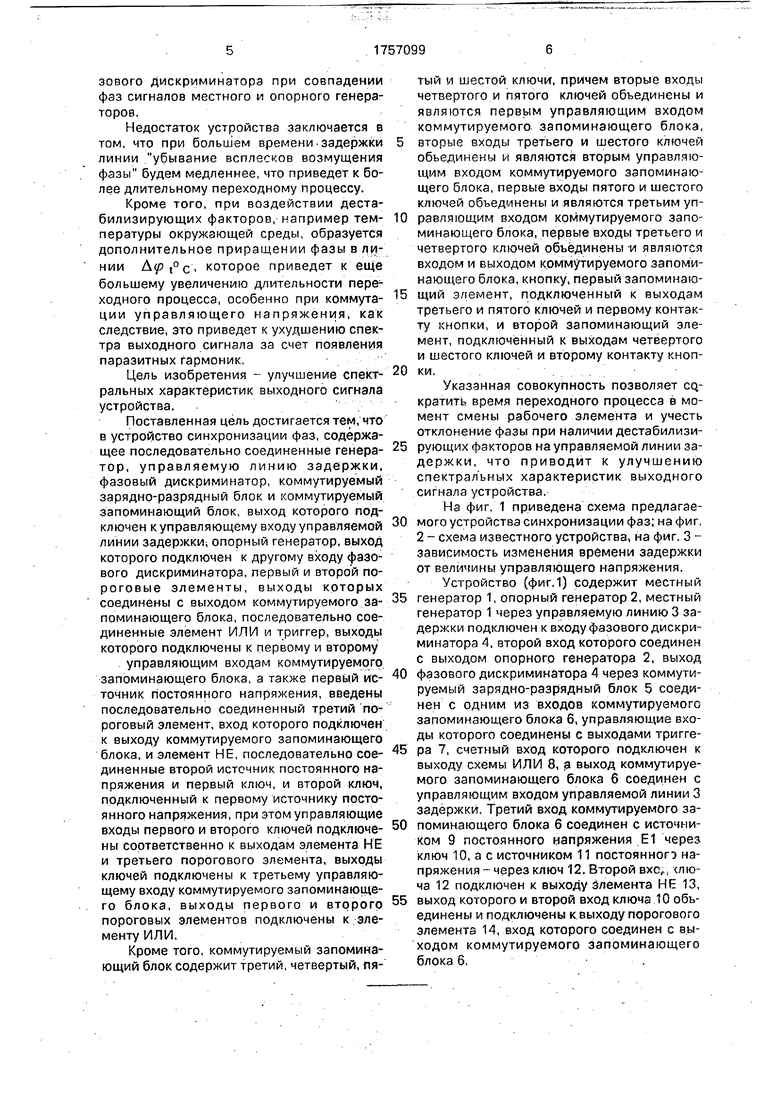

Наиболее близким к предлагаемому является устройство синхронизации фаз двух генераторов. Это устройство содержит (фиг.2) последовательно соединенные мест- ный генератор 1, управляемую линию задержки 3 и фазовый дискриминатор 4, коммутируемый зарядно-разрядный блок 5, подключенный к одному из входов коммутируемого запоминающего блока 6, к другому входу которого подсоединен источник питания (В1) 9, При этом управляющие входы коммутируемого запоминающего блока 6 подключены к триггеру 7, а выход соединен

с входами пороговых элементов 22, 23 и входом управляемой линии задержки.

Кроме того, устройство содержит опорный генератор 2, соединенный с входом фазового дискриминатора 24 и через управляемую линию задержки с входом фазового дискриминатора. Выход фазового дискриминатора соединен с первыми входами элементов И 26, И 25, вторые входы которых соединены соответственно с выходами пороговых элементов 22 и 23, Выходы элементов И 25, И 26 соединены с входами элемента ИЛИ 8, выход которого соединен с переключающим входом триггера 7

Известное устройство работает следующим образом.

Диапазону регулирования управляемой линии задержки данной схемы, равному А л, соответствует диапазон изменения управляющих напряжений на линии задержки Д U UCMSKC UCMMH гДе смакс и UCMHH

выбраны таким образом, чтобы величины задержек входного сигнала были равны (п-1)-2 лги (п+1) 2 я, где п - целое число

Коммутируемый запоминающий блок 8 содержит два запоминающих элемента (конденсатора), один из которых является рабочим, а другой - вспомогательным. В исходном положении на рабочем запоминающем элементе устанавливается начальное напряжение Е1, В зависимости от соотношения фаз опорного и выходного сигналов на выходе фазового дискриминатора 4 образуется сигнал положительной отрицательной полярности. Пусть фаза опорного сигнала опережает фазу сигнала на выходе линии задержки 4. Тогда положительное напряжение с выхода фазового дискриминатора 4 воздействует на коммутируемый зарядно-разрядный блок 5 таким образом, что напряжение на рабочем запоминающем элементе увеличивается. При этом изменяется фаза сигнала на выходе линии задержки 3, приближаясь к фазе сигнала опорного генератора.

Напряжение на рабочем запоминающем элементе следит за изменением разности фаз частотного и опорного генераторов и колеблется около значения, соответствующего нулевому рассогласованию фаз опорного и выходного сигналов. При достижении на рабочем запоминающем элементе напряжения Усмэкс (смин) по сигналу с выхода схемы ИЛИ 8 триггер 7 меняет свое состояние и, воздействуя на коммутируемые запоминающие элементы, подключает другой запоминающий элемент, который становится рабочим. Команда на смену рабочего конденсатора выдается с выхода фазового дискриминатора при совпадении фаз сигналов местного и опорного генераторов.

Недостаток устройства заключается в том, что при большем времени задержки линии убывание всплесков возмущения фазы будем медленнее, что приведет к более длительному переходному процессу.

Кроме того, при воздействии дестабилизирующих факторов, например температуры окружающей среды, образуется дополнительное приращении фазы в линии , которое приведет к еще большему увеличению длительности переходного процесса, особенно при коммутации управляющего напряжения, как следствие, это приведет к ухудшению спектра выходного сигнала за счет появления паразитных гармоник

Цель изобретения - улучшение спектральных характеристик выходного сигнала устройства.

Поставленная цель достигается тем, что в устройство синхронизации фаз, содержащее последовательно соединенные генератор, управляемую линию задержки, фазовый дискриминатор, коммутируемый зарядно-разрядный блок и коммутируемый запоминающий блок, выход которого подключен к управляющему входу управляемой линии задержки, опорный генератор, выход которого подключен к другому входу фазового дискриминатора, первый и второй пороговые элементы, выходы которых соединены с выходом коммутируемого запоминающего блока, последовательно соединенные элемент ИЛИ и триггер, выходы которого подключены к первому и второму

управляющим входам коммутируемого запоминающего блока, а также первый источник постоянного напряжения, введены последовательно соединенный третий пороговый элемент, вход которого подключен к выходу коммутируемого запоминающего блока, и элемент НЕ, последовательно соединенные второй источник постоянного напряжения и первый ключ, и второй ключ, подключенный к первому источнику постоянного напряжения, при этом управляющие входы первого и второго ключей подключены соответственно к выходам элемента НЕ и третьего порогового элемента, выходы ключей подключены к третьему управляющему входу коммутируемого запоминающего блока, выходы первого и второго пороговых элементов подключены к элементу ИЛИ,

Кроме того, коммутируемый запоминающий блок содержит третий, четвертый, пятый и шестой ключи, причем вторые входы четвертого и пятого ключей объединены и являются первым управляющим входом коммутируемого запоминающего блока, 5 вторые входы третьего и шестого ключей объединены и являются вторым управляющим входом коммутируемого запоминающего блока, первые входы пятого и шестого ключей объединены и являются третьим уп0 равляющим входом коммутируемого запоминающего блока, первые входы третьего и четвертого ключей объединены и являются входом и выходом коммутируемого запоминающего блока, кнопку, первый запоминаю5 щий элемент, подключенный к выходам третьего и пятого ключей и первому контакту кнопки, и второй запоминающий элемент, подключенный к выходам четвертого и шестого ключей и второму контакту кноп0 ки.

Указанная совокупность позволяет cq- кратить время переходного процесса в момент смены рабочего элемента и учесть отклонение фазы при наличии дестабилизи5 рующих факторов на управляемой линии за- держки, что приводит к улучшению спектральных характеристик выходного сигнала устройства.

На фиг, 1 приведена схема предлагае0 мого устройства синхронизации фаз; на фиг

2 - схема известного устройства, на фиг. 3 зависимость изменения времени задержки

от величины управляющего напряжения.

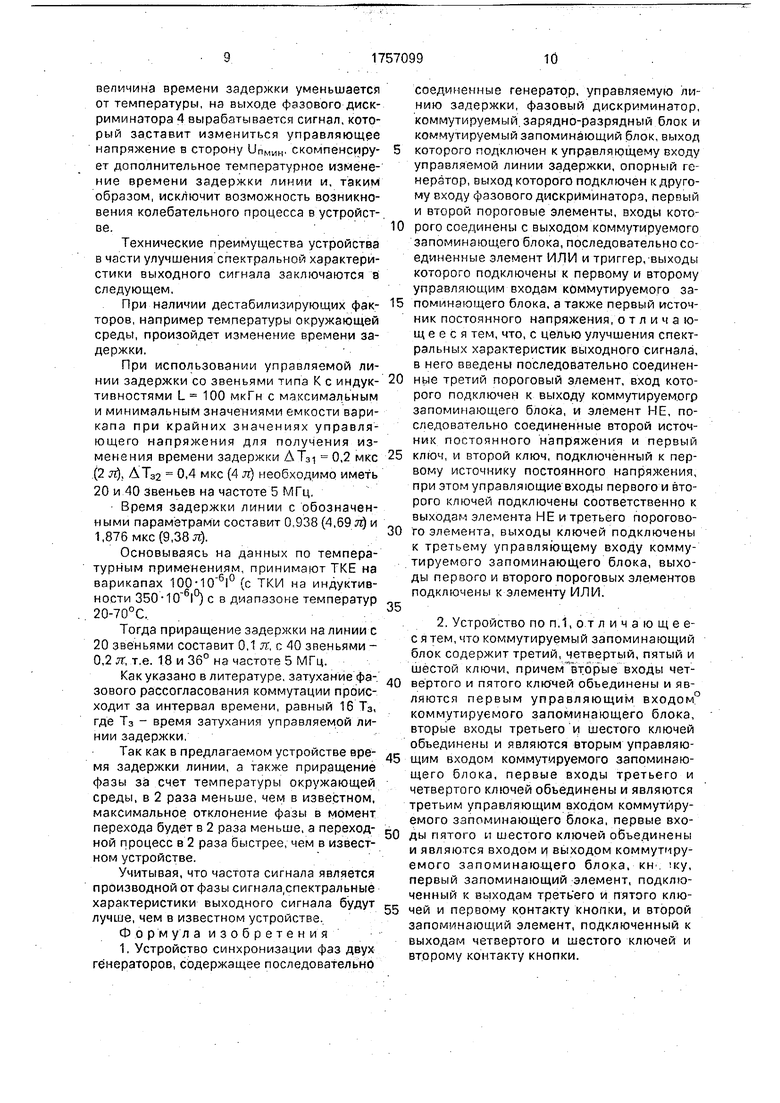

Устройство (фиг. 1} содержит местный

5 генератор 1, опорный генератор 2, местный генератор 1 через управляемую линию 3 задержки подключен к входу фазового дискриминатора 4, второй вход которого соединен с выходом опорного генератора 2, выход

0 фазового дискриминатора 4 через коммутируемый зарядно-разрядный блок 5 соединен с одним из входов коммутируемого запоминающего блока 6, управляющие входы которого соединены с выходами тригге5 ра 7, счетный вход которого подключен к выходу схемы ИЛИ 8, а выход коммутируемого запоминающего блока б соединен с управляющим входом управляемой линии 3 задержки. Третий вход коммутируемого за0 поминающего блока б соединен с источником 9 постоянного напряжения Е1 через ключ 10, а с источником 11 постоянного напряжения - через ключ 12. Второй вхс лю- ча 12 подключен к выходу элемента НЕ 13,

5 выход которого и второй вход ключа 10 объединены и подключены к выходу порогового элемента 14, вход которого соединен с выходом коммутируемого запоминающего блока б,

Коммутируемый запоминающий блок 6 содержит пусковую кнопку 15, соединенную с первым 16 и вторым 17 запоминающими .шементами (конденсаторами С1 и С 2), четыре ключа 18-21. Первые входы ключей 18, 19 объединены и подключены к третьему входу коммутируемого запоминающего блока 6. Второй вход ключа 19 объединен с вторым входом ключа 20 и соединен с первым управляющим входом коммутируемого запоминающего блока 6, к второму управляющему входу этого блока подключены объединенные вторые входы ключей 18, 19. Первые входы ключей 20, 21 также объединены и являются входом-выходом коммутируемого запоминающего блока 6, Первые входы четвертого и шестого ключей объединены и подключены к второму запоминающему злементу С1 и второму контакту кнопки, а первые входы третьего и пятого ключей объединены и подключены к первому запоминающему элементу С2 и первому контакту кнопки. К входам элемента ИЛИ 8 подключены выходы пороговых элементов 22, 23, входы которых объединены и подключены к выходу коммутируемого запоминающего блока 6.

Устройство (фиг 1} работает следующим образом.

С выхода местного генератора 1 сигнал подается на вход управляемой линии 3 задержки. Задержка, а следовательно, и фаза выходного сигнала, зависит от приложенного к ее управляющему входу постоянного напряжения, источником которого служит один из запоминающих элементов 16, 17.

Пусть в исходном состоянии триггер 7 находится в таком положении, при котором ключи 19, 20 будут открыты, а ключи 18, 21 - закрыты. В этом случае запоминающий элемент 16 (конденсатор С1) становится рабочим, а запоминающий элемент 17 (конденсатор С2) - вспомогательным, Пороговый элемент 14 вырабатывает напряжение, при котором открыт ключ 10, а вспомогательный конденсатор С2 через открытые ключи 10, 19 подключен к источнику 9 постоянного напряжения Е1. Нажатием кнопки 15 рабочей конденсатор С1 подключается параллельно конденсатору С2 и на них устанавливается напряжение источника Е1.

8 зависимости от соотношения фаз выходного и опорного сигналов на выходе фазового дискриминатора 4 образуется сигнал, соответствующий опережению или отставанию фазы выходного сигнала устройства. Пусть фаза опорного сигнала опережает фазу сигнала на выходе управляемой линии 3 задержки, Фазовый

дискриминатор 4 вырабатывает сигнал на подключение разрядной цепи коммутируемого зарядно-разрядного блока (КЗРБ) 5. При достижении нулевого значения рассогласования фаз, а затем отставании фазы опорного сигнала в блоке КЗРБ5, включается зарядная цепь. Таким образом, напряжение на рабочем запоминающем элементе 16 будет следить за изменением разности фаз

0 местного и опорного генераторов и колебаться около значения, соответствующего нулевому рассогласованию фаз сигнала опорного генератора и сигнала с выхода линии 3 задержки. При достижении на рабо5 чем запоминающем элементе напряжения UnM3Kc (порогового напряжения, задаваемого пороговым элементом 22) срабатывает пороговый элемент 22 и происходит смена состояния триггера 7, который, воздействуя

0 на коммутируемые запоминающие элементы, отключает рабочий запоминающий элемент 16 (конденсатор C1j от управляющего входа управляемой линии 3 задержки и подключает к этому входу запоминающий эле5 мент 17 (конденсатор С2), который становится рабочим и к которому было подключено напряжение от источника 9 постоянного напряжения Е1. Запоминающий элемент 16 становится вспомогательным и

0 к нему подключается источник 11 постоянного напряжения Е2, Поскольку изменение управляющего напряжения от UCMaKC до UCMMH (E2) соответствует изменению фазы выходного сигнала 2 п, на выходе фазового дискриминатора 4 появится сигнал, который будет воздействовать на КЗРБ 5 аналогично описанному.

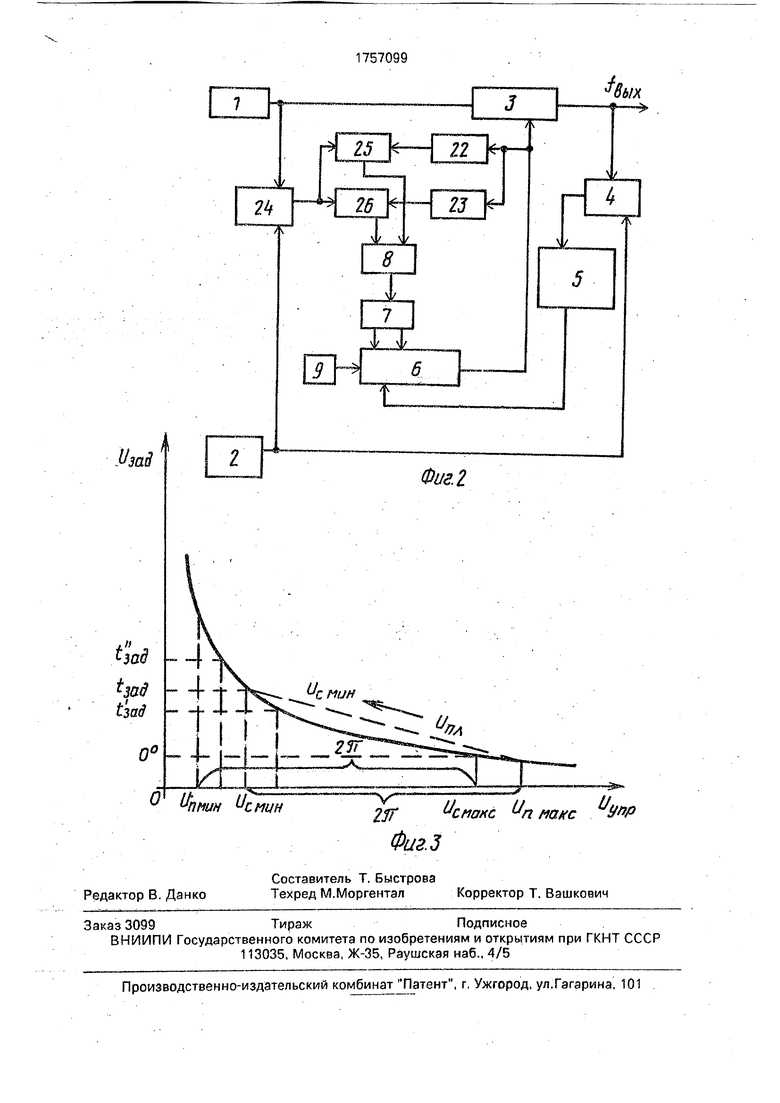

При обратном изменении фазы рассогласование генераторов напряжения управления будет меняться от UnMnn к Е1, При достижении ипмин произойдет переключение управляющего напряжения в исмакс- Характеристика изменения фазы выходного

5 сигнала от управляющего напряжения показана на фиг. 3.

Рассмотрим работу устройства под влиянием дестабилизирующих факторов, например при понижении температуры

0 окружающей среды. Величина времени задержки при этом уменьшается, Для сохранения диапазона регулирования линии задержки равным 2 п необходимо управляющее напряжение U. Пусть расхождение

5 генераторов таково, что напряжение управления линии задержки изменяется в сторону увеличения напряжения. При достижении Упмакс должно произойти пере- ключение в исмин- Но вследствие того, что

0

величина времени задержки уменьшается от температуры, на выходе фазового дискриминатора 4 вырабатывается сигнал, который заставит измениться управляющее напряжение в сторону иПМин скомпенсирует дополнительное температурное изменение времени задержки линии и, таким образом, исключит возможность возникновения колебательного процесса в устройстве.

Технические преимущества устройства в части улучшения спектральной характеристики выходного сигнала заключаются в следующем,

При наличии дестабилизирующих факторов, например температуры окружающей среды, произойдет изменение времени задержки.

При использовании управляемой линии задержки со звеньями типа К с индук- тивностями L 100 мкГн с максимальным и минимальным значениями емкости варикапа при крайних значениях управляющего напряжения для получения изменения времени задержки АТ31 0,2 мкс (2 л), АТ32 0,4 мкс (4 л) необходимо иметь 20 и 40 звеньев на частоте 5 МГц.

Время задержки линии с обозначен- ными параметрами составит 0 938 (4,69 л) и 1,876 мкс (9,38 л).

Основываясь на данных по температурным применениям, принимают ТКЕ на варикапах 100-Ю 6 0 (с ТКИ на индуктивности 350-10 И с в диапазоне температур 20-70°С.

Тогда приращение задержки на линии с 20 звеньями составит 0,1 я, с 40 звеньями - 0,2 я, т.е. 18 и 36° на частоте 5 МГц.

Как указано в литературе, затухание фазового рассогласования коммутации происходит за интервал времени, равный 16 Тз, где Т3 - время затухания управляемой линии задержки,

Так как в предлагаемом устройстве время задержки линии, а также приращение фазы за счет температуры окружающей среды, в 2 раза меньше, чем в известном, максимальное отклонение фазы в момент перехода будет в 2 раза меньше, а переходной процесс в 2 раза быстрее, чем в известном устройстве.

Учитывая, что частота сигнала является производной от фазы сигнала,спектральные характеристики выходного сигнала будут лучше, чем в известном устройства.

Формула изобретения

1. Устройство синхронизации фаз двух генераторов, содержащее последовательно

соединенные генератор, управляемую линию задержки, фазовый дискриминатор, коммутируемый зарядно-разрядный блок и коммутируемый запоминающий блок, выход 5 которого подключен к управляющему входу управляемой линии задержки, опорный генератор, выход которого подключен к другому входу фазового дискриминатора, перрый и второй пороговые элементы, входы кото0 рого соединены с выходом коммутируемого запоминающего блока, последовательно соединенные элемент ИЛИ и триггер, выходы которого подключены к первому и второму управляющим входам коммутируемого за5 поминающего блока, а также первый источник постоянного напряжения, отличающееся тем, что, с целью улучшения спектральных характеристик выходного сигнала, в него введены последовательно соединен0 ные третий пороговый элемент, вход которого подключен к выходу коммутируемогр запоминающего блока, и элемент НЕ, последовательно соединенные второй источник постоянного напряжения и первый

5 ключ, и второй ключ, подключенный к первому источнику постоянного напряжения, при этом управляющие входы первого и второго ключей подключены соответственно к выходам элемента НЕ и третьего порогово0 го элемента, выходы ключей подключены к третьему управляющему входу коммутируемого запоминающего блока, выходы первого и второго пороговых элементов подключены к элементу ИЛИ.

5

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что коммутируемый запоминающий блок содержит третий, четвертый, пятый и шестой ключи, причем вторые входы чет0 вертого и пятого ключей объединены и являются первым управляющим входом0 коммутируемого запоминающего блока, вторые входы третьего и шестого ключей объединены и являются вторым управляю5 щим входом коммутируемого запоминающего блока, первые входы третьего и четвертого ключей объединены и являются третьим управляющим входом коммутируемого запоминающего блока, первые вхо0 ды пятого и шестого ключей объединены и являются входом и выходом коммутируемого запоминающего блока, кн ку, первый запоминающий элемент, подключенный к выходам третьего и пятого клю5 чей и первому контакту кнопки, и второй запоминающий элемент, подключенный к выходам четвертого и шестого ключей и второму контакту кнопки.

Уза

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации фаздВуХ гЕНЕРАТОРОВ | 1978 |

|

SU819975A1 |

| Устройство синхронизации фаз сигналов двух генераторов | 1978 |

|

SU771886A1 |

| Устройство коррекции временных искажений | 1980 |

|

SU932648A1 |

| Измеритель скорости звука | 1990 |

|

SU1758444A1 |

| Устройство коррекции временных искажений | 1980 |

|

SU906031A1 |

| Устройство компенсации временных искажений | 1980 |

|

SU965018A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1986 |

|

SU1394411A1 |

| УСТРОЙСТВО ДЛЯ ВОЗБУЖДЕНИЯ УДАРНЫХ ИМПУЛЬСОВ | 1993 |

|

RU2019795C1 |

Использование: радиоизмерительная техника, синхронизация фазы одного генератора по фазе другого. Сущность изобрете- ния: устройство синхронизации фаз содержит 2 генератора (1,2), 1 управляемую линию задержки, 1 фазовый дискриминатор 4, 1 коммутируемый зарядно-разрядный блок 5, 1 коммутируемый запоминающий блок 6, 1 триггер 7, элемент ИЛИ 8, 2 источника постоянного напряжения 9,11,2 ключа 10, 12, 1 элемент НЕ 13 и 3 пороговых элемента 14, 22, 23. Коммутируемый запоминающий блок б содержит 4 ключа 18,19, 20, 21, 2 запоминающих блока 16, 17 и кнопку 15. Поставленная цель - улучшение спектральных характеристик выходного сигнала - достигается за счет сокращения времени задержки управляемой линии- задержки и уменьшения времени переходного процесса. 1 з.п. ф-лы, 1 ил, fax (Л С VJ СЛ Ч О sQ О Фиг.1

зад W

&

пмин Uс мин

2JT УСПОКС УП махе W

Фиг.З

| Устройство для синхронизации фаздВуХ гЕНЕРАТОРОВ | 1978 |

|

SU819975A1 |

Авторы

Даты

1992-08-23—Публикация

1990-06-25—Подача