ш

i

Вмд1

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Устройство цифровой передачи и приема телевизионного сигнала | 1985 |

|

SU1309327A1 |

| Приемник частотно-манипулированных сигналов | 1990 |

|

SU1786680A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ | 2021 |

|

RU2780985C1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| ГЕНЕРАТОР КВАЗИОРТОГОНАЛЬНО-ПРОТИВОПОЛОЖНЫХ СИГНАЛОВ | 1999 |

|

RU2187144C2 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2019 |

|

RU2711054C1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

Изобретение относится к технике связи Цель изобретения - повышение помехоустойчивости устр-ва. Устр-во для передачи бинарной информации содержит г-р 1, эл т И 2, Т-триггер 3, регистр 4 сдвига, ЦАП 5, сумматоры 6 и 14 по модулю два, компараторы 7 и 11, интегратор 8, D-триггеры 9 и 15, двухполупериодный выпрямитель 10 пинию задержки 12 и сумматор 13. Цель достигается путем подавления низкочастотных составляющих в спектре линейного передаваемого сигнала. 2 ил.

Bxod 7

2

Изобретение относится к технике связи и может использоваться для передачи цифровых сигналов в системах с импульсно-ко- довой модуляцией.

Цепь изобретения - повышение поме- хоустойчивости устройства путем подавления низкочастотных составляющих в спектре линейного передаваемого сигнала.

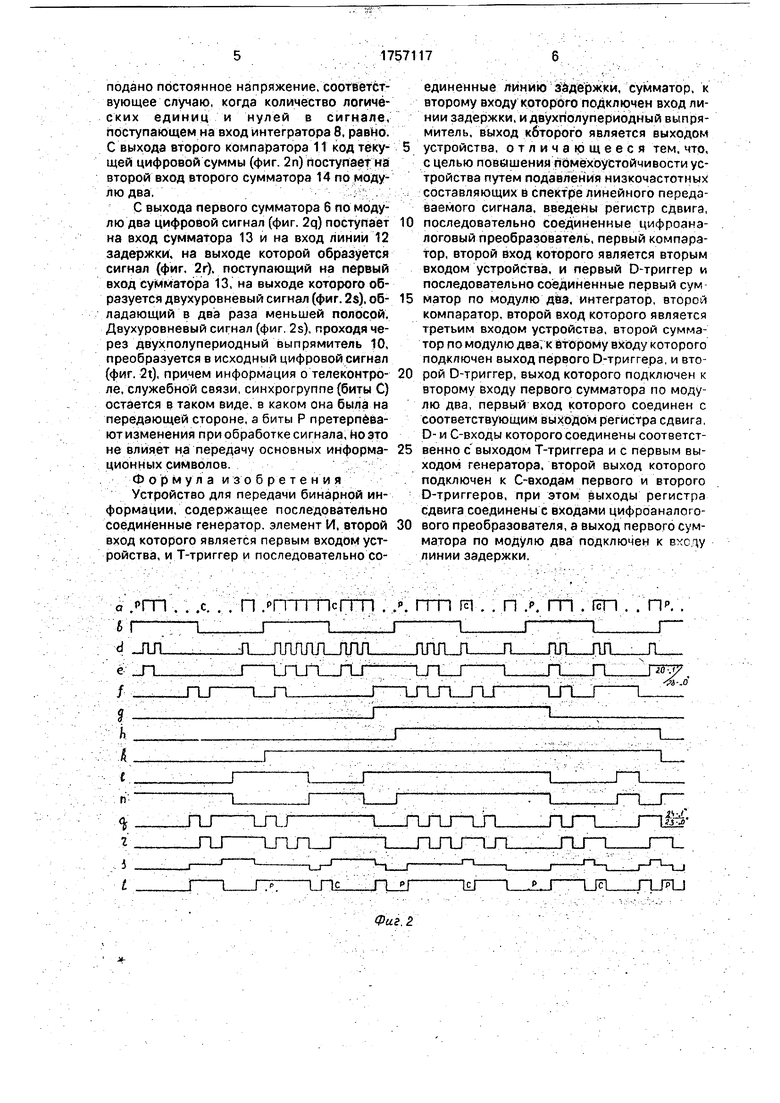

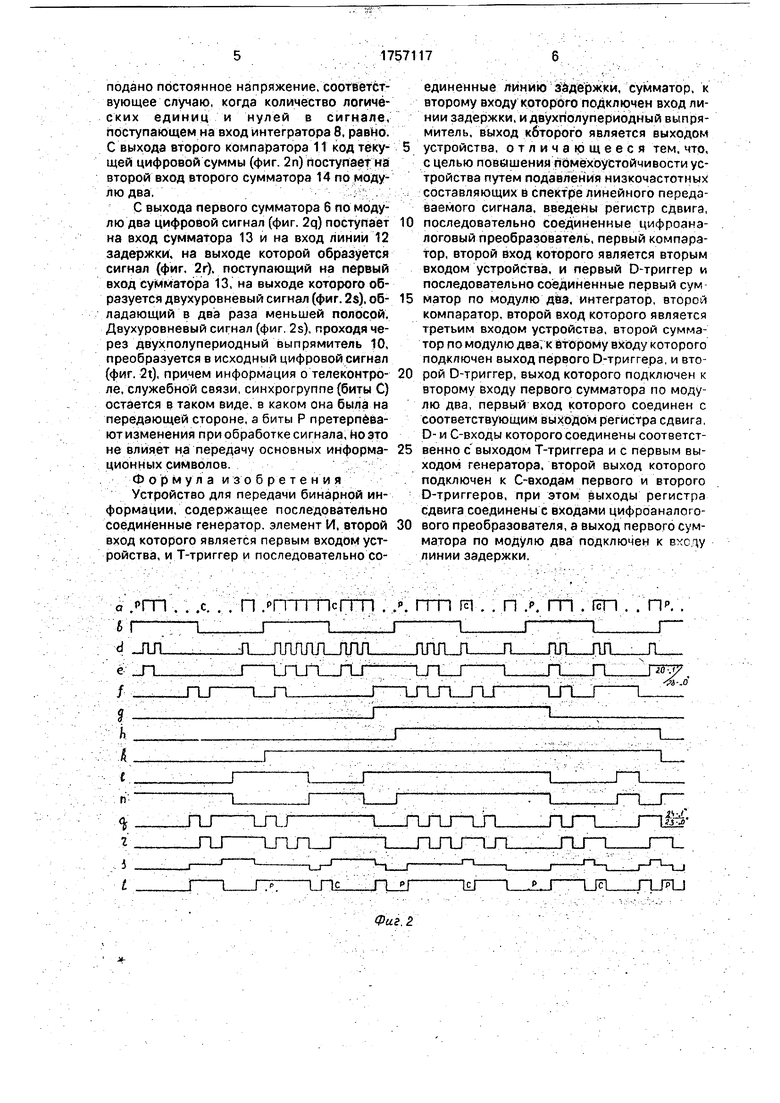

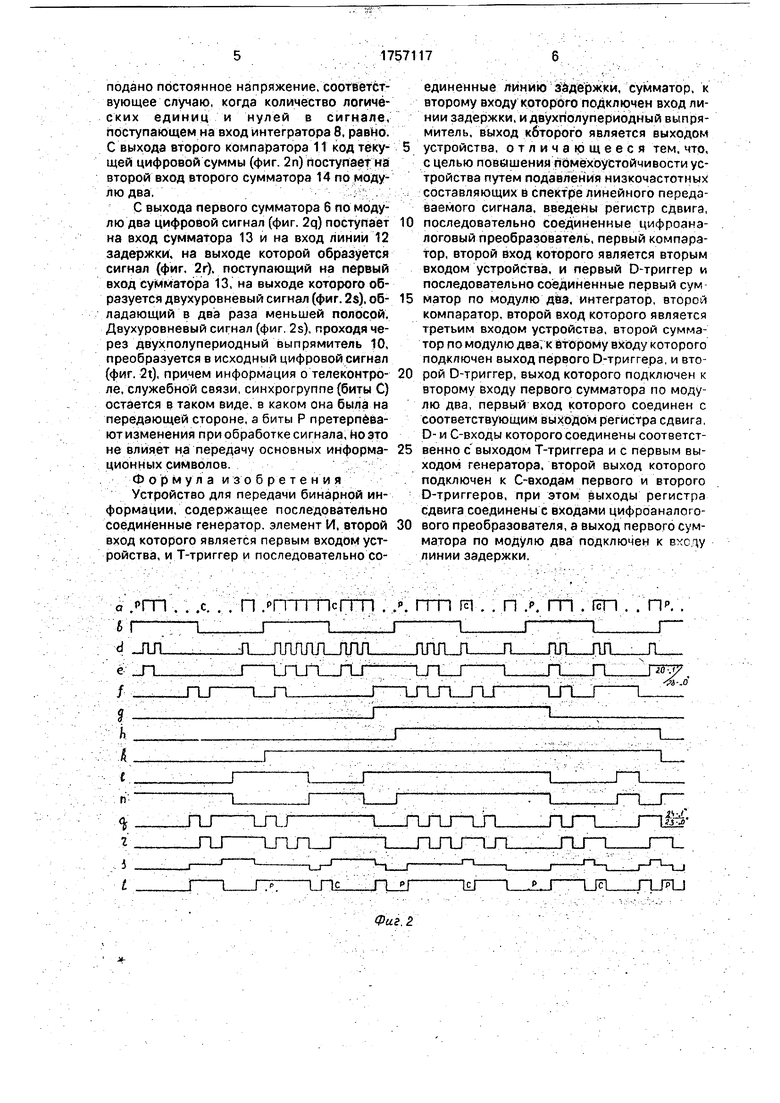

На фиг. 1 представлена структурная электрическая схема предложенного уст- ройства; на фиг, 2 - эпюры напряжения, поясняющие его работу.

Устройство для передачи бинарной информации содержит генератор 1, элемент И 2. Т-триггер 3, регистр 4 сдвига, цифроана- лотовый преобразователь 5, первый сумматор б по модулю два, первый компаратор, интегрэторВ, первый D-триггер 9, двухполу- периодный выпрямитель 10, второй компаратор 11, линию 12 задержки, сумматор 13, второй сумматор 14 по модулю два и второй D-триггер 15.

Устройство работает следующим образом.

На первый вход устройства поступает информационный сигнал в формате NRZ вида m BIPIC, полученным путем добавления к каждым m информационным битам двух дополнительных битов - бита Р и бита С (фиг 2а), На место бита Р записан уровень логического нуля, на место бита С записана информация о телеконтроле, служебной связи, синхрогруппе. При этом два дополнительных бита добавляются на каждые десять информационных бит (фиг. 2а). Далее цифровой сигнал поступает на второй вход элемента 1/1 2, на первый вход которого поступает хронирующая тактовая частота (фиг. 2Ь), в результате чего на выходе элемента И 2 образуется поток импульсов (фиг, 2d), со- ответствующий логическим единицам поступающего на первый вход устройства цифрового сигнала. Импульсы поступают на вход Т-триггера 3, на выходе которого получается сигнал (фиг. 2е), который поступает на D-вход регистра 4 сдвига, на С-вход которого подается хронирующая тактовая частота с выхода генератора 1. Регистр 4 сдвига предназначен для преобразования цифрового сигнала, поступающего на его D-вход, из последовательного кода в параллельный, С первого, второго(m+2)-ro выходов регистра 4 сдвига цифровые сигналы

поступают на первый, второй (т+2)-й

входы цифрозналогового преобразователя 5, который предназначен для преобразования цифрового сигнала в аналоговый и с выхода которого сигнал в аналоговой форме поступает на второй вход первого компаратора 7.

На выходе первого коммутатора 7 получается сигнал (фиг. 2д) - код цифровой суммы группы, показывающий, сколько единиц находится в группе импульсов на (т+2) бит - больше половины либо меньше или равно половине импульсов из (т+2) бит. На первый вход первого компаратора 7 подано по второму входу устройства постоянное напряжение, соответствующее случаю, когда в пачке из (т+2) бит количество логических единиц равно 1/2(т+2).

Далее сигнал (фиг, 2д) - код цифровой суммы группы поступает на D-вход первого D-триггера 9, на С-вход которого подана частота (фиг. 2Ь), равная fT/(m+2). Первый D- триггер 9 предназначен для хранения поступающего на его D-вход кода цифровой суммы группы в течение (гп+ 2) тактов и фор - мирует на своем выходе сигнал (фиг. 2ri) - код цифровой суммы группы, показывающий количество информационных логических единиц в группе из (т+2) бит. Далее код цифровой группы суммы (фиг. 2h) поступает на первый вход второго сумматора 14 по модулю два. на второй вход которого поступает код текущей цифровой суммы, сформированный вторым компаратором 11. Сложив по модулю два сигналы, проходящие на вход, второй сумматор 14 по модулю два формирует сигнал (фиг. 21} инверсии либо отсутствия инверсии сигнала (фиг. 2f), поступающего на первый вход первого сумматора б по модулю два, в зависимости от соотношения кода цифровой суммы группы и кода текущей цифровой суммы. Далее сигнал инверсии поступает на D-вход второго D-триггера 15, на С-вход которого поступает частота В, равная fT/(m+2).

Второй D-триггер 15 предназначен для хранения поступающего на его D-вход сигнала инверсии либо отсутствия такового в течение (т+2) тактов. Затем сигнал инверсий (фиг. 2k) поступает на второй вход первого сумматора 6 по модулю два, на первый вход которого поступает сигнал (фиг. 2f). На выходе первого сумматора 6 по модулю два образуется сигнал (фиг. 2q), представляющий собой инверсный (или прямой) сигнал (фиг. 21) и поступающий на вход интегратора 8, который предназначен для хранения информации о текущей цифровой сумме цифрового сигнала, поступающего на его вход. С выхода интегратора 8 информация о текущей цифровой сумме поступает на первый вход второго компаратора 11, на выходе которого формируется код текущей цифровой суммы (фиг. 2п), показывающий соотношение логических единиц и нулей информационного сигнала. На второй вход второго jtOMnapaTopa 11 с третьего входа устройства

подано постоянное напряжение, соответствующее случаю, когда количество логических единиц и нулей в сигнале, поступающем на вход интегратора 8, равно. С выхода второго компаратора 11 код теку- щей цифровой суммы (фиг. 2п) поступает на второй вход второго сумматора 14 по модулю два.

С выхода первого сумматора 6 по модулю два цифровой сигнал (фиг. 2q) поступает на вход сумматора 13 и на вход линии 12 задержки, на выходе которой образуется сигнал (фиг. 2г), поступающий на первый вход сумматора 13, на выходе которого образуется двухуровневый сигнал (фиг. 2s), об- падающий в два раза меньшей полосой, Двухуровневый сигнал (фиг 2s), проходя через двухполупериодный выпрямитель 10, преобразуется в исходный цифровой сигнал (фиг. 2t), причем информация о телеконтро- ле, служебной связи, синхрогруппе (биты С) остается в таком виде, в каком она была на передающей стороне, а биты Р претерпевают изменения при обработке сигнала. Но это не влияет на передачу основных информа- ционных символов.

Формула изобретения Устройство для передачи бинарной информации, содержащее последовательно соединенные генератор, элемент И, второй вход которого является первым входом устройства, и Т-триггер и последовательно соединенные линию задержки, сумматор, к второму входу которого подключен вход линии задержки, и двухполупериодный выпрямитель, выход которого является выходом устройства, отличающееся тем. что, с целью повышения помехоустойчивости устройства путем подавления низкочастотных составляющих в спектре линейного передаваемого сигнала, введены регистр сдвига, последовательно соединенные цифроанэ- логовый преобразователь, первый компаратор, второй вход которого является вторым входом устройства, и первый D-триггер и последовательно соединенные первый сум матор по модулю два, интегратор, второй компаратор, второй вход которого является третьим входом устройства, второй сумматор по модулю два. к второму входу которого подключен выход первого D-триггера, и второй D-триггер, выход которого подключен к второму входу первого сумматора по модулю два, первый вход которого соединен с соответствующим выходом регистра сдвига, D- и С-входы которого соединены соответственно с выходом Т-триггера и с первым выходом генератора, второй выход которого подключен к С-входам первого и второго D-триггеров, при этом выходы регистра сдвига соединены с входами цифроаналого- вого преобразователя, а выход первого сумматора по модулю два подключен к вхс-jy линии задержки.

| Патент США № 3162724 1961 №31 ВДЛиференко, И.А.ЛуВ В Молькии и И Д.Толкл 178-68. |

Авторы

Даты

1992-08-23—Публикация

1988-01-21—Подача