Изобретение относится к вычислительной технике и может быть использовано для выявления дефектных нако- питепьных регистров при контроле запоминающих устройств на цилиндрических магнитных доменах.

Цель изобретения - повышение достоверности контроля и увеличение быстродействия устройства

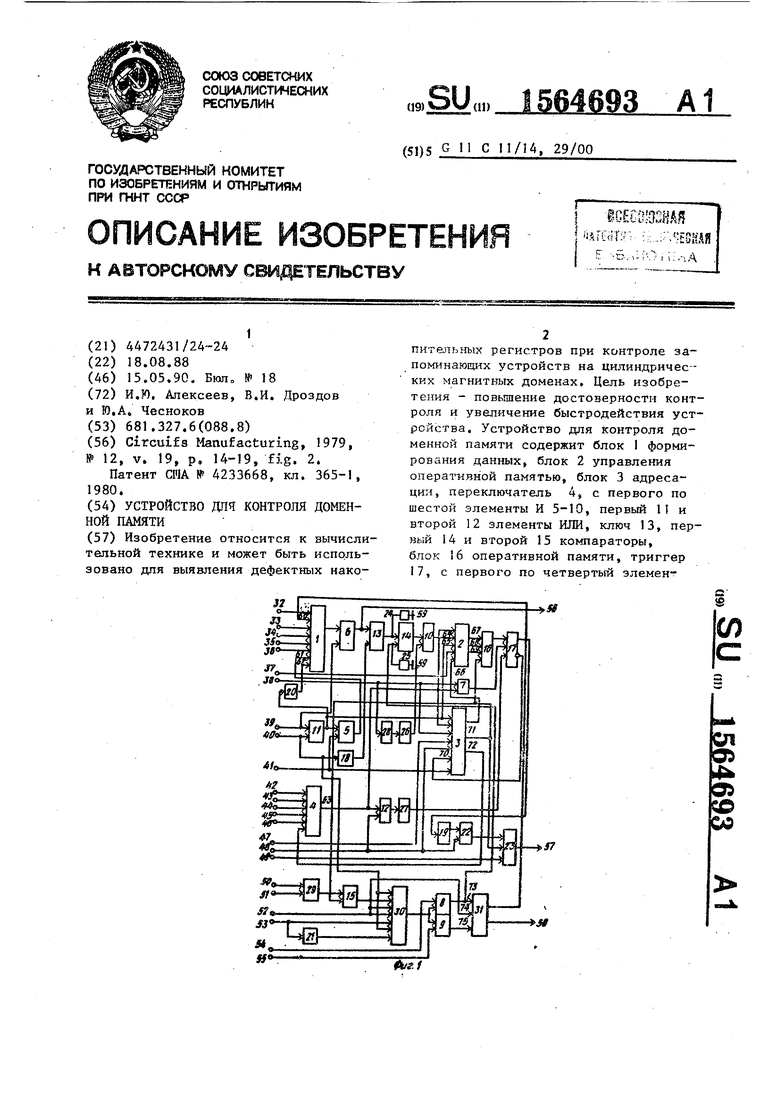

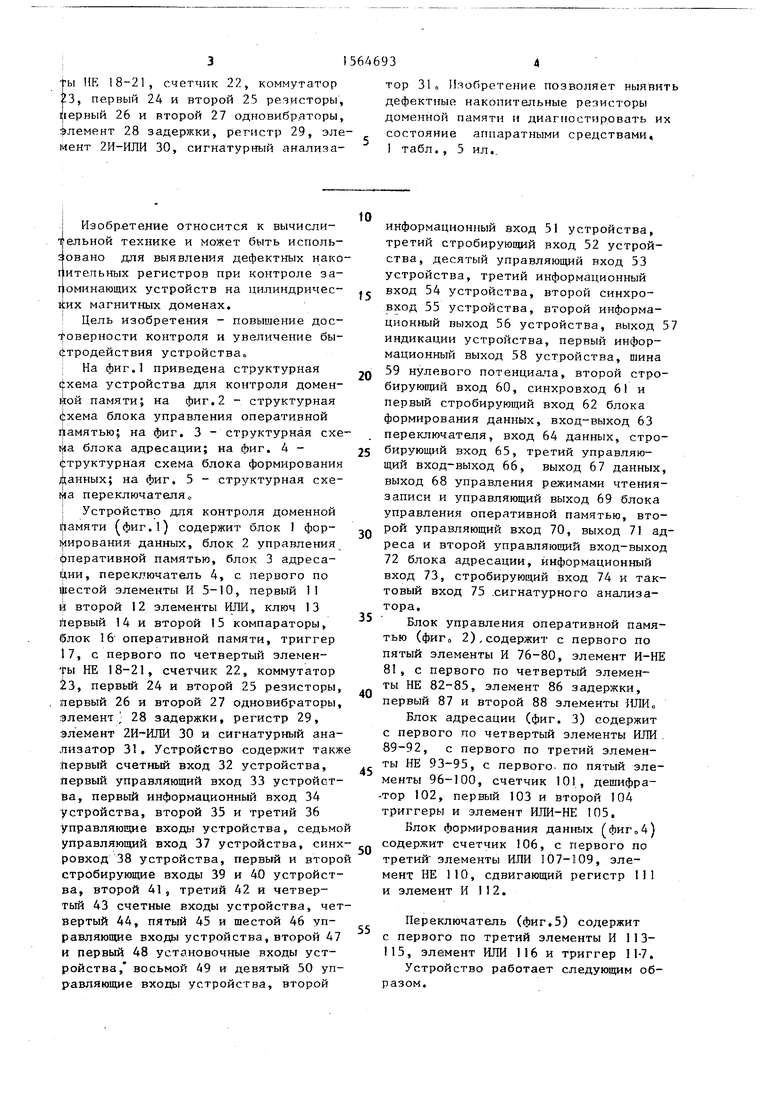

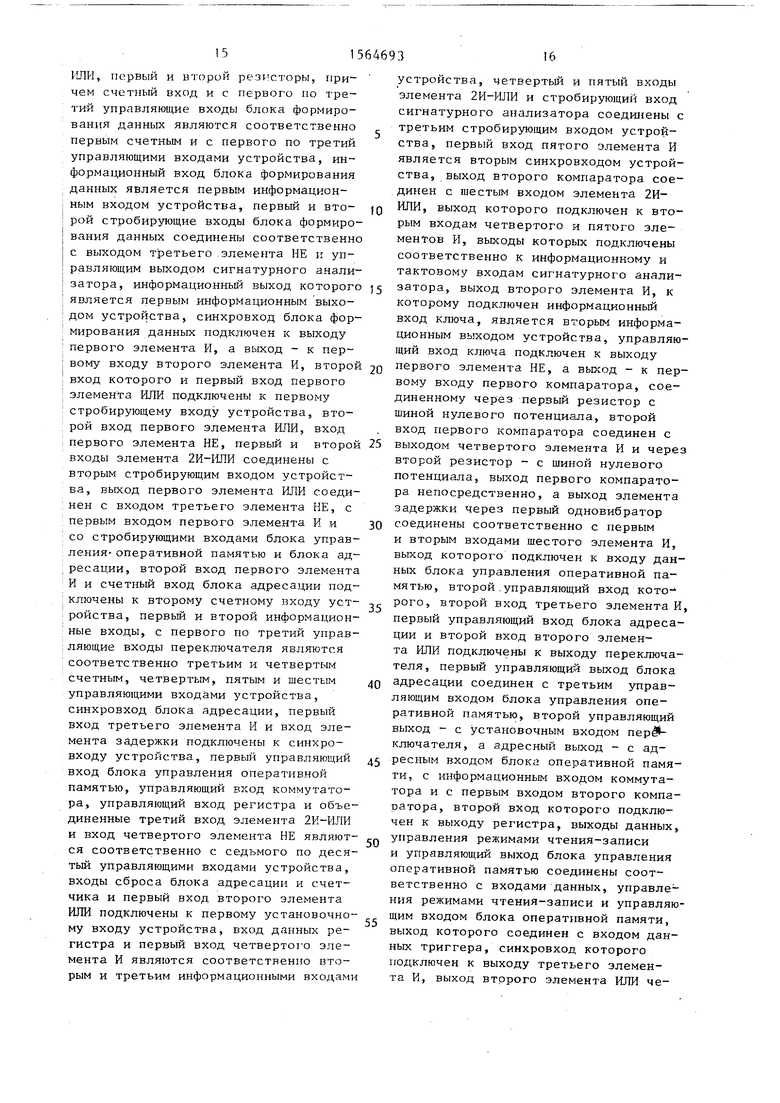

На фиг.1 приведена структурная Схема устройства для контроля доменной памяти; на фиг.2 - структурная фхема блока управления оперативной йамятью; на фиг. 3 - структурная схема блока адресации; на фиг. 4 - фтруктурная схема блока формирования данных; на фиг. 5 - структурная схема переключателя

Устройство для контроля доменной памяти (фиг.1) содержит блок 1 формирования данных, блок 2 управления Оперативной памятью, блок 3 адресации, переключатель 4, с первого по Шестой элементы И 5-10, первый II и второй 12 элементы ИЛИ, ключ 13 первый 14 и второй 15 компараторы, блок 16 оперативной памяти, триггер 17, с первого по четвертый элементы НЕ 18-21, счетчик 22, коммутатор ИЗ, первый 24 и второй 25 резисторы, йервый 26 и второй 27 одновибраторы, Элемент 28 задержки, регистр 29, элемент 2И-ИЛИ 30 и сигнатурный анализатор 31. Устройство содержит такж первый счетный вход 32 устройства, первый управляющий вход 33 устройства, первый информационный вход 34 устройства, второй 35 и третий 36 управляющие входы устройства, седьмо управляющий вход 37 устройства, синх ровход 38 устройства, первый и второ стробирующие входы 39 и 40 устройства, второй 41, третий 42 и четвертый 43 счетные входы устройства, четвертый 44, пятый 45 и шестой 46 управляющие входы устройства, второй 47 И первый 48 установочные входы устройства, восьмой 49 и девятый 50 управляющие входы устройства, второй

5

5

0

5

0

5

0

5

информационный вход 51 устройства, третий стробирующий вход 52 устройства, десятый управляющий вход 53 устройства, третий информационный вход 54 устройства, второй синхро- вход 55 устройства, второй информационный выход 56 устройства, выход 57 индикации устройства, первый информационный выход 58 устройства, шина 59 нулевого потенциала, втооой стробирующий вход 60, синхровход 61 и первый стробирующий вход 62 блока формирования данных, вход-выход 63 переключателя, вход 64 данных, стробирующий вход 65, третий управляющий вход-выход 66, выход 67 данных, выход 68 управления режимами чтения- записи и управляющий выход 69 блока управления оперативной памятью, второй управляющий вход 70, выход 71 адреса и второй управляющий вход-выход 72 блока адресации, информационный вход 73, стробирующий вход 74 и тактовый вход 75 сигнатурного анализатора.

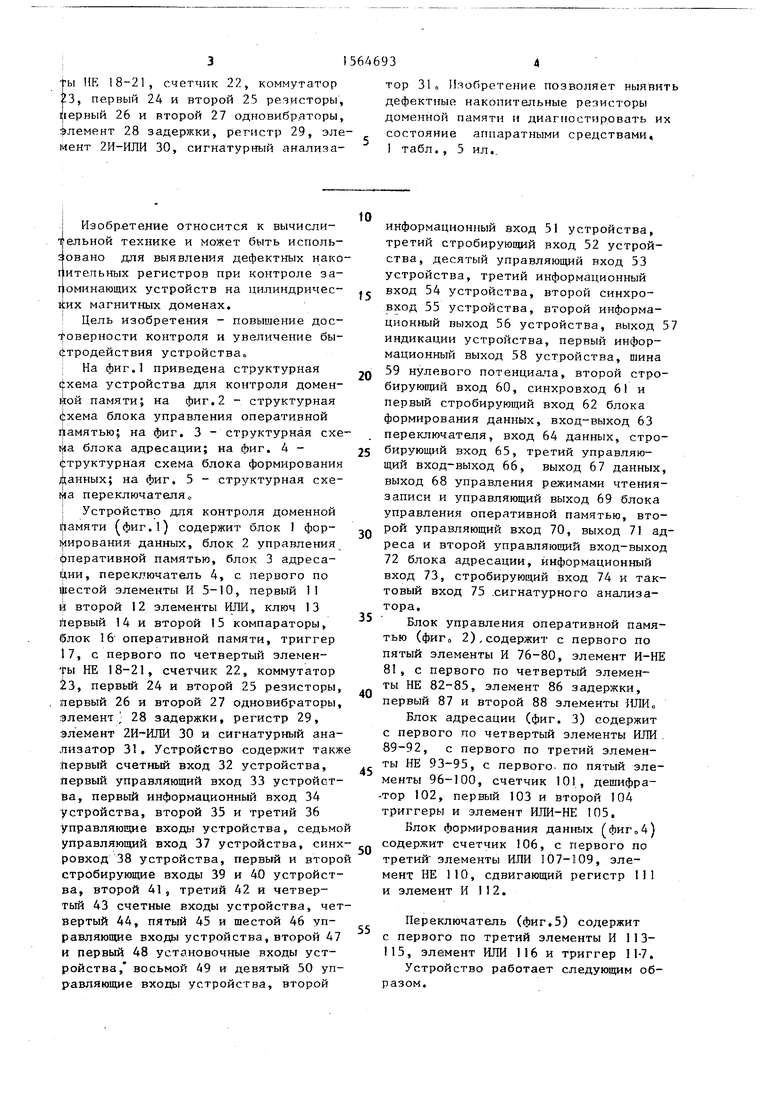

Блок управления оперативной памятью (фиг0 2)«содержит с первого по пятый элементы И 76-80, элемент И-НЕ 81, с первого по четвертый элементы НЕ 82-85, элемент 86 задержки, первый 87 и второй 88 элементы ИЛИ

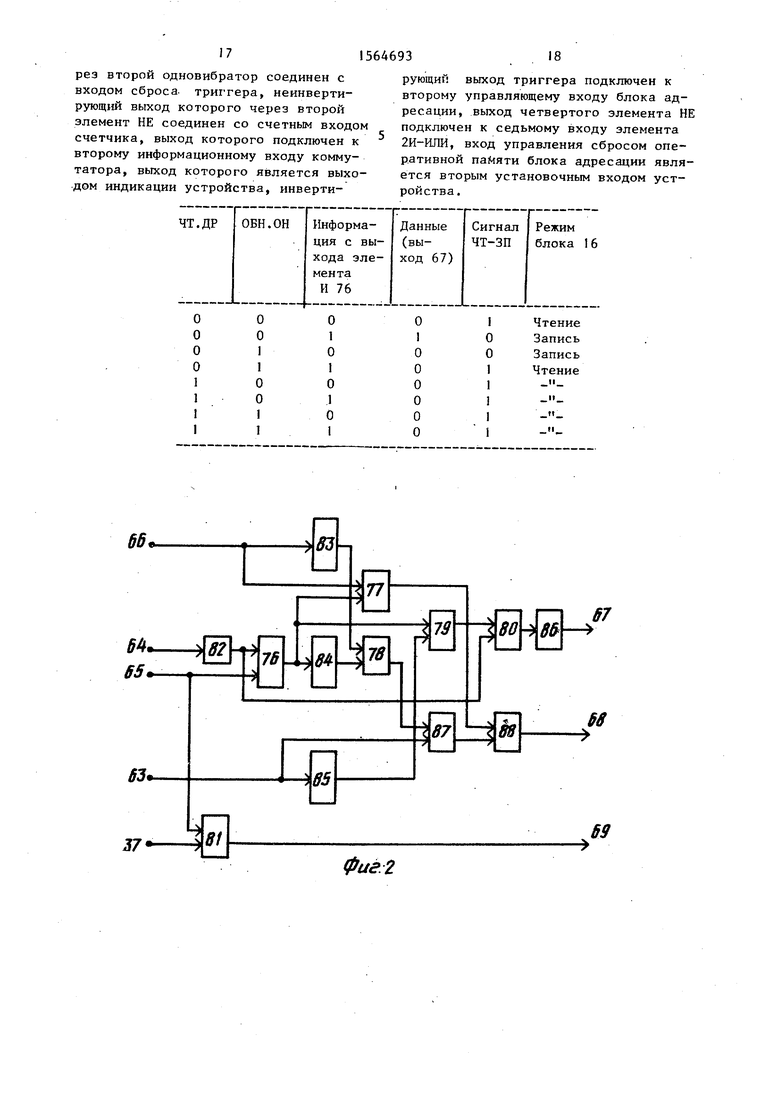

Блок адресации (фиг. 3) содержит с первого по четвертый элементы ИЛИ 89-92, с первого по третий элементы НЕ 93-95, с первого по пятый элементы 96-100, счетчик 101, дешифра- -тор 102, первый 103 и второй 104 триггеры и элемент ИЛИ-НЕ 105.

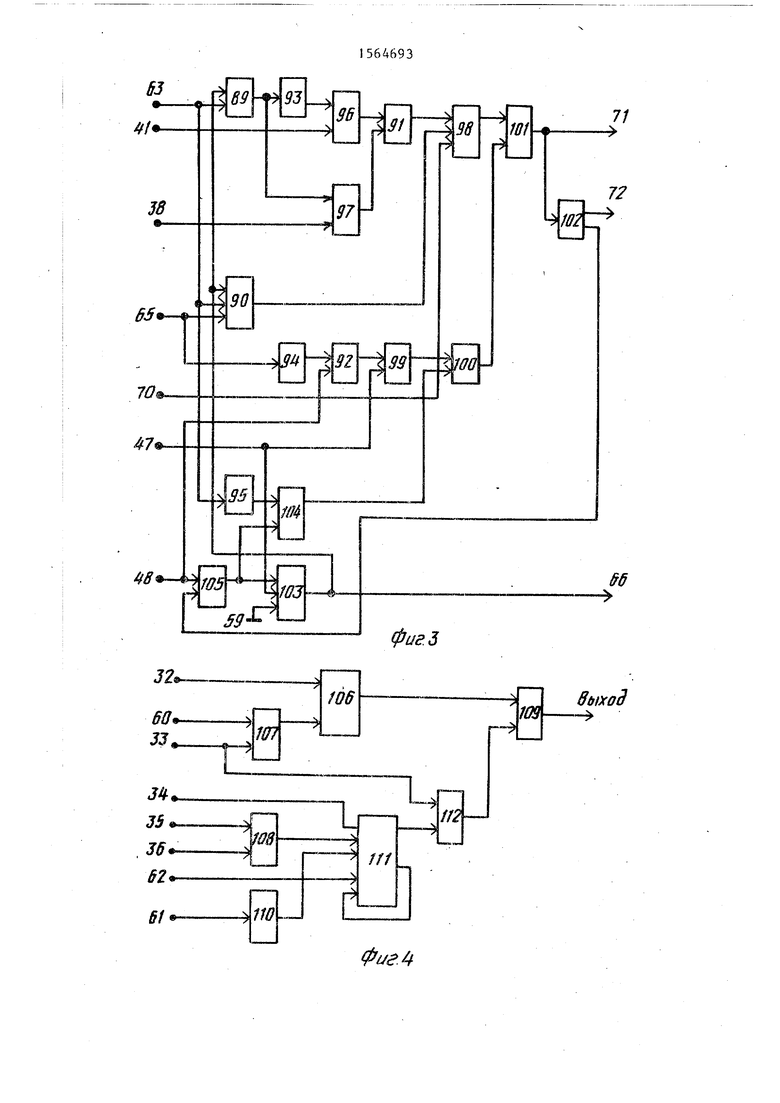

Блок формирования данных (фиг„4) содержит счетчик 106, с первого по третий элементы ИЛИ 107-109, элемент НЕ ПО, сдвигающий регистр 111 и элемент И 112.

Переключатель (фиг.5) содержит с первого по третий элементы И 113- 115, элемент ИЛИ 116 и триггер 11-7.

Устройство работает следующим образом.

51

Сигналом с входа 33 выбирается режим работы блока 1 формирования данных Лог. 1 на входе 33 соответствует режиму Байт, когда на выходе блока 1 появляется последовательност повторяющихся байтов данных. Лог.О на входе 33 соответствует режиму , когда на выходе блока 1 появляется последовательность, состоящая из чередующихся серий единиц и нулейо В режиме Байт 1 с входа 3 через элемент ИЛИ 107 сбрасывает и блокирует счетчик 106 и открывает по первому входу элемент И 112, на второй вход которого поступает информация с выхода регистра 111. Последний загружается оператором с входа 3 блока формирования данных перед началом работы по сигналу ЗП.Д с входа 35, В момент поступления О на вход 62 регистр 111 переключается в режим сдвига и синхронно с сигналами частоты fyf с синхровхода 61 блока формирования данных на выходе регистра 111 появляется записанная в него информация, которая через элемент И 112 и элемент ИЛИ 109 поступает на выход блока 1 формирования данных. Поскольку информация с выхода регистра 111 поступает на его вхо то на выходе блока 1 имеется последовательность одинаковых байтов, первоначально введенных в регистр 111. Длина последовательности определяется длительностью строба на входе 62. Этим стробом производится переключение регистра 111 в режим приема информации по входу параллельного ввода. Это происходит во время работы устройства по сигналам РЕГЕ- НЕР.Д или ЗП.Д путем подачи 1 на входы 36 или 35 соответственно,

В режиме Тест О с входа 33 разрешает работу счетчика 106, который выдает последовательность единиц к нулей на выход блока 1 форми-. рования данных. Пересчет в счетчике 106 ведется по его счетному входу импульсами, поступающими на вход 32 блока 1, информация снимается с выхода переполнения счетчика 106. Вход 60 выполняет ту же функцию, что и вход 33 блока 1 формирования данных. Функции блока 2 управления оперативной памятью (фиг.2) состоят в управлении блоком 16 оперативной памяти по выходам 67 (данные), 68 чтение- запись), 69 (управляющий выход)

0

Активный уровень сигнала по выходу 69 - О. При этом на выходе элемента И-НЕ 81 О присутствует в том- случае, когда схема не запущена (сигнал Пуск на входе 37 соответствует 1, а сигнал на входе 65 - О), или когда схема запущена и идет один из режимов: ввод или вывод, а сигнал Пуск имеет значение О. На вход 66 поступает сигнал обнуления блока 16 оперативной памяти (ОБНоОН), по которому на выходах 67 и 68 должны появиться сигналы 00,

5 которые обеспечат запись О в блок 16 оперативной памяти (фиг) Данные поступают на вход 64 блока 2 в инвертированном виде, восстанавливаются элементом НЕ 82 и стробируются

0 сигналом по входу 65 на элементе И 76, Запись данных в блок 16 обеспечивается блоком 2 управления и в случае появления | на входе 64 при значении сигнала на входе 65 - I

5 При этом на выходах 68 и 69 должны быть установлены сигналы: 1 (данные) и О (чтение-запись). Блок 2 управления должен обеспечить чтение содержимого блока 16 оперативной па0 мяти при поступлении на ЕХОД 63 1 (сигнала Чтение дефектных регистров (ЧТ ДР)).

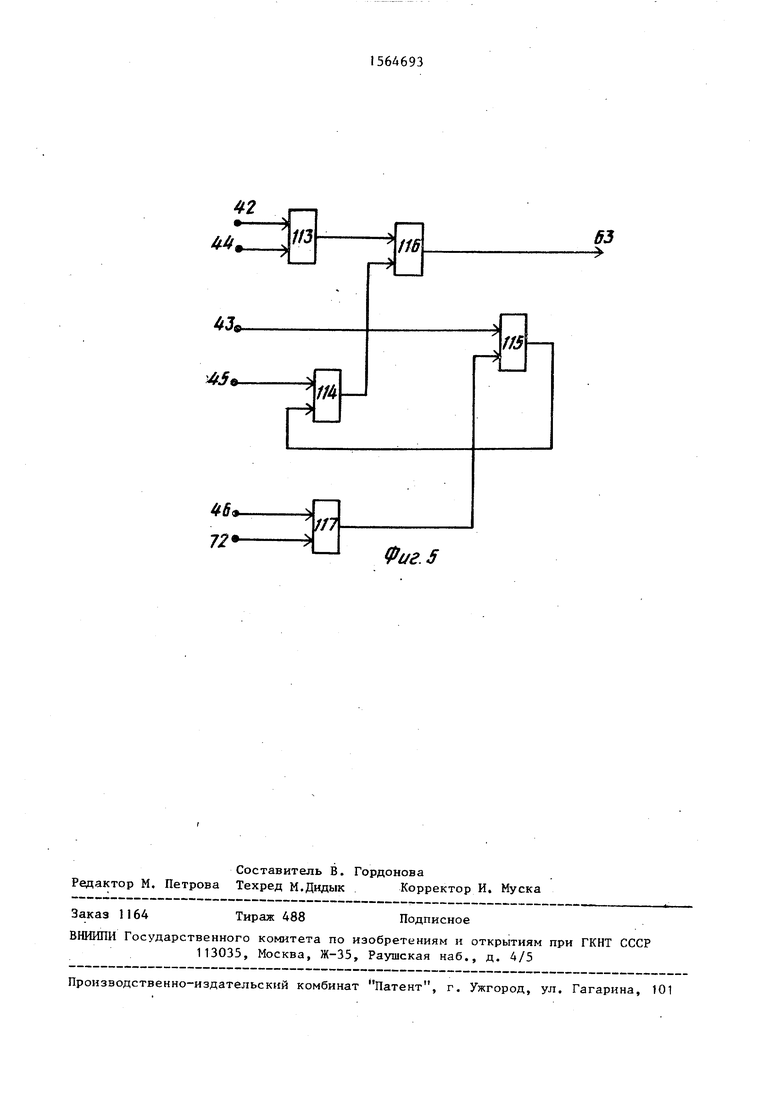

Таблица истинности блока 2 управления имеет следующий вид.

Блок 3 адресации (фиг.З) работает следующим образом.

Вначале производится установка в исходное состояние. По сигналу 1 О (Сброс), поступающему на вход 48, О с выхода элемента ИЛИ-НЕ 105 производит сброс триггеров 103 и 104 в нулевое состояние.

Сброс счетчика 101 производится поступающей на его вход уста5

0

5

новки с, выхода элемента И 100, на один вход которого приходит 1 с инвертирующего выхода триггера 104, который находится в нулевом состоянии. 1 на другом входе элемента И 100 образуется следующим образом. На входе 65 - О при отсутствии стробов ввода и вывода. Этот сигнал инвертируется элементом НЕ 94, проходит через элемент ИЛИ 92 и через элемент И 99, на другом входе которого I с входа 47 при отсутствии сигнала сброса оперативного накопителя (СВР.ОН) на этом входе, и подается на другой

10

15

вход элемента И 100„ В результате сметчик 101 не меняет своего состояния. По команде СВР.ОН на вход 47 поступает О, который взводит триггер 103 и закрывает элемент И 99, что приводит к снятию сигнала сброса со сметчика 101, счетчик готов к пересчету 1 ct выхода триггера 103 поступает на выход 66 и проходит через элемент ИЛИ 89, что разрешает прохождение синхросигнала с входа 38 ч€:рез элементы И 97 и (ПИ 91 на вход элемента И 98, на других входах которого имеются 1 с выхода элемента ИЛИ 90 и с входа 70. Элемент И 98 открывается и на счетном входе счетчи- кЈ: 101 появляется синхросигнале С выхода счетчика 101 на выход 71 и на дешифратора 102 поступает последовательность кодов адресов накопителя блока 16,

После опроса последнего адреса бгока 16 срабатывает дешифратор 102, НЕ выходе которого появляется сигнал t, передним фронтом которого триг- ЮЗ устанавливается в нулевое состояние (в случае, если к этому вре- снят сигнал О команды СВР„ОН с входа 70). Сброс триггера 103 при- к снятию разрешения на поступ- синхроимпульсов на счетный вход сметчика 101 (по цепям элемента ИЛИ 8$ и элемента И 97). Счетчик 101 прекращает изменять свои состояния. Сня- О с входа 47 сопровождается по- я лением на нем 1, которая пропус- кфет 1 на вход сброса счетчика 101 с выхода элемента НЕ 94 (на его вхо- дф О с входа 65) через элементы 40 ИЛИ 92, И 99 и 100 (на другом входе элемента И 100 - 1 с выхода триггера 104, находящегося в нулевом состоянии). Счетчик 101 сбрасывается, В рабочем режиме на входе 41 15646938

да 70. После прихода положительного импульса на вход 65 он через элемент ИЛИ 90 поступает на третий вход элемента И 98, на выходе которого появляется серия импульсов частоты fn, которая поступает на счетный вход счетчика 101.

1 с входа 47 поступает на один вход элемента И 99, на другом входе которого удерживается 1 с выхода элемента ИЛИ 92 до тех пор, пока на входе 65 - О. 1 с выхода элемента И 99 проходит через элемент И 100 на вход сброса счетчика 101. Таким образом, пока на входе 65 - О, счетчик 101 удерживается в состоянии сброса. После прихода 1 на вход 65 на входе сброса счетчика 101 появ- 0,

20

25

а на счетном входе - сеп

Счетчик

ляется

рия импульсов частоты

начинает пересчет.

После снятия 1 с входа 65 на выходе элемента И 100 устанавливает I1

которая сбрасывает счет30

35

45

ся

чик 101.

В режиме чтения дефектов (ЧТ.Д) на входе 63 - 1, на входе 38 - серия синхроимпульсов, на входе 65 - О, на входе 70 - 1 до появления дефекта и О - при дефекте, на входах 47 и 48 - 1 до О соответственно. 1 с входа 63 через элемент ИЛИ 89 проходит на один вход элемента И 97, синхроимпульсы с входа 38 через элементы И 97 и ИЛИ 91 поступают на вход элемента И 98, на втором входе которого - 1 с выхода элемента ИЛИ 90 (на его входе - 1 с входа 65), на третьем входе элемента И 98 - 1 с входа 700 С выхода открытого элемента И 98 синхроимпульсы поступают на счетный вход сче.тчи- ка 101.

1 с входа 63 через элемент НЕ 95 устанавливает триггер 104 в единич- ное состояние, что приводит к появлению О на его инвертирующем выходе, закрытию элемента И 100 и снятию 1 команды Сброс с входа счетчика 101, Счетчик начинает перебор адресов, который продолжается до появления О на входе 70. При появлении 1 на входе 70 счетчик возобновляет перебор адресов накопителя блока 16. Окончание перебора адресов происходит по сбросу счетчика 101 при срабатывании дешифратора 102, который через элемент ИЛИ-НЕ 105 сбрасывает триггер

частота поля fп, на входе 65 - последовательность импульсов положительной полярности, на входе 70 - 1, на входах 63 и 48 - О, на входе 47 - |, триггеры 103 и 104 - в нулевом состоянии. Импульсы fn поступают на один вход элемента И 96, на другом входе которого - 1 с выхода элемента НЕ 93 (на его входе - О , так как на входе 63 - О),

С выхода элемента И 96 импульсы частоты ff, через элемент ИЛИ 91 поступают на один вход элемента И 98, на другом входе которого - 1 с вхо0

1 с входа 47 поступает на один вход элемента И 99, на другом входе которого удерживается 1 с выхода элемента ИЛИ 92 до тех пор, пока на входе 65 - О. 1 с выхода элемента И 99 проходит через элемент И 100 на вход сброса счетчика 101. Таким образом, пока на входе 65 - О, счетчик 101 удерживается в состоянии сброса. После прихода 1 на вход 65 на входе сброса счетчика 101 появ- 0,

0

а на счетном входе - сеп

Счетчик

ляется

рия импульсов частоты

начинает пересчет.

После снятия 1 с входа 65 на выходе элемента И 100 устанавливает0

5

I1

которая сбрасывает счет0

5

5

0

5

ся

чик 101.

В режиме чтения дефектов (ЧТ.Д) на входе 63 - 1, на входе 38 - серия синхроимпульсов, на входе 65 - О, на входе 70 - 1 до появления дефекта и О - при дефекте, на входах 47 и 48 - 1 до О соответственно. 1 с входа 63 через элемент ИЛИ 89 проходит на один вход элемента И 97, синхроимпульсы с входа 38 через элементы И 97 и ИЛИ 91 поступают на вход элемента И 98, на втором входе которого - 1 с выхода элемента ИЛИ 90 (на его входе - 1 с входа 65), на третьем входе элемента И 98 - 1 с входа 700 С выхода открытого элемента И 98 синхроимпульсы поступают на счетный вход сче.тчи- ка 101.

1 с входа 63 через элемент НЕ 95 устанавливает триггер 104 в единич- ное состояние, что приводит к появлению О на его инвертирующем выходе, закрытию элемента И 100 и снятию 1 команды Сброс с входа счетчика 101, Счетчик начинает перебор адресов, который продолжается до появления О на входе 70. При появлении 1 на входе 70 счетчик возобновляет перебор адресов накопителя блока 16. Окончание перебора адресов происходит по сбросу счетчика 101 при срабатывании дешифратора 102, который через элемент ИЛИ-НЕ 105 сбрасывает триггер

91

104. Сигнал 1 с выхода триггера 10 обеспечивает сброс счетчика 101„ Таким образом, в режиме ЧТ.ДР блок 3 адресации циклически формирует коды адресов накопителя блока 16, осуществляя останов при поступлении на вход 70 1 сигнала Фл.Дф (Флаг дефекта) . При этом на выходе 72 циклически появляется сигнал СВР.310.

Переключатель 4 (фиг.5) работает следующим образом

В исходном состоянии на его входах 42 и 43 - положительные импульсы низкой (1,5 Гц) и высокой (1,5 кГц) частот соответственно. На входах 44 и 45 - О и 1 соответственно, на входе 46 - Г1,на входе 72 - 1, триггер 117 - в нулевом состоянии, при этом на выходе 63 - О,

При выполнении режима ручного опроса на входах 44, 45 и 46 - комбинация сигналов 1, О и 1 соответственно. При этом на выходе 63 появляется импульсный сигнал частоты 1,5 Гц. При выполнении режима ускореного опроса дефектных регистров (ДР) на входах 44, 45 и 46 - комбинация логических сигналов 010, При этом срабатывает триггер 17 и сигнал частоты 1,5 кГц появляется на выходе 63, пройдя элементы И 115 и 114 и элемент ИЛИ 116. После прихода отрицательного импульса на вход 72 триггер 117 сбрасывается и на выходе 63 устанавливается О.

Перед началом работы устройства производится установка блоков устройства в исходное состояние подачей 1 на вход 48. При этом происходит сброс счетчика 22. 1 через элемент ИЛИ 12 проходит на вход одновибрато ра 27, на выходе которого появляется отрицательный импульс, устанавливающий триггер 17 в нулевое состояние. Подается 1 на вход 48 блока 3

адресации, в котором происходит сброс триггеров 103 и 104 в нулевое состояние (фиг.З).

Затем производят сброс блока 16 оперативной памяти подачей и снятием 1 (сигнала СВР.ОН) на вход 47, откуда 1 поступает на вход блока 3 адресации, который производит перебор кодов адреса оперативного накопителя блока 16 на выходе 71, выдаются сигналы СВР.310 и ОВН.ОН с выходов 72 и 66, Эти сигналы соответственно производят установку триггера 11 7

693

10

переключателя 4 и запуск в режим СВР о ОН блока 2, который устанавливает О на выходе 67 данных и О - на выходе 68 (команда Запись), на выходе 69 блока 2 управления - О (при наличии О на его входе 65 и 1 на его входе 37). Таким образом, на входе данных накопителя блока 16 - О, включен режим Запись, накопитель выбран (О - на выходе 69 блока 2), производится перебор адресов, происходит очистка (запись нулевых данных) в блок 16 оперативной памяти.

Затем производится выбор режима работы блока 1 формирования данных„ 1 на входе 33 соответствует режиму

0

5

0

5

0

5

0

5

Байт , когда производится ввод последовательных друг за другом по длине страницы одинаковых байтов данных, поступающих на вход ЗА данных 1 на входе 33 соответствует режиму Тест, когда с выхода блока 1 формирования данных подается циклическая последовательность из восьми О и восьми 1.

Для работы в режиме Байт необходимо занести байт в блок 1, для чего кратковременно подают на вход 35 1, которая стробирует занесение информации с входа 34.

При проведении любого из режимов работы устройства на входе 32 присутствует импульсный сигнал Конец цикла (КЦ), частота которого определяет период подачи сигналов в тестовой последовательности, на входе 34 постоянно присутствует байт вводимой информации, на вход 36 приходит импульсный сигнал регенерации данных (Реген.Д), на входы 38, 41-43 поступают последовательности импульсов синхронизации частоты f, 1,5 Гц,

1,5 кГц соответственно, на входах 44 и 45 -команда отсутствия опроса дефектных регистров (код Ol) , на входе 46 - 1, на входе 47 - 1 (нет сброса ОН), на входе 48 - О (нет сброса), на входе 49 - О (сигнал ДР), на входе 53 - О (индикация сигнатуры), на входе 55 - последовательность импульсов синхронизации сигнатурного анализатора 31. Сигналы на входах 50, 51, 53 и 54 определяют режим индикации сигнатурного анализатора 31 .

Режим ввода информации начинается с подачи сигнала Пуск. При этом

на входе 37 появляется О, на вхо- $е 46 удерживается 1, а на входе JJ9 - последовательность положитель- Йых импульсов, на входе 40 - О, на входе 52 появляется последовательность импульсов управления сигнатурным анализатором, а на выходе 60 сиг- йатурного анализатора 31 - инвертированная последовательность импульсов . управления блоком формирования Данных.

1 В зависимости от выбранного по иходу 33 режима блок 1 начинает выдавать информационную последовательность, которая проходит через элемент 6 на выход 56 устройства для ввода Йе в объект контроля (доменную память) .

Поскольку на входе 40 в режиме в|вода - О, то 1 с выхода элемен- ija НЕ 18 закрывает ключ 13 (его выход Јi третьем состоянии) , на одном из входов компаратора 14 - О (через ре- истор 24). В этом режиме на вход

4 подан О (информация из объекта

i}e выводится), поэтому на другом вхо- Де компаратора 14 также О. Ключ 13 реализован на сумматоре по модулю ва, т.е. при совпадении сигналов На его входах на выходе компаратора 14 - О. На входе 64 блока 2 - О с выхода элемента И 10, на выходах 66, 37 и 63 блока 2 - также О. Б этом случае блок 2 формирует я|а своих выходах команду управления режимом чтения накопителя блока 16 (блок 16 предварительно обнулен). По- Скольку в этом случае на входе данных Щлока 16 - О, а на входе синхронизации триггера 17 также О с выхода Элемента И 7, то с инверсного выхода триггера 17 на вход 70 блока 3 адресации поступает О, на вход 38 Приходит синхроимпульс, а на вход 65 - импульсный сигнал строба ввода. При этом на его выходе появляется последовательность адресов накопителя блока 16. Таким образом, в режиме идет чтение предварительно об- Иуленного накопителя блока 16.

В режиме Вывод на входы устройства приходят те же сигналы, что и цри вводе, отличие лишь в том, что на В1ходе 39 - О 1 (строб ввода отсутствует) , а на входе 40 - последовательность положительных импульсов строба вывода, на входе 54 - информационная последовательность, снимаемая с до156469312

менной памяти. При выводе устройство автоматически сравнивает эту информацию с введенной и результаты несравнения заносит в виде единичных флагов дефекта в ячейки накопителя блока 16 по адресу, определяющему номер дефектного бита в информационной последовательности.

Вывод информации на вход 54 устройства осуществляется в стробе вывода, т.е. тогда, когда на входе 40 - 1. При этом бит информации с входа 54 проходит через открытый элемент И 8 на вход компаратора 14, на другом входе которого через ключ 13, который открыт, - О с выхода элемента НЕ 18 (в стробе вывода ка входе 40 - 1), появляется последовательность с выхода блока 1 формирования данных, введенная ранее в объект и являющаяся эталонной.

При несравнении выводимого бита с соответствующим эталонным на выходе компаратора 14 появляется 1, которая проходит на вход 64 блока 2. При этом на его выходах устанавливается набор команд для осуществления

15

20

25

30

35

40

записи 1 (флага дефекта) в накопитель блока 16 по соответствующему адресу.

По окончании режима Вывод на входе 40 устанавливается О, закрывающий через элемент НЕ 18 ключ 13, на входе 54 появляется О (нет инфор- мации), на входе 37 появляется 1 (снимается команда Пуск), а на входе 46 - отрицательный импульс сигнала Стоп. При этом переключатель 4 пропускает первый импульс с входа 43 на выход 63 переключателя 4 и далее на соответствующие входы блока 2 и блока 3, а также на вход элемента И 7. Блок 2 устанавливает режим с опроса накопителя блока 6, а блок 3 осуществляет перебор его адресов. Через открывшийся элемент И 7 на синх- ровходе триггера 17 появляются синхроимпульсы с входа 38, которые осуществляют взведение триггера 17 в единичное состояние по первому встретившемуся при опросе накопителя блока 16 флагу дефекта. На прямом выходе триггера 17 появляется единичный сигнал, который через элемент НЕ 19 просчитывается счетчиком 22. Нулевой сигнал с инвертирующего выхода триггера 17 останавливает блок 3 адресации и прекращает тем самым опрос накопи50

55

0

5

0

записи 1 (флага дефекта) в накопитель блока 16 по соответствующему адресу.

По окончании режима Вывод на входе 40 устанавливается О, закрывающий через элемент НЕ 18 ключ 13, на входе 54 появляется О (нет инфор- мации), на входе 37 появляется 1 (снимается команда Пуск), а на входе 46 - отрицательный импульс сигнала Стоп. При этом переключатель 4 пропускает первый импульс с входа 43 на выход 63 переключателя 4 и далее на соответствующие входы блока 2 и блока 3, а также на вход элемента И 7. Блок 2 устанавливает режим с опроса накопителя блока 6, а блок 3 осуществляет перебор его адресов. Через открывшийся элемент И 7 на синх- ровходе триггера 17 появляются синхроимпульсы с входа 38, которые осуществляют взведение триггера 17 в единичное состояние по первому встретившемуся при опросе накопителя блока 16 флагу дефекта. На прямом выходе триггера 17 появляется единичный сигнал, который через элемент НЕ 19 просчитывается счетчиком 22. Нулевой сигнал с инвертирующего выхода триггера 17 останавливает блок 3 адресации и прекращает тем самым опрос накопи0

5

13

теля блока 16. Следующий импульс с выхода 63 переключателя 4 производит сброс триггера 17 через элемент ИЛИ и одновибратор 27, происходит запуск блока 3.по снятию О с его входа 70 и останов по появлении следующего флага дефекта в накопителе блока 16

Таким образом, по сигналу Стоп происходит автоматический опрос содержимого накопителя блока 16, а счетчик 22 накапливает количество дефектов в выводимой информации, которое через открытый коммутатор 23 передается на выход 57 устройства для индикации.

Лля выявления адресов флагов дефектов производится ручной опрос содержимого накопителя блока 16. При этом на вход 49 кратковременно подается 1, переключающая вход коммутатора 23 на выход блока 3. При каждом опросе на входах 44 и 45 переключателя 4 устанавливается код 10 и на его выходе 63 появляется 1, которая производит опрос накопителя блока 16 с пониженной частотой 1,5 Г При опросе происходит останов перебора адресов с блока 3 и появление кода адреса дефекта на выходе 57. При непрерывном ручном опросе коды адреса сменяются на выходе 57 с час- тотрй 1,5 Гц. При прерывистом опросе можно осуществить ручной останов в нужный момент.

В устройстве использован сигнатурный анализатор 31, который позволяет получить на выходе 58 сигнатуру (свертку) выводимой информационной последовательности. Выходная информационная последовательность доменной памяти состоит из периодически повторяющихся фрагментов, характеризующих ее состояние. Каждый бит фрагмента характеризует состояние определенного регистра доменной памяти в определенный момент времени. Устройство может обеспечить два режима получения сигнатуры - полная сигнатура (характеристика объекта) и сигнатура регистра объекта.

В режиме получения полной сигнатуры на входе 52 - последовательность импульсов окна анализатора 31 (в окне анализатор производит свертку),

на входе 53 - О, на входах 54 и 55 информационная и синхронизирующая последовательности. с входа 53 инвертируется элементом НЕ 21 и

0

5

0

5

4693

0

5

0

14

через элемент 2И-ИЛИ 30 открывает элементы И 8 и 9, через которые на соответствующие входы анализатора 31 поступают сигналы с входов 54 и 55 устройства. Сигнатура с выхода анализатора 31 поступает на выход 58 устройства.

В режиме получения сигнатуры регистра объекта на входе 50 устанавливается код регистра, который заносится в регистр 29 по команде с входа 54. На входе 53 - 1, на входах 52, 54, 55 - соответствующие последовательности. При работе в режиме вывода компаратор 15 при совпадении номера регистра, введенного в регистр 29, и адреса с выхода блока 3 выдает положительный импульс, который открывает элемент 2И-ИЛИ 30, отпирающий элементы И 8 и 9. На входах 73 и 75 анализатора 31 появляются информационные импульсы и импульсы синхронизации только в моменты времени, соответствующие появлению информации из определенного регистра объекта. При этом на выходе 58 устройства получается сигнатура регистра доменной памяти. Использование сигнатурного анализатора 31 и логики выбора регистра позволяет диагностировать состояние регистра хранения накопителя на ЦМД по его сигнатуре, что повышает полноту и достоверность контроля.

Предлагаемое изобретение позволяет решить задачу выявления и локализации дефектных накопительных регистров доменной памяти аппаратными средствами, что повышает быстродействие устройства.

Формула изобретения

Устройство для контроля доменной памяти, содержащее блок формирования данных, первый компаратор, блок оперативной памяти, элементы НЕ с первого по четвертый и ключ, отличающееся тем, что, с целью повышения достоверности контроля и увеличения быстродействия устройства, в него введены второй компаратор, элемент 2И-ИЛИ, регистр, элементы И с первого по шестой, сигнатурный анализатор, коммутатор, счетчик, триггер, элемент задержки, переключатель, блок управления оперативной памятью, блок адресации, первый и второй одно- вибраторы, первый и второй элементы

ИЛИ, первый и второй резисторы, причем счетный вход и с первого по третий управляющие входы блока формирования данных являются соответственно первым счетным и с первого по третий управляющими входами устройства, информационный вход блока формирования данных является первым информационным входом устройства, первый и вто- рой стробирующие входы блока формирования данных соединены соответственно с выходом третьего элемента НЕ и управляющим выходом сигнатурного анализатора, информационный выход которого является первым информационным выходом устройства, синхровход блока формирования данных подключен к выходу первого элемента И, а выход - к первому входу второго элемента И, второй вход которого и первый вход первого элемента ИЛИ подключены к первому стробирующему входу устройства, второй вход первого элемента ИЛИ, вход первого элемента НЕ, первый и второй входы элемента 2И-ИЛИ соединены с вторым стробирующим входом устройства, выход первого элемента ИЛИ соединен с входом третьего элемента НЕ, с первым входом первого элемента И и со стробирующими входами блока управления- оперативной памятью и блока адресации, второй вход первого элемента И и счетный вход блока адресации подключены к второму счетному входу уст- ройства, первый и второй информационные вхоцы, с первого по третий управляющие входы переключателя являются соответственно третьим и четвертым счетным, четвертым, пятым и шестым управляющими входами устройства, синхровход блока адресации, первый вход третьего элемента И и вход элемента задержки подключены к синхро- входу устройства, первый управляющий вход блока управления оперативной памятью, управляющий вход коммутатора, управляющий вход регистра и объединенные третий вход элемента 2К-ИЛИ и вход четвертого элемента НЕ являют- ся соответственно с седьмого по десятый управляющими входами устройства, входы сброса блока адресации и счетчика и первый вход второго элемента ИЛИ подключены к первому установочному входу устройства, вход данных регистра и первый вход четвертого элемента И являются соответственно вторым и третьим информационными входами

5 0 5 0 с 0 -Q

5

устройства, четвертый и пятый входы элемента 2И-Ш1И и стробирующий вход сигнатурного анализатора соединены с третьим стробирующим входом устройства, первый вход пятого элемента И является вторым синхровходом устройства, выход второго компаратора соединен с шестым входом элемента 2И- ИЛИ, выход которого подключен к вторым входам четвертого и пятого элементов И, выходы которых подключены соответственно к информационному и тактовому входам сигнатурного анализатора, выход второго элемента И, к которому подключен информационный вход ключа, является вторым информационным выходом устройства, управляющий вход ключа подключен к выходу первого элемента НЕ, а выход - к первому входу первого компаратора, соединенному через первый резистор с шиной нулевого потенциала, второй вход первого компаратора соединен с выходом четвертого элемента И и через второй резистор - с шиной нулевого потенциала, выход первого компаратора непосредственно, а выход элемента задержки через первый одновибратор соединены соответственно с первым и вторым входами шестого элемента И, выход которого подключен к входу данных блока управления оперативной памятью, второй управляющий вход которого, второй вход третьего элемента И, первый управляющий вход блока адресации и второй вход второго элемента ИЛИ подключены к выходу переключателя, первый управляющий выход блока адресации соединен с третьим управляющим входом блока управления оперативной памятью, второй управляющий выход - с установочным входом ключателя, а адресный выход - с адресным входом блока оперативной памяти, с информационным входом коммутатора и с первым входом второго компа- патора, второй вход которого подключен к выходу регистра, выходы данных, управления режимами чтения-записи и управляющий выход блока управления оперативной памятью соединены соответственно с входами данных, управления режимами чтения-записи и управляющим входом блока оперативной памяти, выход которого соединен с входом данных триггера, синхровход которого подключен к выходу третьего элемента И, выход второго элемента ИЛИ че1715

рез второй одновибратор соединен с входом сброса триггера, неинвертирующий выход которого через второй элемент НЕ соединен со счетным входом счетчика, выход которого подключен к второму информационному входу коммутатора, выход которого является выходом индикации устройства, инверти

18

рующий выход триггера подключен к второму управляющему входу блока адресации, выход четвертого элемента НЕ подключен к седьмому входу элемента 2И-ИЛИ, вход управления сбросом оперативной памяти блока адресации является вторым установочным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645959A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Изобретение относится к вычислительной технике и может быть использовано для выявления дефектных накопительных регистров при контроле запоминающих устройств на цилиндрических магнитных доменах. Цель изобретения - повышение достоверности контроля и увеличение быстродействия устройства. Устройство для контроля доменной памяти содержит блок 1 формирования данных, блок 2 управления оперативной памятью, блок 3 адресации, переключатель 4, с первого по шестой элементы И 5-10, первый 11 и второй элементы ИЛИ 12, ключ 13, первый 14 и второй 15 компараторы, блок 16 оперативной памяти, триггер 17, с первого по четвертый элементы НЕ 18-21, счетчик 22, коммутатор 23, первый 24 и второй 25 резисторы, первый 26 и второй 27 одновибраторы, элемент 28 задержки, регистр 29, элемент 2И-ИЛИ 30, сигнатурный анализатор 31. Изобретение позволяет выявить дефектные накопительные резисторы доменной памяти и диагностировать их состояние аппаратными средствами. 5 ил.

фае 2

W

9В

38

97

3

192

Ц&

h

т

|Н

Ъ J

103

%

98

101

71

72

WlT

199

Z$MO

&б

фиаЗ

Фиг 4

| Circuits Manufacturing, 1979, № 12, v | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент СМА (Р 4233668, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

Авторы

Даты

1990-05-15—Публикация

1988-08-18—Подача