1 Т.11п V рлнг)р;гфял.11ых ключей, две -11Г.м:чтов Т, дня элемеитя И.ЛИ /Ц, :1 tic-r-reriTH И,генератор тактоп, счргчик адреса и дешифратор, причем (.пока постоянной памяти через репи.тр соединен с пepвы f выходом блока управления, а групгта адресных входов - с выходами элементов НИИ группы,входы каждого из которых соеnHneiiFii с выходами одноименнных многоразрядных ключей группы, входы которых соединены с выходами соответствующих счетчиков группы, первые и вторые входы которых соединены соответственно с выходами одноразрядных ключей группы и выходами элементов И первой группы, первые входы которых объединены и являются входом неисправности блока управления, первые входы элементов И второй группы об7зединены и являются входом готовНОСТР блока управления, вторые входы

1 1

19

элементов Н первой и второй соединены с.соответствующими выходами дешифратора, а выходы - соответственно с входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами первого элемента И, выход которого соединен с первым входом второго элемента И, второй вход и выход которого соединены соответственно с первым выходом генератора тактов и входом счетчика адреса, . выход которого соединен с входом дешифратора и является вторым выходом блока управления, второй и третий выходы генератора тактов соединены соответственно с управляющим входом регистра и первыми входами одноразрядных ключей группы, вторые входы которых и вторые входы многоразрядны ключей группы соединены с выходами элементов И второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для автоматического контроля микропроцессоров | 1984 |

|

SU1264182A2 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для сбора информации от многоразрядных дискретных датчиков | 1986 |

|

SU1529230A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ МИКРОПРОЦЕССОРОВ, содержащее блок управления и канал контроля, состоящий из селектора адреса, блока сравнения, эталонного микропроцессора, блока индикации, блока формирователей импульсов, генератора импульсов, блока памяти и дешифратора состояний выводов, отличающееся тем, что, с целью повьпиения производительности, в него введены N--1 каналов контроля, а в каждый канал контроля введены блок регистровой памяти, схема сравнения, элемент ИЛИ, триггер готовности, коммутатор и селектор, причем в каждом канале контроля разрядные выходы коммутатора соединены соответственно с первым входом триггера готовности, первым входом схемы сравнения, информационньп входом блока памяти и управляющим входом генератора импульсов, выход которого соединен с тактовым входом блока формирователей импульсов, информационный вход которого соединен с выходом блока памяти, а первьй и второй выходы подключены соответственно к входам контролируемого и эталонного микропроцессоров,, вьгходы которых подключены соответственно к первому и второму входам блока сравнения, выход эталонного микропроцессора соединен через блок регистродой памяти с первым входом блока индикации, второй вход которого соединен с информационным выходом блока сравнения, выход эталонного микропроцессора соединен с вторым входом схемы сравнения, через дешифратор состояний выводов - с разрешающим входом блока формирователей импульсов, а через селектор адреса с адресным входом блока памяти, вы(Л С ход схемы сравнения соединен с первым входом элемента ИЛИ, выход которого соединен с вторым входом триггера готовности, выход которого соеS динен с входами готовности блока формирователей импульсов и коммутатора, выход несовпадения блока сравнения соединен с вторым входом элемента ИЛИ и через коммутатор с входом неисправ ности блока управления, вход готовности которого соединен с соответстСП вующим в1-кодом коммутатора, входы сброса блока сравнения, блока регистсо ровой памяти и третий вход элемента ИЛИ образуют вход сброса устройства, информационный вход коммутатора каждого канала контроля соединен с первым выходом блока управления, второй выход которого через селектор соединен с управляющим входом коммутатора, причем блок управления содержит блок постоянной памяти, регистр, группу элементов ИШ1, группу многоразрядных ключей,группу счетчиков.

Изобретение относится к цифровой вычислительной технике, в частности к средствам контроля и поиска неисправности в устройствах, например в микропроцессорах.

Известно устройство, содержащее блок управления, эталонньв1 и контролируе( блоки, блок сравнения и бло индикации l .

Недостатком его является отсутствие возможности контроля дискретных объектов с двунаправленными шинами.

Наиболее близким изобретению по технической сущности является устройство для автоматического контроля больших интегральных схем, содержащее блок управления и пост контроля, включающий селектор адреса, блок сравнения, эт 1лонный и контролируемый блоки, блок индикации, фор.мирователь входных сигналов, генератор, блок памяти и дешифратор состояния выводов эталонного блока 2.

Недостатками известного устройства являются ограниченная производительность и невысокие диагностические возможности.

Цель изобретения - повьшение производительн(зсти.

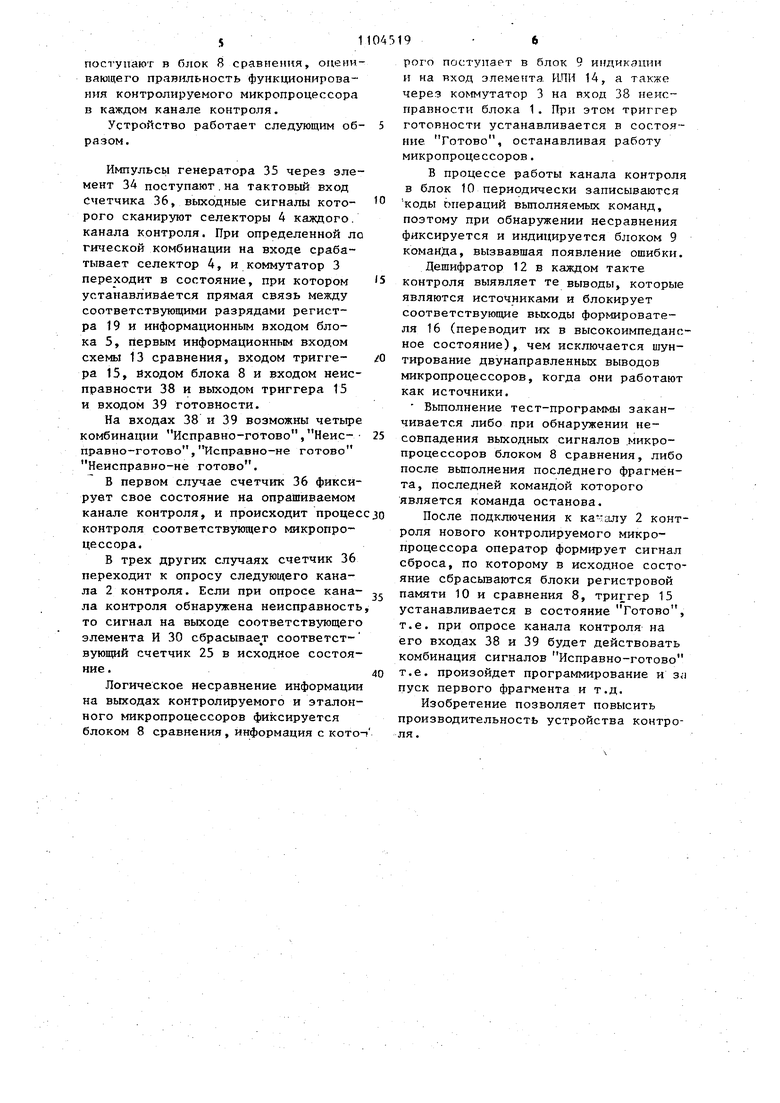

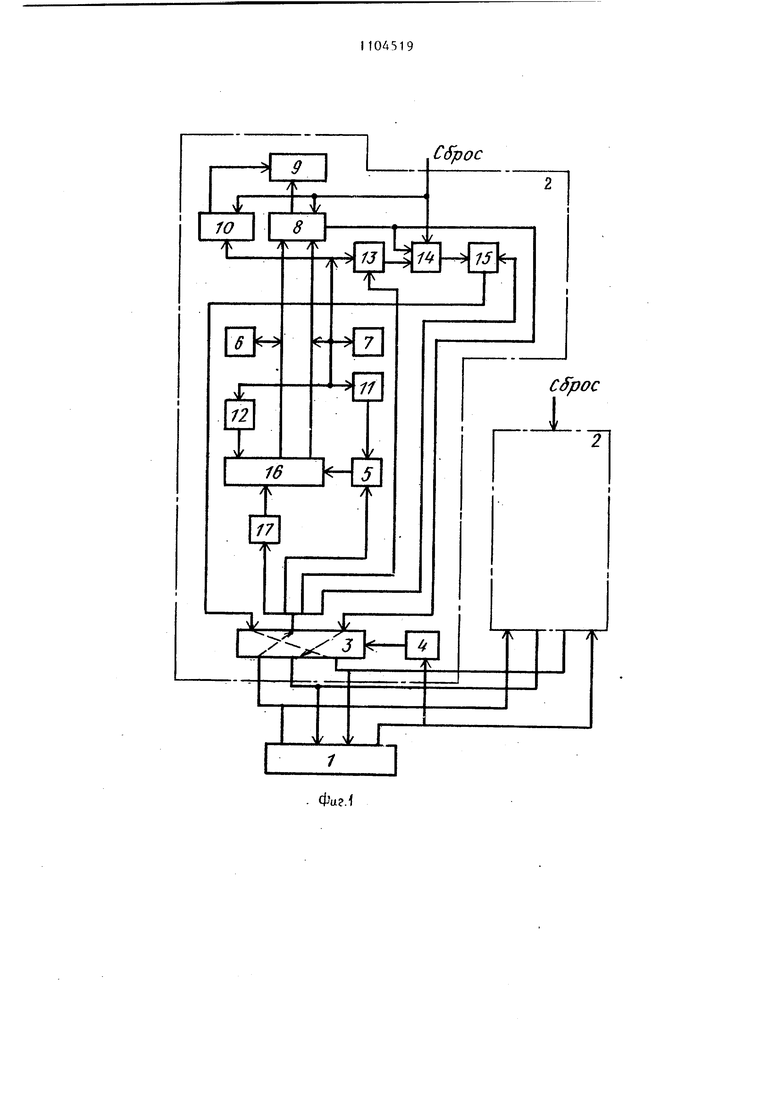

Поставленная цель достигается тем, что в многоканальное устройство для автоматического контроля микропроцессоров, содержащее блок управления и канал контроля, состоящий из селектора адреса, блока сравнения эталонного микропроцессора, блока индикации, блока формирователей импульсов, генератора импульсов, блока памяти и дешифратора состояний выводов, введены N-1 каналов контроля , а в каждый канал контроля введены блок регистровой памяти, схема сравнения, элемент ИЛИ, триггер готовности, коммутатор и селектор, причем в каждом канале контроля разрядные выходы коммутатора соединены соответственно с первым входом триггера готовности, первьм входом схемы сравнения, информационным входом блока памяти и управляющим входом генератора импульсов, выход которого соединен с тактовым входом блока формирователей импульсов, информационный вход которого соединен с выходом блока памяти, а первый и второй выходы подключены соответственно к входам контролируемого и этлонного микропроцессоров, выходы которых поцклюгены соответственно IS первому и второму входам блока сравнения, выход эталонного микропр цессора соединен через блок регистр вой памяти с первым входом блока индикации, вторэй вход которого сое динен с информационным выходом блок сравнения, выход эталонного микропроцессора соединен с вторым входом схемы сравнения, через дешифратор состояний выводов - с разрешающим входом блока формирователей импульсов, а через селектор адреса - с ад ресным входом блока памяти, выход схемы сравнения соединен с первым входом элемента ИЛИ, выход которого соединен с вторым входом триггера готовности, выход которого соединен с входами готовности блока формирователей импульсов и коммутатора, вы ход несовпадения блока сравнения со динен с вторым входом элемента ИЛИ и через коммутатор с входом неиспра ности блока управления, вход готовности которого соединен с срответст вующим выходом коммутатора, входы сброса блока сравнения, блока регис ровой памяти и третий вход элемента ИЛИ образуют вход сброса устройства, информационный вход коммутато ра каждого канала контроля соединен с первым выходом блока управления, второй выход которого через селектор соединен с управляющим входом коммутатора, причем блок управления содержит блок постоянной памяти, регистр, группу элементов ИЛИ, груп пу многоразрядных ключей, группу счетчиков, группу одноразрядных ключей, две группы элементов И, два элемента ИЛИ, два элемента И, генератор тактов, счетчик адреса и дешифратор, причем выход блока постоянной памяти через регистр соединен с первым выходом блока управления, а группа адресных входов - с выходами элементов ИЛИ груп пы, входы каждого из которых соедин ны с вькодами одноименных многоразрядных ключей группы, входы которых соединены с выходами соответствующих счетчиков группы, первые и вторые входы которых соединены соответствен но с выходами одноразрядных ключей группы и выходами элементов И первой группы, первые входы которых объеди нены и являются входом неисправности блока управления, первые входы элементоп И второй группы объединены и являются входом готовности блок управления, вторые входы элементов И первойи второй групп соедт): с соответствующими выходами дешифратора, а выходы - соответственно с входами первого и второго элементов РШИ, выходы которых соединены соответственно с первым и вторым входами первого элемента Ц, выход которого соединен с первым входом второго элемента И, второй вход и выход которого соединены соответственно с первым выходом генератора тактов и входом счетчика адреса, вькод которого соединен с входом дешифратора и является вторым выходом блока управления, второй и третий выходы генератора тактов соединены соответственно с управляющим входом регистра и первыми входами одноразрядных ключей группы, вторые входы которых и вторые входы многоразрядных ключей группы соединены с выходами элементов И второй группы. На фиг. 1 изображена схема устройства; на фиг. 2 - схема блока управления. Устройство содержит блок 1 управления, канал 2 контроля, коммутатор 3, селектор 4, блок 5 памяти, контролируемьпЧ микропроцессор 6, эталонный микропроцессор 7, блок 8 сравнения, блок 9 индикации, блок 10 регистровой памяти, селектор 11 адреса, дешифратор 12 состояния выводов, схему 13 сравнения, элемент ИЛИ 14, триггер 15 готовности, блок 16 формирователей импульсов, генератор 17, блок 18 постоянной памяти, регистр 19, группу 20 элементов ИЛИ, элементы ИЛИ 21, группу 22 многоразрядных ключей 23, группу 24 счетчиков 25, группу 26 одноразрядных ключей 27, первую группу 28 и вторую группу 29 элементов И 30, элементы ИЛИ 31 и 32, элементы И 33 и 34, генератор 35 тактов, счетчик 36 адреса, дешифратор 37, вход 38 неисправности, вход 39 готовности. Устройство обеспечивает контроль микропроцессоров на детерминированных тестах, задаваемых в виде программно-реализуемого алгоритма с помощью тест-программы, которая хранится в блоке 18 и по частям по мере его вьтолнения .перегружается в режиме прямого доступа в блок 5. Выходные сигналы ьшкропроцессоров

поступают в блок 8 сравнения, оценивающего правильность функционирования контролируемого микропроцессора в каждом канале контроля.

Устройство работает следующим образом.

Импульсы генератора 35 через элемент ЗА поступают.на тактовый вход счетчика 36, выходные сигналы которого сканируют селекторы 4 каждого, канала контроля. При определенной ло гжгеской комбинации на входе срабатывает селектор 4, и коммутатор 3 переходит в состояние, при котором устанавливается прямая связь между соответствующими разрядами регистра 1 9 и информационным входом блока 5, первым информационным входом схемы 13 сравнения, входом триггера 15, Входом блока 8 и входом неисправности 38 и выходом триггера 15 и входом 39 готовности.

На входах 38 и 39 возможны четьфе комбинации Исправно-готово,Нейсправно-готово,Исправно-не готово Неисправно-не готово.

В первом случае счетчик 36 фиксирует свое состояние на опрашиваемом канале контроля, и происходит процес контроля соответствующего микропроцессора.

В трех других случаях счетчик 36 переходит к опросу следующего канала 2 контроля. Если при опросе канала контроля обнаружена неисправность то сигнал на выходе соответствующего элемента И 30 сбрасывае соответствующий счетчик 25 в исходное состояние.

Логическое несравнение информации на выходах контролируемого и эталонного микропроцессоров фиксируется блоком 8 сравнения, информация с кото

рого поступает в блок 9 индикдпии и на вход элемента НИИ 14, а также через коммутатор 3 на вход 38 неисправности блока 1. При этом триггер готовности устанавливается в состояние Готово, останавливая работу микропроцессоров.

В процессе работы канала контроля в блок 10 периодически записываются коды операций выполняемых команд, поэтому при обнаружении несравнения фиксируется и индицируется блоком 9 команда, вызвавшая появление ошибки.

Дешифратор 12 в каждом такте контроля выявляет те выводы, которые являются источниками и блокирует соответствующие выходы формирователя 16 (переводит их в высокоимпедансное состояние), чем исключается шунтирование двунаправленных: выводов микропроцессоров, когда они работают как источники.

Вьшолнение тест-программы заканчивается либо при обнаружении несовпадения выходных сигналов микропроцессоров блоком 8 сравнения, либо после вьшолнения последнего фрагмента, последней командой которого является команда останова.

После подключения к 2 контроля нового контролируемого микропроцессора оператор формирует сигнал сброса, по которому в исходное состояние сбрасываются блоки регистровой памяти 10 и сравнения 8, триггер 15 устанавливается в состояние Готово, т.е. при опросе канала контроля на его входах 38 и 39 будет действовать комбинация сигналов Исправно-готово т.е. произойдет программирование и 3 пуск первого фрагмента и т.д.

Изобретение позволяет повысить производительность устройства контроля.

8

10

f I

12

17 Ж

.

/

(

Сброс

Urrb

У

i

фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля интегральных схем | 1975 |

|

SU553618A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для автоматическогоКОНТРОля бОльшиХ иНТЕгРАльНыХ CXEM | 1978 |

|

SU798841A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1982-07-05—Подача