Изобретение относится к автоматике и вычислительной технике и может найти применение при построении надежных распределителей импульсов с обнаружением сбоев в течение цикла работы.

Устройство предназначено для использования в тех случаях, когда на время обнаружения ошибки не наложено жестких ограничений.

Целью изобретения является повышение достоверности функционирования за счет увеличения глубины контроля сбоев и упрощение.

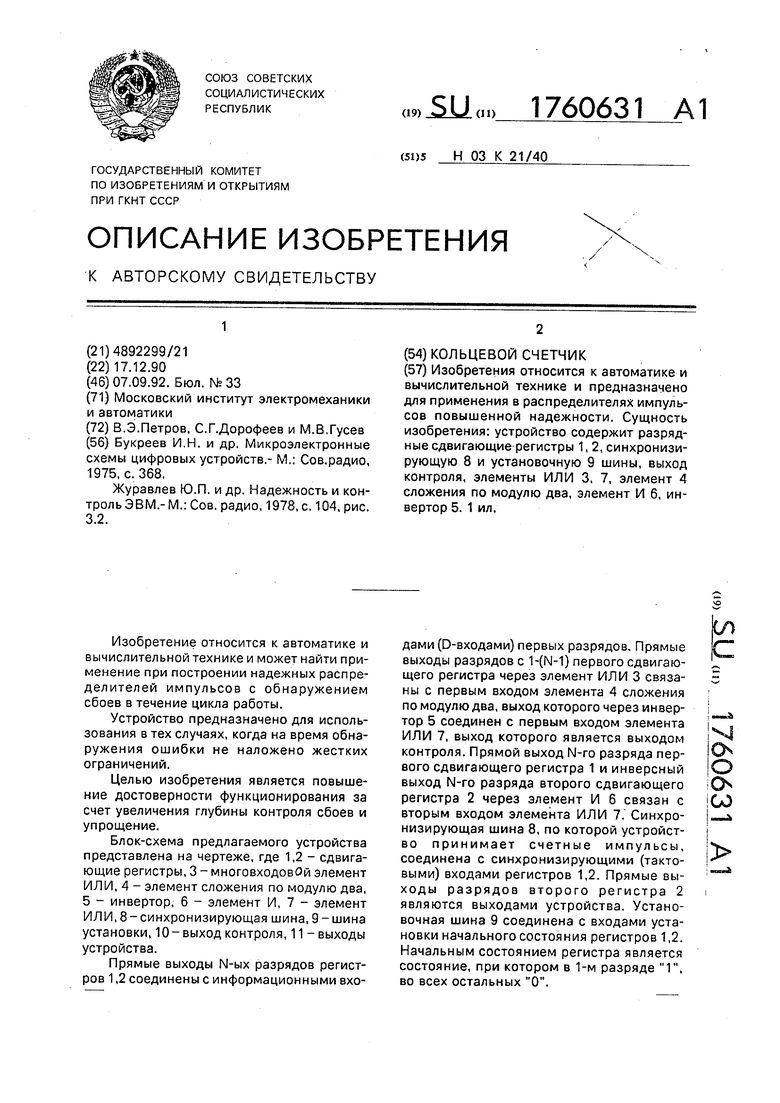

Блок-схема предлагаемого устройства представлена на чертеже, где 1,2 - сдвигающие регистры, 3 - многовходовОй элемент ИЛИ, 4 - элемент сложения по модулю два, 5 - инвертор, 6 - элемент И, 7 - элемент ИЛИ,8-синхронизирующая шина, 9-шина установки, 10-выход контроля, 11 -выходы устройства.

Прямые выходы N-ых разрядов регистров 1,2 соединены с информационными входами (D-входами) первых разрядов. Прямые выходы разрядов с 1-(N-1) первого сдвигающего регистра через элемент ИЛИ 3 связаны с первым входом элемента 4 сложения по модулю два, выход которого через инвертор 5 соединен с первым входом элемента ИЛИ 7, выход которого является выходом контроля. Прямой выход N-ro разряда первого сдвигающего регистра 1 и инверсный выход N-ro разряда второго сдвигающего регистра 2 через элемент И 6 связан с вторым входом элемента ИЛИ 7. Синхронизирующая шина 8, по которой устройство принимает счетные импульсы, соединена с синхронизирующими (тактовыми) входами регистров 1,2. Прямые выходы разрядов второго регистра 2 являются выходами устройства. Установочная шина 9 соединена с входами установки начального состояния регистров 1,2. Начальным состоянием регистра является состояние, при котором в 1-м разряде 1, во всех остальных О.

сл

с

-А

XI

о о

О GO

Перед началом работы оба регистра 1,2

устанавливаются в состояние 1000. При

поступлении тактовых сигналов на шину 9 регистры 1,2 осуществляют их пересчет по модулю N. Если в результате сбоя в регистрах 1,2 возникают неравные коды, то через число тактов не более N в М-х разрядах будут различные сигналы и на выходе 10 появляется 1, свидетельствующая об ошибке.

Если в результате сбоя оба регистра установятся в одинаковые запрещенные состояния (т.е. состояния, которые не содержат единственную единицу), то через число входных тактов, не превышающее N. на входах элемента 4 будут две единицы или два нуля, что также формирует на выходе 10.

Регистры сдвига могут быть построены на базе стандартных синхронных D-тригге- ров или IK-триггеров, При этом шина начальной установки соединяется с асинхронным входом установки в 1 первого триггера и асинхронными входами установки в О всех последующих триггеров, а синхронизирующая шина соединена с синхронизирующими входами всех триггеров.

Рассмотрим преимущества предлагаемого устройства по сравнению с известным

Учитывая то, что предлагаемое устрой ство обнаруживает бол мне сбоев, чем известное (дополнительно обнаруживаются все сбои, в результате которых оба регистра устанавливаются в одно и то же запрещенное состояние), можно сделать вывод о том, что глубина контроля предлагаемого решения существенно больше (так как обнаруживается дополнительно 2N-M таких состояний).

Построение схемы сравнения прототипа требует использования N элементов сло- жения по модулю два и N-входового элемента ИЛИ, В отличие от этого цепи контроля данного устройства содержат элемент ИЛИ с N-1 входами, элемент сложения по модулю два, инвертор, элементы И, ИЛИ. Заметим, что инвертор 5 и элементы И, ИЛИ 6,7 эквивалентны по сложности элементу А

сложения по модулю два. Учитывая вышеизложенное, можно сделать вывод, что предлагаемая схема содержит на N-2 элементов сложения по модулю два меньше и элемент

ИЛИ с меньшим числом входов.

На предприятии-заявителе предполагается использовать предлагаемое устройство при построении управляющих и синхронизирующих цепей в цифровых системах переработки информации.

Ожидаемый положительный эффект заключается в повышении достоверности функционирования и /прощении тех задачах, где допускается задержка сигнала контроля

на время, че превышающее модуль счета. Формула изобретения Кольцевой счетчик, содержащий два идентичных N-разрядных сдвигающих регистра, синхронизирующую и установочную

шины и выход контроля, прямой выход М-го разряда каждого сдвигающего регистра соединен с информационным входом первого разряда того же регистра, синхронизирующая и установочные шины соединены соотаетственно с синхронизирующими и установочными входами сдвигающих регистров, отличающийся тем, что, с целью упрощения и повышения глубины контроля сбоев в случае, если на время задержки сигнала обнаружения сбоя наложено огргниче- н..: т Т, где Т -- период работы, введены м.-юговходовый элемент ИЛИ, элемент сложения по модулю два, элемент И, элемент ИЛИ к инвертор, причем прямые выходы

разрядов с первого по (М-1)-й первого сдвигающего регистра через многовходовый элемент ИЛИ связаны с первым входом элемента сложения по модулю два, выход которой через инвертор связан с первым входом

элемента ИЛИ, выход которого соединен с выходом контроля, второй вход элемента сложения по модулю два соединен с прямым выходом N-го разряда первого регист- оа сдвига, инверсный выход N-го разряда

второго сдвигающего регистра соединен с вторым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик с контролем | 1990 |

|

SU1720155A1 |

| Счетчик с контролем | 1983 |

|

SU1123106A1 |

| Линейный счетчик | 1986 |

|

SU1338064A1 |

| Счетчик | 1987 |

|

SU1434542A1 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| Устройство для синхронизации с контролем | 1983 |

|

SU1161933A1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

Изобретения относится к автоматике и вычислительной технике и предназначено для применения в распределителях импульсов повышенной надежности. Сущность изобретения: устройство содержит разрядные сдвигающие регистры 1,2,синхронизирующую 8 и установочную 9 шины, выход контроля, элементы ИЛИ 3, 7, элемент 4 сложения по модулю два, элемент И 6, инвертор 5. 1 ил.

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств.- М.; Сов.радио, 1975, с | |||

| Полу генеративная топка для сжигания влажного торфа | 1921 |

|

SU368A1 |

| Журавлев Ю.П | |||

| и др | |||

| Надежность и контроль ЭВМ.- М.: Сов | |||

| радио, 1978, с | |||

| Счетная таблица | 1919 |

|

SU104A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-09-07—Публикация

1990-12-17—Подача