Изобретение относится к технике связи и может использоваться в устройствах, обеспечивающих прием информации по симплексным или полудуплексным каналам связи с дублированием передачи по дополнительному каналу связи и использованием кодов, обнаруживающих ошибки.

Известны устройства для приема дискретной информации, например Ю.М.Мартынов Обработка информации в системах передачи данных изд. Связь, 1969г.с. 72- 82; В.Г.Каминский и А.Г. Мельников Устройство для приема дискретной информации авторское свидетельство N° 517172,03.07.1974 г; А.Г.Мельников и И.И. Кудрявцев Устройство для приема дискретной информации авторское свидетельство № 902293 от 12.03.1980 г.

Из известных устройств для приема дискретной информации наиболее близким по технической сущности к предлагаемому является Устройство для приема дискретной

информации авторское свидетельство N 517172 от 03.07.1974 г.. авторов В.Г.Каминского и А.Г.Мельникова.

В этом устройстве производится сравнение знаков, принятых по основному и дополнительному каналам связи и при приеме двух разрешенных по коду, но не совпадающих между собой знаков потребителю выдается знак из того канала связи, в котором перед сравниваемым знаком не было искаженных знаков, т.е. не было ошибок.

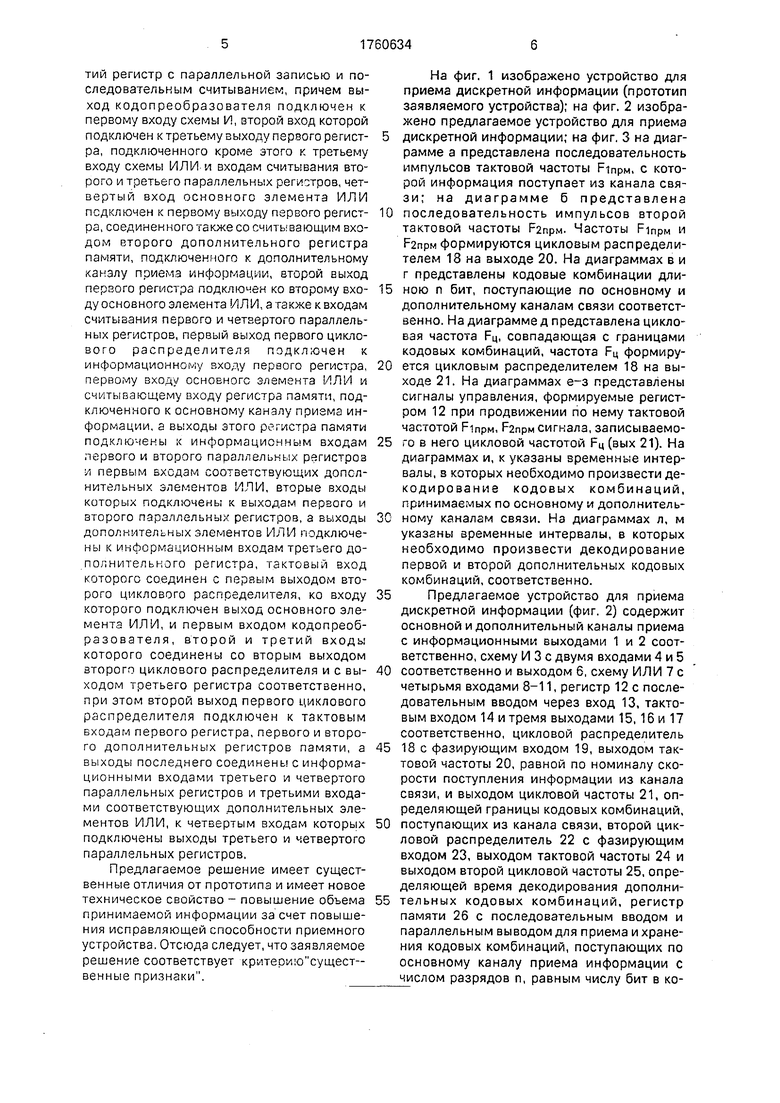

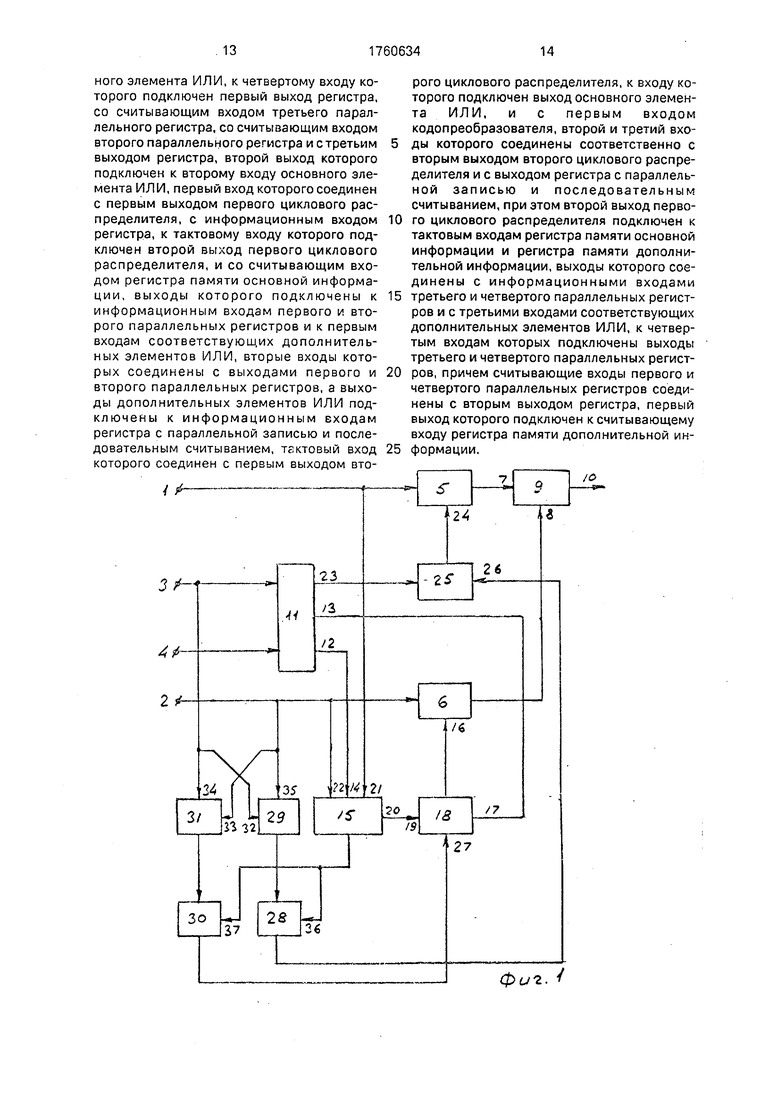

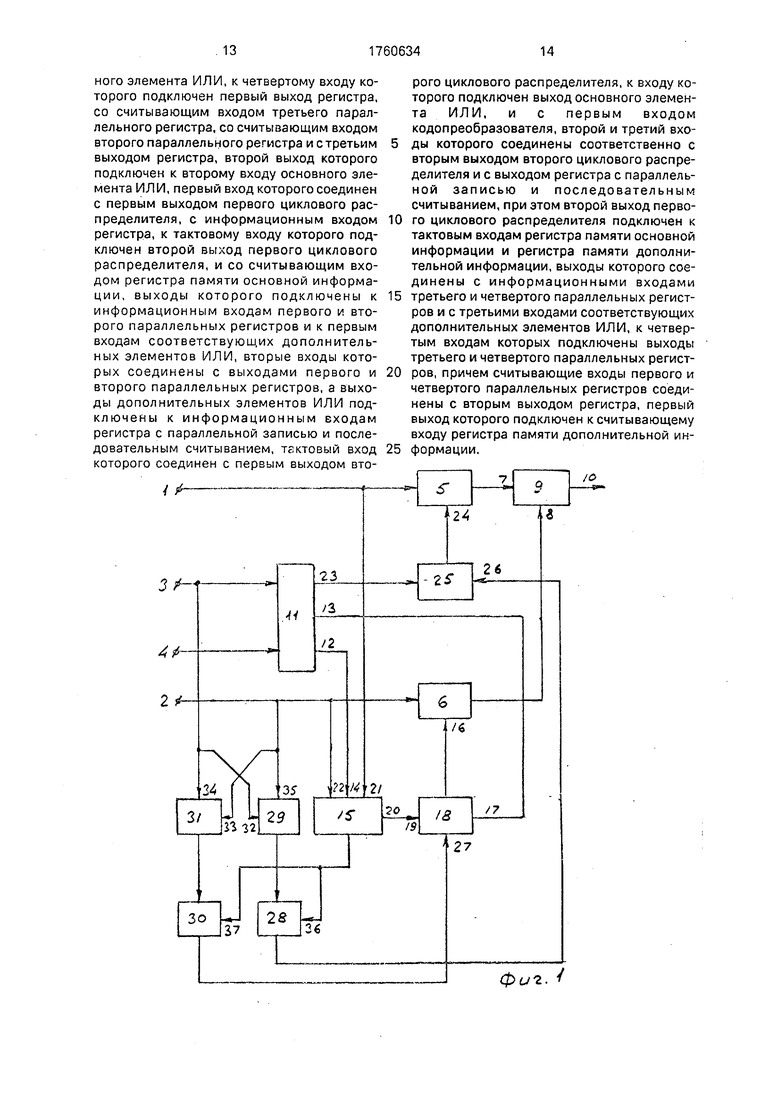

Блок-схема известного устройства представлена на фиг. 1. Оно содержит основной и дополнительный каналы приема с информационными выходами 1 и 2 и с выходами сигналов ошибок 3 и 4 соответственно. К информационным выходам 1, 2 подключены элементы И 5,6, выходы которых подключены ко входам 7,8 первого элемента ИЛИ 9, выход которого 10 является выходом устройства. К выходам сигналов ошибок 3,4

™л

о

IGJ

подключены входы схемы управления 11, а ее выходы 12, 13 подключены соответственно к входу 14 схемы сравнения 15 и входу 16 элемента И 6 через вход 17 второго элемента ИЛИ 18, второй вход которого 19 соединен с выходом 20 схемы сравнения 15. Входы 21, 22 схемы сравнения 15 соединены с информационными выходами 1, 2 каналов, выход 23 схемы управления 11 подключен к входу 24 элемента И 5 через дополнительный элемент ИЛИ 25, второй вход 26 которого, а также вход 27 второго элемента ИЛИ 18 соединены с входами схемы управления 11 через соответствующие последовательно соединенные ячейку памяти 28, элемент ЗАПРЕТ 29 и ячейку памяти 30, элемент ЗАПРЕТ 31. При этом управляющие входы 32 и 33 элементов ЗАПРЕТ 29, 31 соединены с информационными входами 34, 35 элементов ЗАПРЕТ 31, 29 соответственно, а объединенные управляющие входы 36, 37 ячеек памяти 28, 30, образующих регистр, соединены с дополнительным выходом 38 схемы сравнения 15. Устройство работает следующим образом. С выходов 1,3 и 2,4 основного и дополнительного каналов поступают информация и сигналы ошибок. Когда сигналы ошибок поступают на входы схемы управления 11, она выдает решения по выходу 23 в случае отсутствия ошибки в кодовом блоке, принятом по основному каналу, и наличия ошибки в кодовом блоке, принятом по дополнительному каналу, по выходу 13 при наличии ошибки в кодовом блоке, принятом по основному каналу и при отсутствии ошибки в кодовом блоке, принятом по дополнительному каналу, и по выходу 12 - в случае отсутствия ошибки в кодовом блоке, принятом как по основному, так и по дополнительному каналам,

При выдаче схемой управления решения по выходу 23, информация с выхода 1 основного канала через разрешающие элементы И 5 и ИЛИ 9 поступает на выход 10 устройства. При выдаче решения по выходу 13 на выход 10 устройства информация поступает через разрешающие элементы И 6 и ИЛИ 9 с выхода 2 дополнительного канала приема. При выдаче схемой управления 11 решения по выходу 12 этот сигнал поступает на схему сравнения 15, где поэлементно сравнивается информация, поступившая на другие ее входы 21 и 22 из каналов приема. В случае выдачи по результату сравнения (сравнения всех двоичных элементов комбинаций) с выхода 20 схемы сравнения 15 на второй вход 19 элемента ИЛИ 18 положительного решения, информация на выход 10 устройства поступает через разрешающие элементы И 6 и ИЛИ 9 с выхода 2 дополнительного канала приема. Если результат сравнения отрицательный, сигнал с дополнительного выхода 38 схемы сравнения 15 поступает на управляющие входы 36 и 37

ячеек памяти 28 и 30. Сигналы ошибок из каналов поступают на информационные 35, 34 и управляющие 32, 33 входы элементов ЗАПРЕТ 29,31. При этом с элемента ЗАПРЕТ 29 сигнал поступает и записывается в

ячейку памяти 28 только в том случае, если ошибка была зарегистрирована в дополнительном канале. В ячейку памяти 30 сигнал записывается в том случае, если сигнал ошибки поступает по основному каналу. С

ячеек памяти 28, 30 информация считывается сигналом отрицательного результата сравнения со схемы сравнения 15 по длине соседнего (предыдущего) блока. Сигналы, считанные с ячеек памяти 28, 30 разрешают

прохождение информации на выход 10 устройства соответственно через элементы ИЛИ 25, И 5, ИЛИ 18, И 6 основного и дополнительного каналов приема.

При наличии ошибок одновременно в

основном и дополнительном каналах сигналы ошибок не проходят через элементы ЗАПРЕТ 29, 31, в результате чего информация из этих каналов не выдается. Таким образов данное устройство не бра кует информацию,

а выполняет ее выборку из основного или дополнительного канала приема в зависимости от искажений в основном и дополнительном каналах связи.

Недостатком данного устройства

является низкая вероятность доставки сообщения по причине невозможности формирования неискаженного знака сообщения в случае обнаружения ошибок в одноименных кодовых комбинациях

принятых по основному и дополнительному каналам связи, т.е. снижение объема принимаемой из канала связи информации.

Целью изобретения является увеличение объема принимаемой информации за

счет повышения исправляющей способности принимающего устройства.

Данная цель достигается тем, что в известное устройство для приема дискретной информации с использованием кодов, обнаруживающий ошибки, содержащее основной и дополнительный каналы приема с информационными выходами, схемы И и ИЛИ и первый регистр введены дополнительно два цикловых распределителя, регистр памяти информации, поступающей пс основному каналу приема, второй регистр памяти информации, поступающей по дополнительному каналу приема, четыре параллельных регистра, дополнительные

элементы ИЛИ, кодопреобразователь и третий регистр с параллельной записью и последовательным считыванием, причем выход кодопреобразователя подключен к первому входу схемы И, второй вход которой подключен к третьему выходу первого регистра, подключенного кроме этого к третьему входу схемы ИЛИ-и входам считывания второго и третьего параллельных регистров, чет- вертый вход основного элемента ИЛИ подключен к первому выходу первого регистра, соединенного также со считывающим входом второго дополнительного регистра памяти, подключенного к дополнительному каналу приема информации, второй выход первого регистра подключен ко второму входу основного элемента ИЛИ, а также к входам считывания первого и четвертого параллельных регистров, первый выход первого циклового распределителя подключен к информационному входу первого регистра, первому входу основного элемента ИЛИ и считывающему входу регистра памяти, подключенного к основному каналу приема информации, а выходы этого регистра памяти подключены к информационным входам первого и второго параллельных регистров л первым входам соответствующих дополнительных элементов ИЛИ, вторые входы которых подключены к выходам первого и второго параллельных регистров, а выходы дополнительных элементов ИЛИ подключены к информационным входам третьего дополнительного регистра, тактовый вход которого соединен с первым выходом второго циклового распределителя, ко входу которого подключен выход основного элемента ИЛИ, и первым входом кодопреобразователя, второй и третий входы которого соединены со вторым выходом второго циклового распределителя и с выходом третьего регистра соответственно, при этом второй выход первого циклового распределителя подключен к тактовым входам первого регистра, первого и второго дополнительных регистров памяти, а выходы последнего соединены с информационными входами третьего и четвертого параллельных регистров и третьими входами соответствующих дополнительных элементов ИЛИ, к четвертым входам которых подключены выходы третьего и четвертого параллельных регистров.

Предлагаемое решение имеет существенные отличия от прототипа и имеет новое техническое свойство - повышение объема принимаемой информации за счет повышения исправляющей способности приемного устройства. Отсюда следует, что заявляемое решение соответствует критери о сущест- венные признаки.

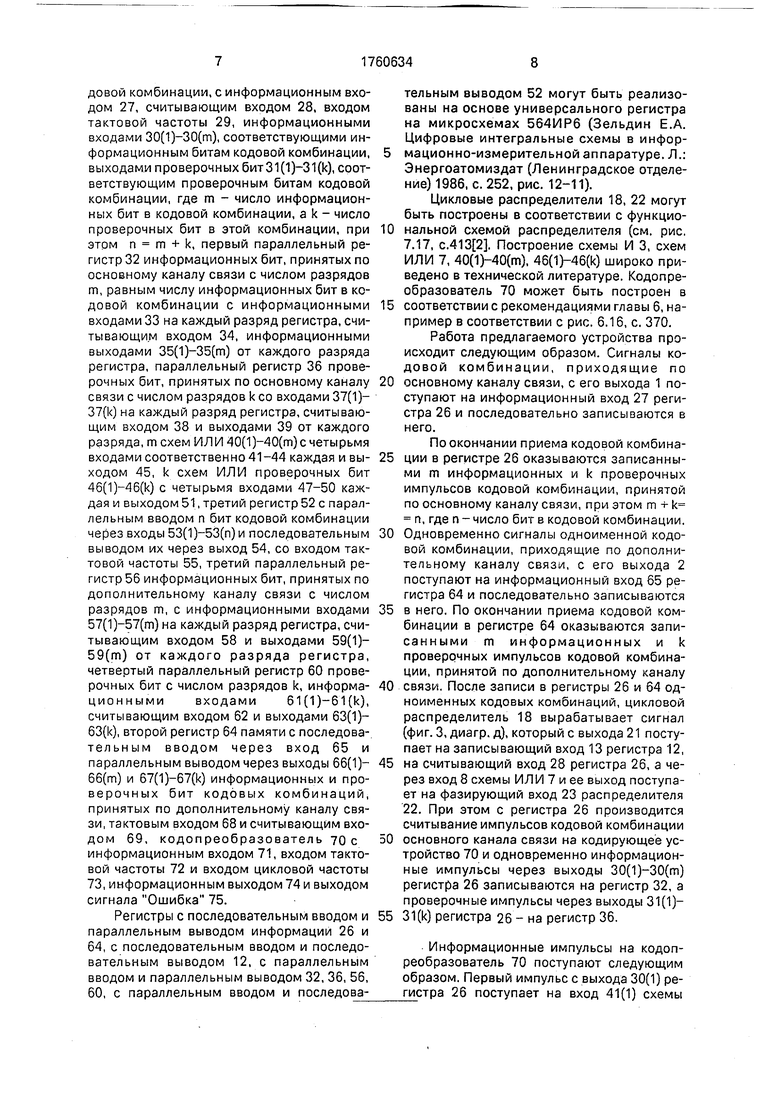

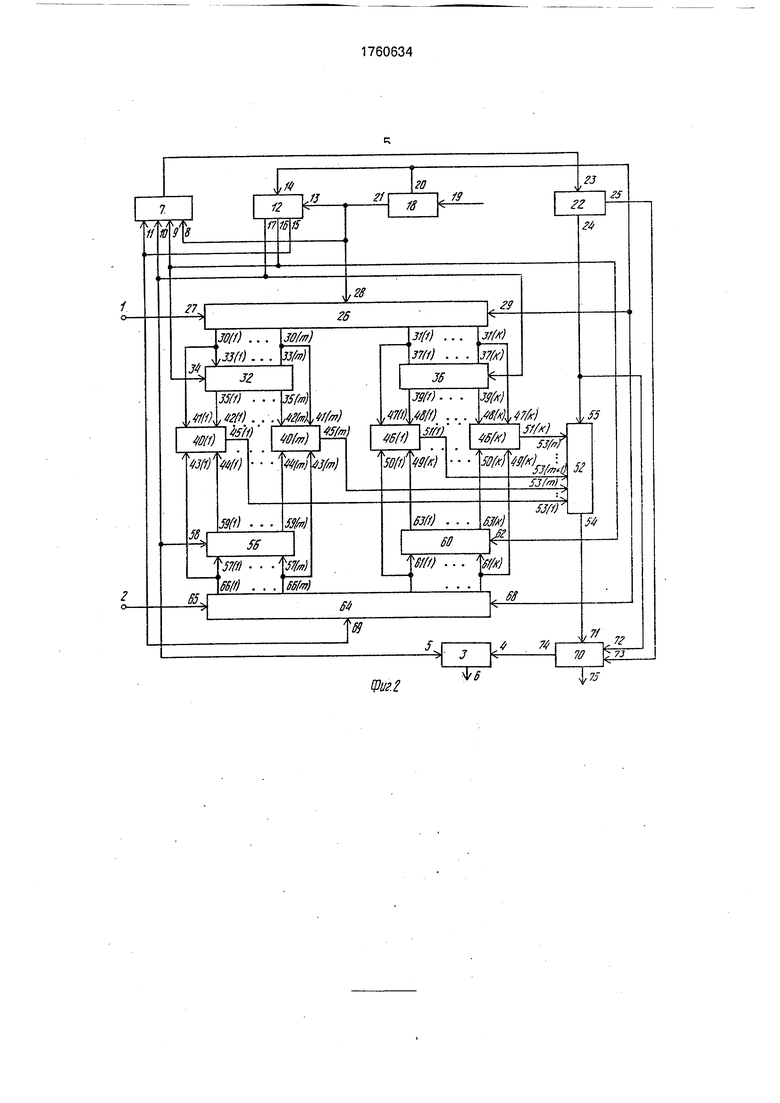

На фиг. 1 изображено устройство для приема дискретной информации (прототип заявляемого устройства); на фиг. 2 изображено предлагаемое устройство для приема

дискретной информации; на фиг. 3 на диаграмме а представлена последовательность импульсов тактовой частоты Р1Прм, с которой информация поступает из канала связи; на диаграмме б представлена

0 последовательность импульсов второй тактовой частоты Р2прм. Частоты Р1Прм и Р2прм формируются цикловым распределителем 18 на выходе 20. На диаграммах в и г представлены кодовые комбинации дли5 ною п бит, поступающие по основному и дополнительному каналам связи соответственно. На диаграмме д представлена цикловая частота Рц, совпадающая с границами кодовых комбинаций, частота Рц формиру0 ется цикловым распределителем 18 на выходе 21. На диаграммах е-з представлены сигналы управления, формируемые регистром 12 при продвижении по нему тактовой частотой FinpM, Рапрм сигнала, записываемо5 го в него цикловой частотой Рц (вых 21). На диаграммах и, к указаны временные интервалы, в которых необходимо произвести де- кодирование кодовых комбинаций, принимаемых по основному и дополнительС ному каналам связи. На диаграммах л, м указаны временные интервалы, в которых необходимо произвести декодирование первой и второй дополнительных кодовых комбинаций, соответственно.

5 Предлагаемое устройство для приема дискретной информации (фиг. 2) содержит основной и дополнительный каналы приема с информационными выходами 1 и 2 соответственно, схему И 3 с двумя входами А и 5

0 соответственно и выходом 6, схему ИЛИ 7 с четырьмя входами 8-11, регистр 12 с последовательным вводом через вход 13, тактовым входом 14 и тремя выходами 15,16 и 17 соответственно, цикловой распределитель

5 18с фазирующим входом 19, выходом тактовой частоты 20, равной по номиналу скорости поступления информации из канала связи, и выходом цикловой частоты 21, определяющей границы кодовых комбинаций,

0 поступающих из канала связи, второй цикловой распределитель 22 с фазирующим входом 23, выходом тактовой частоты 24 и выходом второй цикловой частоты 25, определяющей время декодирования дополни5 тельных кодовых комбинаций, регистр памяти 26 с последовательным вводом и параллельным выводом для приема и хранения кодовых комбинаций, поступающих по основному каналу приема информации с числом разрядов п, равным числу бит в кодовой комбинации, с информационным входом 27, считывающим входом 28, входом тактовой частоты 29, информационными входами 30(1)-30(т), соответствующими информационным битам кодовой комбинации, выходами проверочных бит 31(1)-31(к), соответствующим проверочным битам кодовой комбинации, где m - число информационных бит в кодовой комбинации, a k - число проверочных бит в этой комбинации, при этом n m + k, первый параллельный регистр 32 информационных бит, принятых по основному каналу связи с числом разрядов т, равным числу информационных бит в кодовой комбинации с информационными входами 33 на каждый разряд регистра, считывающим входом 34, информационными выходами 35(1)-35(т) от каждого разряда регистра, параллельный регистр 36 проверочных бит, принятых по основному каналу связи с числом разрядов k со входами 37(1)- 37(l) на каждый разряд регистра, считывающим входом 38 и выходами 39 от каждого разряда, m схем ИЛ И 40(1)-4Q(m)c четырьмя входами соответственно 41-44 каждая и выходом 45, k схем ИЛИ проверочных бит 46(1)-46(k) с четырьмя входами 47-50 каждая и выходом 51, третий регистр 52 с параллельным вводом n бит кодовой комбинации через входы 53(1)-53(п) и последовательным выводом их через выход 54, со входом тактовой частоты 55, третий параллельный регистр 56 информационных бит, принятых по дополнительному каналу связи с числом разрядов т, с информационными входами 57(1)-57(т) на каждый разряд регистра, считывающим входом 58 и выходами 59(1)- 59(т) от каждого разряда регистра, четвертый параллельный регистр 60 проверочных бит с числом разрядов k, информа- ционными входами 61(1)-61(k), считывающим входом 62 и выходами 63(1)- 63(k), второй регистр 64 памяти с последова- тельным вводом через вход 65 и параллельным выводом через выходы 66(1)- 66(т) и 67(1)-67(к) информационных и проверочных бит кодовых комбинаций, принятых по дополнительному каналу связи, тактовым входом 68 и считывающим входом 69, кодопреобразователь 70 с информационным входом 71, входом тактовой частоты 72 и входом цикловой частоты 73, информационным выходом 74 и выходом сигнала Ошибка 75.

Регистры с последовательным вводом и параллельным выводом информации 26 и 64, с последовательным вводом и последовательным выводом 12, с параллельным вводом и параллельным выводом 32, 36, 56, 60, с параллельным вводом и последовательным выводом 52 могут быть реализованы на основе универсального регистра на микросхемах 564ИР6 (Зельдин Е.А. Цифровые интегральные схемы в информационно-измерительнойаппаратуре.Л.: Энергоатомиздат (Ленинградское отделение) 1986, с. 252, рис. 12-11).

Цикловые распределители 18, 22 могут быть построены в соответствии с функциональной схемой распределителя (см. рис. 7.17, с.. Построение схемы И 3, схем ИЛИ 7, 40(1)-40(m), 46(1)-46(k) широко приведено в технической литературе. Кодопреобразователь 70 может быть построен в

соответствии с рекомендациями главы 6, например в соответствии с рис. 6.16, с. 370.

Работа предлагаемого устройства происходит следующим образом. Сигналы кодовой комбинации, приходящие по

основному каналу связи, с его выхода 1 поступают на информационный вход 27 регистра 26 и последовательно записываются в него.

По окончании приема кодовой комбинации в регистре 26 оказываются записанными m информационных и k проверочных импульсов кодовой комбинации, принятой по основному каналу связи, при этом m + k n, где n - число бит в кодовой комбинации.

Одновременно сигналы одноименной кодовой комбинации, приходящие по дополнительному каналу связи, с его выхода 2 поступают на информационный вход 65 регистра 64 и последовательно записываются

в него. По окончании приема кодовой комбинации в регистре 64 оказываются записанными m информационных и k проверочных импульсов кодовой комбинации, принятой по дополнительному каналу

связи. После записи в регистры 26 и 64 одноименных кодовых комбинаций, цикловой распределитель 18 вырабатывает сигнал (фиг. 3, диагр. д), который с выхода 21 поступает на записывающий вход 13 регистра 12,

на считывающий вход 28 регистра 26, а через вход 8 схемы ИЛИ 7 и ее выход поступает на фазирующий вход 23 распределителя 22. При этом с регистра 26 производится считывание импульсов кодовой комбинации

основного канала связи на кодирующее устройство 70 и одновременно информационные импульсы через выходы 30(1)-30(т) регистра 26 записываются на регистр 32, а проверочные импульсы через выходы 31(1)31(k) регистра 26 - на регистр 36.

Информационные импульсы на кодопреобразователь 70 поступают следующим образом. Первый импульс с выхода 30(1) ре- гистра 26 поступает на вход 41(1) схемы

кодовой комбинации потребителю выдается информация и производится установка элементов устройства в исходное состояние.

При наличии ошибки с приходом очередного тактового импульса продвижения сигнала по регистру 12, на его выходе 17 появляется сигнал, который поступает, на считывающий вход 58 регистра 56, считывающий вход 38 регистра 36, на вход 5 схемы И.З, а через четвертый вход 11 схемы ИЛИ 7 - на фазирующий вход 23 циклового распределителя 22. При этом запускается распределитель 22 и на кодопреобразователь 70 считывается вторая дополнительная комбинация, сформированная из информационной части кодовой комбинации, принятой по дополнительному каналу связи и проверочной части, принятой по основному каналу связи. Информационные импульсы второй дополнительной кодовой комбинации считываются следующим образом: с выходов 59 регистра 56 через входы 44 схем ИЛИ 40(1)-40(т), с их выходов 45 на регистр 52. Проверочные импульсы дополнительной кодовой комбинации считываются следующим образом: с выходов 39 регистра 36 через входы 48 схем ИЛИ 46(1)-46(k), с их выходов 51 на регистр 52. С регистра 52 через его выход 54 тактовыми сигналами с распределителя 22 вторая дополнительная кодовая комбинация последовательно считывается на кодопреобразователь 70, который проверяет ее на наличие ошибок. При отсутствии ошибок в этой комбинации потребителю выдается информация, а элементы устройства устанавливаются в исходное состояние. При наличии ошибки в кодовой комбинации потребителю выдается сигнал Ошибка с выхода 6 схемы И 3. Данный сигнал вырабатывается при наличии двух сигналов: сигнала на выходе 17 регистра 12 и сигнала Ошибка на выходе 74 кодопреобразователя 70, после чего схема устанавливается в исходное состояние для приема и обработки по описанному алгоритму очередных кодовых комбинаций, принятых по основному и дополнительному каналам связи.

Предлагаемое устройство для приема дискретной информации имеет существенные отличия от известного как по составу элементов, так и по связям между ними, что и обеспечило положительный -эффект, заключающийся в увеличении вероятности приема сообщения при наличии искажений в канале связи.

Введенная совокупность новых признаков позволяет при обнаружении искажений одноименных кодовых комбинаций в обоих

каналах связи формировать две дополнительные кодовые комбинации из сочетания информационных и проверочных частей кодовых комбинаций, принятых пснэсновному

5 и дополнительному каналам связи.

Формирование двух дополнительных кодовых комбинаций эквивалентно увеличению числа повторений передач сообщения с двух до четырех раз, что увеличивает веро10 ятность приема сообщения (увеличивает объем принимаемой информации). Первая дополнительная кодовая комбинация образуется из информационной части кодовой комбинации, принятой по основному каналу

15 связи и присоединения к ней проверочной части кодовой комбинации, принятой по дополнительному каналу связи.

Вторая дополнительная кодовая комбинация формируется из информационной ча20 сти кодовой комбинации, принятой по дополнительному каналу связи и присоединения к ней проверочной части кодовой комбинации, принятой по основному каналу связи.

25Если обозначить кодовую комбинацию,

принятую по основному каналу связи через И1,П1, а по дополнительному через И2, П2, где И1, И2 - информационные части, а Ш, П2 - проверочные части соответствующих

30 кодовых комбинаций, то общее число кодовых комбинаций на приеме при двукратной передаче сообщения будет 1) И1,П1; 2) И2.П2; 3) И1.П2, 4) И2.П1. Из них комбинации 3 и 4 - дополнительные. Достоверность

35 информации в этом устройстве определяется также избыточностью выбранного кода. При большом числе повторений можно, естественно, сформировать большое число дополнительных кодовых комбинаций. Не40 обходимо отметить, что способ увеличения вероятности доставки сообщения потребителю путем передачи его по нескольким каналам связи широко используется на практике, и особенно эффективен при пере45 даче коротких команд управления. Формула изобретения Устройство для приема дискретной информации, содержащее элемент И, регистр и основной элемент ИЛИ, отличающее

50 с я тем, что, с целью увеличения объема принимаемой информации, введены два цикловых распределителя, регистр памяти основной информации, четыре параллельных регистра, дополнительные элементы

55 ИЛИ, регистр памяти дополнительной информации, регистр с параллельной записью и последовательным считыванием и кодопреобразователь, выход которого подключен к первому входу элемента И, второй вход которого соединен с третьим входом основИЛИ информационных бит 40(1) и с ее выхода 45(1) поступает на первый вход 53(1) регистра 52. Второй импульс, соответственно со второго выхода 30(2) регистра 26 поступает на первый вход 41(2) схемы ИЛИ 40(2) и с ее выхода 45(2) - на второй вход 53(2) регистра 52 (цепь прохождения второго импульса на рис. 2 не показана), т-им- пульс с выхода 30(т) регистра 26 поступает на вход41 (т) схемы ИЛИ40(т)исее выхода 45(т) поступает на вход 53(гл) регистра 52.

Проверочные импульсы кодовой комбинации основного канала считываются следующим образом. Первый импульс с выхода 31(1) регистра 26 поступает на вход 47(1) схемы ИЛИ 46(1) и с ее выхода 51(1) - на первый проверочный вход 53(т + 1) регистра 52, Второй импульс, соответственно, со второго выхода 31(2) регистра 26 поступает на первый вход 47(2) схемы ИЛИ 46(2) и с ее выхода 51(2)- на второй проверочный вход 53(т + 2) регистра 52 (цепь прохождения второго проверочного импульса на рис. 2 не показана), k-й импульс с выхода 31(к) регистра 26 поступает на первый вход 47(k) схемы ИЛИ 46(к) и с ее выхода 51(к) - на вход п регистра 52.

Таким образом, кодовая комбинация с регистра 26 переписывается параллельно на регистр 52, При поступлении на фазирующий вход 23 циклового распределителя 22 через схему ИЛИ 7 сигнала с распределителя 18, он запускается и начинает формировать тактовые и цикловые импульсы для управления работой кодопреобразователя 70, которые соответственно с выходов 24 и 25 распределителя 22 поступают на входы 72 и 73 кодопреобразователя 70 и на вход тактовой частоты 55 регистра 52. При этом кодовая комбинация с регистра 52 последовательно с выхода 54 поступает на кодопре- образователь 70, который производит проверку наличия или отсутствия в ней ошибок, В случае отсутствия ошибок в кодовой комбинации, потребителю с выхода 75 кодопреобразователя 70 выдается ее информационная часть, а все элементы устройства устанавливаются в исходное состояние для приема и анализа очередной комбинации. При обнаружении ошибки в кодовой комбинации, принятой по основному каналу связи, работа устройства продолжается, при этом проверяется наличие ошибки или ее отсутствие в кодовой комбинации, принятой по дополнительному каналу связи, Для этого она подается на кодопреобразователь 70. Это производится следующим образом. После обнаружения ошибки в кодовой комбинации, принятой по основному каналу связи, на выходе 15 регистра 12 появляется сигнал (см. фиг. 3, диагр. е), который поступает на вход тактовой частоты 69 регистра 64, а через второй вход 11 схемы ИЛИ 7 и ее выход - на фазирующий

вход 23 распределителя 22. При этом запускается распределитель 22, производится считывание кодовой комбинации с регистра 64 на кодопреобразователь 70 и одновременно ее информационные импульсы через

0 выходы 66(1)-66(т) регистра 64 поступают на регистр 56, а проверочные импульсы через выходы 67(1)-67(k) регистра 64 - на регистр 60.

Информационные импульсы на кодоп5 реобразователь 70 поступают следующим образом: с выходов 66(1)-66(т) регистра 64 через вторые входы 43 схем ИЛИ 40(1)- 40(т), с их выходов 45(1)-45(т) на регистр 52.

0 Проверочные импульсы считываются следующим образом: с выходов 67(1)-67(k) регистра 64 через входы 43 схем ИЛИ 46(1)-46(k), с их выходов 51(1)-51(к) на регистр 52. С регистра 52 кодовая комбина5 ция дополнительного канала связи считывается на кодопреобразователь 70 тактовыми импульсами с распределителя 22. При отсутствии ошибки в кодовой комбинации, потребителю выдается ее инфор0 мационная часть, а все элементы устройства устанавливаются в исходное состояние.

При обнаружении ошибки сброс элементов в исходное состояние не производится и с очередным тактовым импульсом

5 на выходе 16 регистра 12 появляется сигнал, который поступает на считывающий вход 34 регистра 32, считывающий вход 62 регистра 60, а через вход 9 схемы ИЛИ 7 и ее выход - на фазирующий вход 23 распределителя

0 22. При этом запускается распределитель 22, и на кодопреобразователь 70 считывается первая дополнительная кодовая комбинация, образованная из информационных импульсов кодовой комбинации, принятой по основно5 му каналу связи и проверочных импульсов кодовой комбинации, принятой по дополнительному каналу связи.

Информационные импульсы считываются следующим образом: с выходов 35 ре0 гистра 32 через входы 42 схем ИЛИ 40(1)-40(т), с их выходов 45 на регистр 52.

Проверочные импульсы этой дополнительной кодовой комбинации считываются с выходов 63(1)-63(k) регистра 60 через вхо5 ды 50 схем ИЛИ 46(1)-46(k) и их выходы 51 на регистр 52.

С регистра 52 через его выход 54 первая дополнительная комбинация последовательно считывается на кодопреобразователь 70. При отсутствии ошибок в этой

ного элемента ИЛИ, к четвертому входу которого подключен первый выход регистра, со считывающим входом третьего параллельного регистра, со считывающим входом второго параллельного регистра и с третьим выходом регистра, второй выход которого подключен к второму входу основного элемента ИЛИ, первый вход которого соединен с первым выходом первого циклового распределителя, с информационным входом регистра, к тактовому входу которого подключен второй выход первого циклового распределителя, и со считывающим входом регистра памяти основной информации, выходы которого подключены к информационным входам первого и второго параллельных регистров и к первым входам соответствующих дополнительных элементов ИЛИ, вторые входы которых соединены с выходами первого и второго параллельных регистров, а выходы дополнительных элементов ИЛИ подключены к информационным входам регистра с параллельной записью и последовательным считыванием, тактовый вход которого соединен с первым выходом вто3tрого циклового распределителя, к входу которого подключен выход основного элемента ИЛИ, и с первым входом кодопреобразователя, второй и третий входы которого соединены соответственно с вторым выходом второго циклового распределителя и с выходом регистра с параллельной записью и последовательным считыванием, при этом второй выход первого циклового распределителя подключен к тактовым входам регистра памяти основной информации и регистра памяти дополнительной информации, выходы которого соединены с информационными входами

третьего и четвертого параллельных регистров и с третьими входами соответствующих дополнительных элементов ИЛИ, к четвертым входам которых подключены выходы третьего и четвертого параллельных регистров, причем считывающие входы первого и четвертого параллельных регистров соединены с вторым выходом регистра, первый выход которого подключен к считывающему входу регистра памяти дополнительной информации.

Ю

фиъ. 1

2 aft

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ГРУППОВЫХ КОДОВ | 1990 |

|

RU2025049C1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Устройство определения конца блока циклического кода | 1987 |

|

SU1515381A2 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

Использование: .обеспечение приема информации по симплексным или полудуплексным каналам связи. Сущность изобретения: устройство содержит m дополнительных элементов ИЛИ, k дополнительных элементов ИЛИ, один элемент И, один основной элемент ИЛИ, один регистр, один кодопреобразователь, один регистр с параллельной записью и последовательным считыванием, один регистр памяти основной информации, два цикловых распределителя, четыре параллельных регистра, один регистр памяти дополнительной информации. Увеличение объема принимаемой информации достигается за счет увеличения вероятности приема сообщения при наличии искажений в канале связи.

t-C909iL

5 °

| Устройство для приема дискретной информации | 1974 |

|

SU517172A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-09-07—Публикация

1990-01-02—Подача