Фи.1

Изобретение относится к вычислительной технике и предназначено для применения в цифровых вычислительных машинах, их памяти, устройствах обмена информации, в устройствах шумопонижения цифровой звуКО-, видеозаписи и воспроизведения.

Целью изобретения является расширение функциональных возможностей за счет формирования остатка по контрольному основанию.

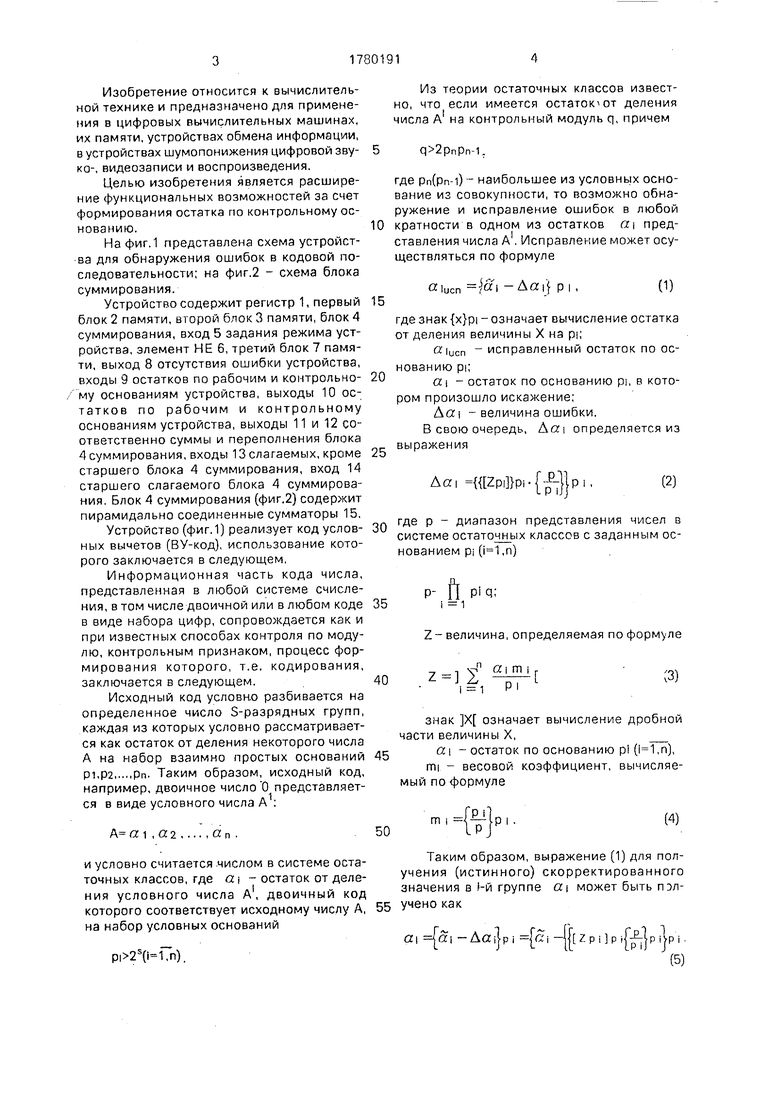

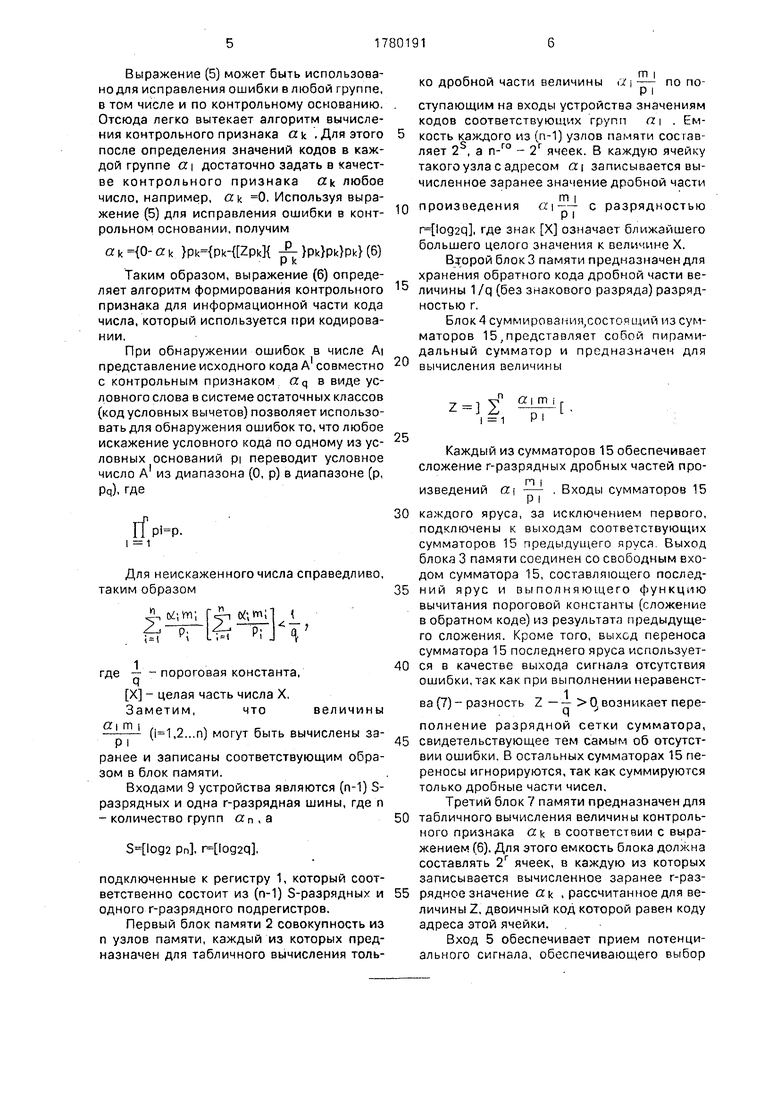

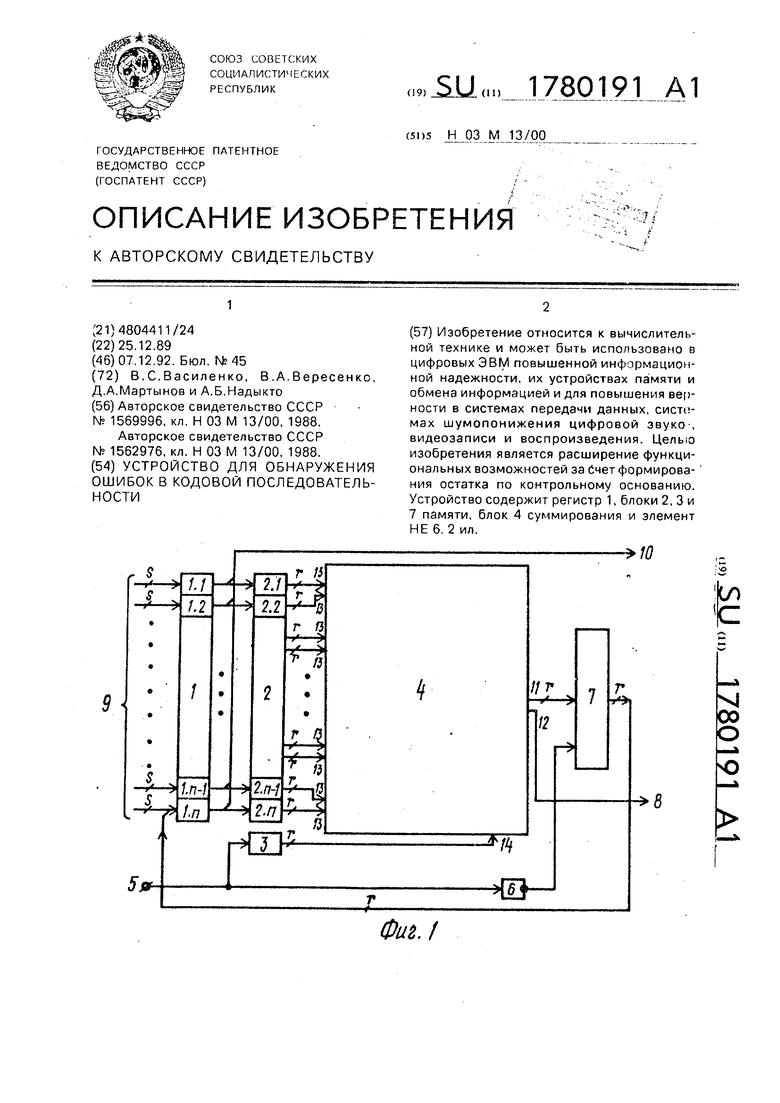

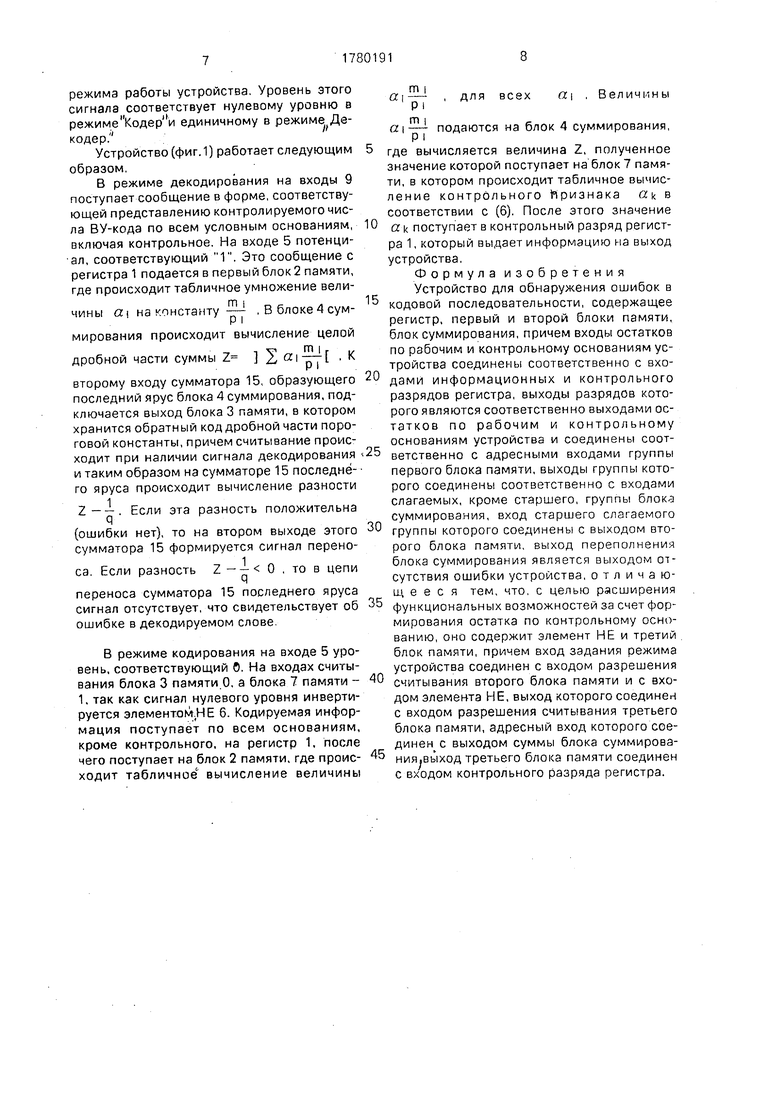

На фиг.1 представлена схема устройства для обнаружения ошибок в кодовой последовательности; на фиг.2 - схема блока суммирования.

Устройство содержит регистр 1, первый блок 2 памяти, второй блок 3 памяти, блок 4 суммирования, вход 5 задания режима устройства, элемент НЕ 6, третий блок 7 памяти, выход 8 отсутствия ошибки устройства, входы 9 остатков по рабочим и контрольному основаниям устройства, выходы 10 остатков по рабочим и контрольному основаниям устройства, выходы 11 и 12 соответственно суммы и переполнения блока 4 суммирования, входы 13 слагаемых, кроме старшего блока 4 суммирования, вход 14 старшего слагаемого блока 4 суммирования. Блок 4 суммирования (фиг.2) содержит пирамидально соединенные сумматоры 15.

Устройство (фиг.1) реализует код условных вычетов (ВУ-код), использование которого заключается в следующем.

Информационная часть кода числа, представленная в любой системе счисления, в том числе двоичной или в любом коде в виде набора цифр, сопровождается как и при известных способах контроля по модулю, контрольным признаком, процесс формирования которого, т.е. кодирования, заключается в следующем.

Исходный код условно разбивается на определенное число S-разрядных групп, каждая из которых условно рассматривается как остаток от деления некоторого числа А на набор взаимно простых оснований Р1,р2,...,рп. Таким образом, исходный код, например, двоичное число О представляется в виде условного числа А ;

А а 1, а 2

On

и условно считается .числом в системе остаточных классов, где «1 - остаток от деления условного числа А, двоичный код которого соответствует исходному числу А, на набор условных оснований

),

Из теории остаточных классов известно, что если имеется ocтaтoк oт деления числа А на контрольный модуль q, причем

5q 2pnpn-l.

где pn(pn-i) - наибольшее из условных основание из совокупности, то возможно обнаружение и исправление ошибок в любой 10 кратности в одном из остатков ai представления числа А . Исправление может осуществляться по формуле

«lucn |«1 - Да)} р I,

(1)

где знак {x}pi - означает вычисление остатка от деления величины X на pi;

исправленный остаток по основанию PI;

о; i - остаток по основанию pi, в котором произошло искажение;

Да| - величина ошибки. В свою очередь, Acti определяется из выражения

Aai ,

(2)

oQ где р - диапазон представления чисел в системе остаточн ых классов с заданным основанием Pi (,n)

р- И pi q;

i 1

Z-величина, определяемая по формуле

ai m i

lZ

(3)

1 PI

i - 1

знак X означает вычисление дробной

части величины X,

/15а - остаток по основанию р1 (,п),

mi - весовой коэффициент, вычисляемый по формуле

50 (

(4)

Таким образом, выражение (1) для получения (истинного) скорректированного значения в -й группе а может быть пзлучено как

а ai i р i р Яр i.

(5) Выражение (5) может быть использовано для исправления ошибки в любой группе, в том числе и по контрольному основанию. Отсюда легко вытекает алгоритм вычисления контрольного признака ctk .Для этого после определения значений кодов в каждой группе а достаточно задать в качестве контрольного признака «k любое число, например, «k 0, Используя выражение (5) для исправления ошибки в контрольном основании,получим а k {0- а k }pk {pk-{ ZpkK - }pk}pk}pk} (6) Таким образом, выражение (6) определяет алгоритм формирования контрольного признака для информационной части кода числа, который используется при кодировании. При обнаружении ошибок в числе At представление исходного кода А совместно с контрольным признаком (Хц в виде условного слова в системе остаточных классов (код условных вычетов) позволяет использовать для обнаружения ошибок то, что любое искажение условного кода по одному из условных оснований PI переводит условное число А из диапазона (О, р) в диапазоне (р, Pq), где . Для неискаженного числа справедливо, таким образом 4. 0 1. --;( где --пороговая константа, X - целая часть числа X, Заметим,чтовеличины Of I ГП i ., , , - (,2...п могут быть вычислены заранее и записаны соответствующим образом в блок памяти. Входами 9 устройства являются (п-1) Sразрядных и одна г-разрядная шины, где п - количество групп огп,а РП, P log2q, подключенные к регистру 1, который соответственно состоит из (п-1) S-разрядных и одного г-разрядного подрегистров. Первый блок памяти 2 совокупность из п узлов памяти, каждый из которых предназначен для табличного вычисления толь, mi ко дробной части величины а, - по поступающим на входы устройства значениям кодов соответствующих групп а . Емкость каждого из (п-1) узлов памяти составляет 2, а п- - 2 ячеек. В каждую ячейку такого узла с адресом ai записывается вычисленное заранее значение дробной части m I «1- с разрядностью произведения p log2q, где знак X означает ближайшего большего целого значения к величине X. Второй блок 3 памяти предназначен для хранения обратного кода дробной части величины 1 /q (без знакового разряда) разрядностью г. Блок 4 суммирования состоящий из сумматоров 15,представляет собой пирамидальный сумматор и предназначен для вычисления величины Каждый из сумматоров 15 обеспечивает сложение г-разрядных дробных частей проп i изведений а - , Входы сумматоров 15 каждого яруса, за исключением первого, подключены к выходам соответствующих сумматоров 15 предыдущего яруса. Выход блока 3 памяти соединен со свободным входом сумматора 15, составляющего последНИИ ярус и выполняющего функцию вычитания пороговой константы (сложение в обратном коде) из результата предыдущего сложения. Кроме того, выход переноса сумматора 15 последнего яруса исгюльзуется в качестве выхода сигнала отсутствия ошибки, так как при выполнении неравенства (7)-разность Z - - О, возникает переполнение разрядной сетки сумматора, свидетельствующее тем самым об отсутствии ошибки. В остальных сумматорах 15 переносы игнорируются, так как суммируются только дробные части чисел. Третий блок 7 памяти предназначен для табличного вычисления величины контрольного признака а k в соответствии с выражением (6). Для этого емкость блока должна составлять 2 ячеек, в каждую из которых записывается вычисленное заранее г-разрядное значение cjk , рассчитанное для величины Z, двоичный код которой равен коду адреса этой ячейки. . Вход 5 обеспечивает прием потенциального сигнала, обеспечивающего выбор режима работы устройства. Уровень этого сигнала соответствует нулевому уровню в режиме Кодер и единичному в режиме Устройство (фиг. 1) работает следующим образом. В режиме декодирования на входы 9 поступает сообщение в форме, соответствующей представлению контролируемого числа ВУ-кода по всем условным основаниям, Езключая контрольное. На входе 5 потенциал, соответствующий 1. Это сообщение с регистра 1 подается в первый блок 2 памяти, где происходит табличное умножение велиm I Г-, л чины а на константу - , В блоке 4суммирования происходит вычисление целой -. ГП I г ,, дробной части суммы Z J 2/ сс К второму входу сумматора 15, образующего последний ярус блока 4 суммирования, подключается выход блока 3 памяти, в котором хранится обратный код дробной части пороговой константы, причем считывание происходит при наличии сигнала декодирования и таким образом на сумматоре 15 последнёго яруса происходит вычисление разности 1 Z. Если эта разность положительна (ошибки нет), то на втором выходе этого сумматора 15 формируется сигнал переноса. Если разность Z О , то в цепи переноса сумматора 15 последнего яруса сигнал отсутствует, что свидетельствует об ошибке в декодируемом слове. В режиме кодирования на входе 5 уровень, соответствующий 0. На входах считывания блока 3 памяти О, а блока 7 памяти 1, так как сигнал нулевого уровня инвертируется элементом.НЕ 6. Кодируемая информация поступает по всем основаниям, кроме контрольного, на регистр 1. после чего поступает на блок 2 памяти, где происходит табличное вычисление величины Величины для всех подаются на блок 4 суммирования. где вычисляется величина Z, полученное значение которой поступает на блок 7 памяти, в котором происходит табличное вычисление контрольного Признака «k в соответствии с (6). После этого значение а k поступает в контрольный разряд регистра 1, который выдает информацию на выход устройства. Формула изобретения Устройство для обнаружения ошибок в кодовой последовательности, содержащее регистр, первый и второй блоки памяти, блок суммирования, причем входы остатков по рабочим и контрольному основаниям устройства соединены соответственно с входами информационных и контрольного разрядов регистра, выходы разрядов которого являются соответственно выходами остатков по рабочим и контрольному основаниям устройства и соединены соответственно с адресными входами группы первого блока памяти, выходы группы которого соединены соответственно с входами слагаемых, кроме старшего, группы блока суммирования, вход старшего слагаемого группы которого соединены с выходом второго блока памяти, выход переполнения блока суммирования является выходом отсутствия ошибки устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования остатка по контрольному основанию, они содержит элемент НЕ и третий . блок памяти, причем вход задания режима устройства соединен с входом разрешения считывания второго блока памяти и с входом элемента НЕ, выход которого соединен с входом разращения считывания третьего блока памяти, адресный вход которого соединен с выходом суммы блока суммирования,выход третьего блока памяти соединен с входом контрольного разряда регистра.

hj

nPVi

in -1У5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1837293A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК В ПОЛИНОМИАЛЬНОЙ СИСТЕМЕ КЛАССОВ ВЫЧЕТОВ С ИСПОЛЬЗОВАНИЕМ ПСЕВДООРТОГОНАЛЬНЫХ ПОЛИНОМОВ | 2005 |

|

RU2294529C2 |

| Устройство кодирования | 1989 |

|

SU1762412A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1562976A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПЕРЕПОЛНЕНИЯ ДИНАМИЧЕСКОГО ДИАПАЗОНА, ОПРЕДЕЛЕНИЯ ОШИБКИ И ЛОКАЛИЗАЦИИ НЕИСПРАВНОСТИ ВЫЧИСЛИТЕЛЬНОГО КАНАЛА В ЭВМ, ФУНКЦИОНИРУЮЩИХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2011 |

|

RU2483346C1 |

| УСТРОЙСТВО СПЕКТРАЛЬНОГО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В КОДАХ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ | 2005 |

|

RU2301441C2 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых ЭВМ повышенной информационной надежности, их устройствах памяти и обмена информацией и для повышения ве[)- ности в системах передачи данных, системах шумопонижения цифровой звуко-, видеозаписи и воспроизведения. Целью изобретения является расширение функциональных возможностей за Счет формирования остатка по контрольному основанию. Устройство содержит регистр 1, блоки 2, 3 и 7 памяти, блок 4 суммирования и элемент НЕ 6.2 ил.

th-ptU

П

.// rz

9аг.г

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1562976A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-07—Публикация

1989-12-25—Подача