TOfffft

Вход (сдвиг)

f /OffC

i

(Л

со

00 05

1;Л

ffff

Устройство относится к импульсной технике и может использоваться в составе контрольно-измерительных и управляющих систем.

Цель изобретения - повышение быстродействия и точности устройства.

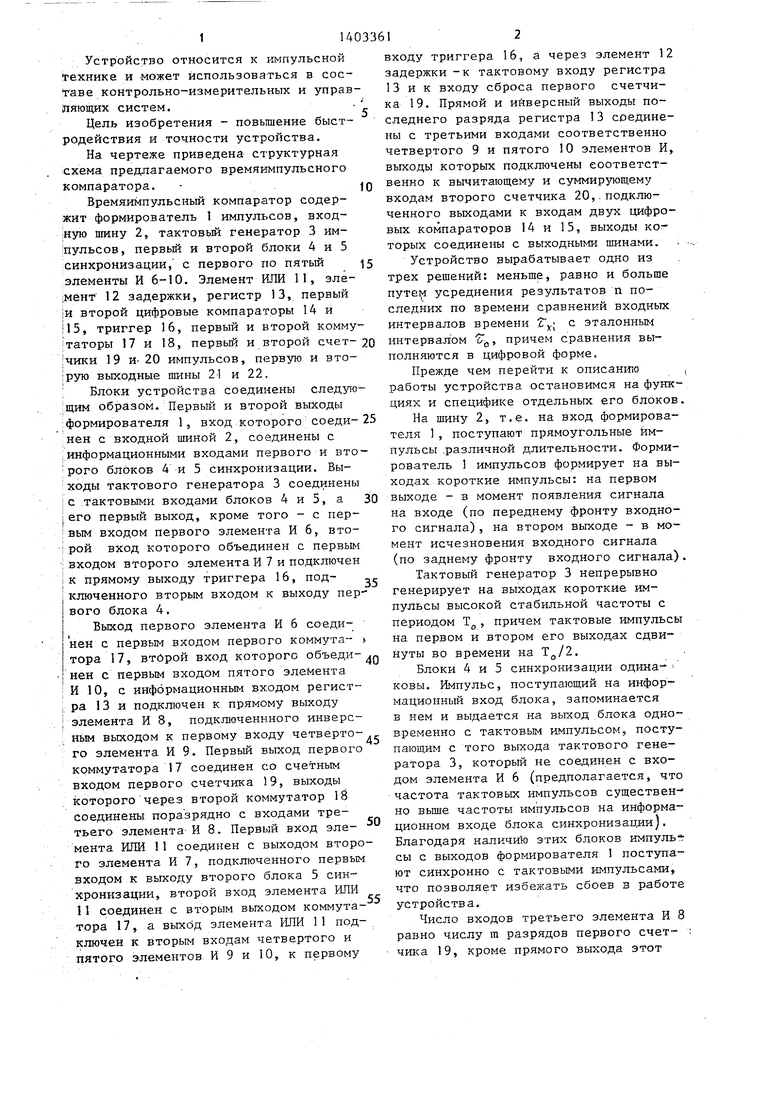

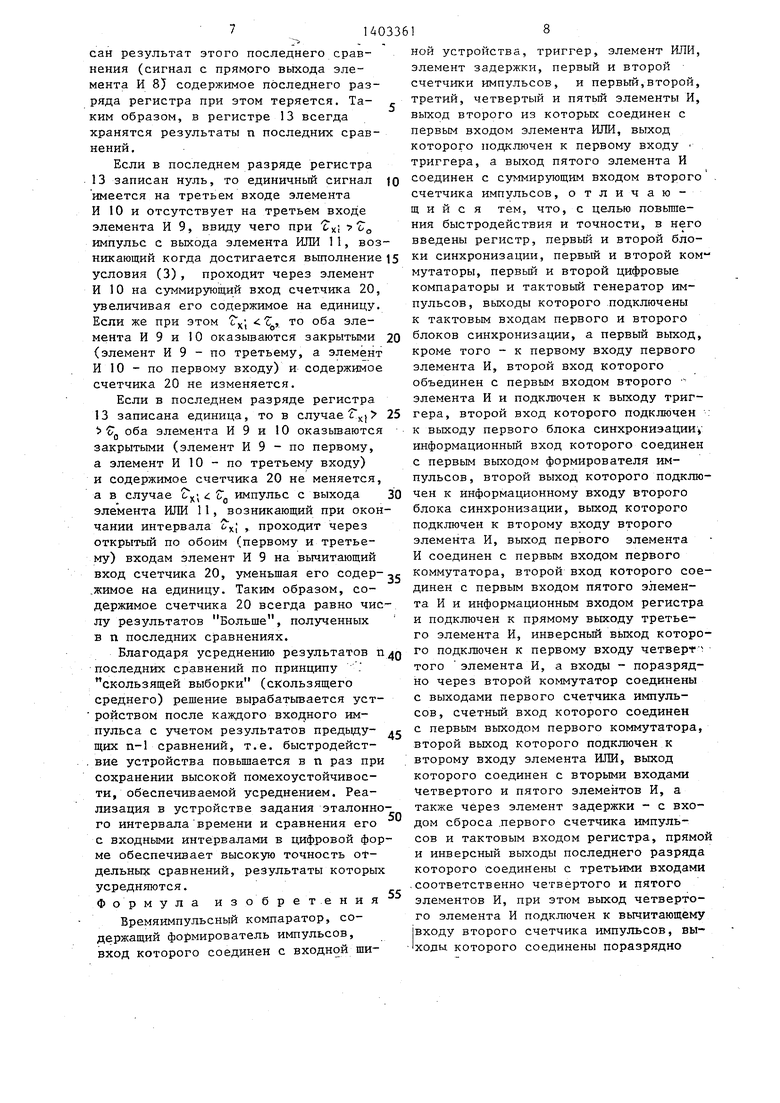

На чертеже приведена структурная схема предлагаемого времяимпульсного компаратора.

Времяимпульсный компаратор содержит формирователь 1 импульсов, вход- |ную шину 2, тактовьй генератор 3 им- ;пульсов, первый и второй блоки 4 и 5 синхронизации, с первого по пятый элементы И 6-10. Элемент ИЛИ 11, элё- :мент 12 задержки, регистр 13, первый |и второй цифровые компараторы 14 и ;15, триггер 16, первый и второй комму |таторы 17 и 18, первый и второй счет|чики 19 и- 20 импульсов, первую и вто- ;рую выходные шины 21 и 22. . Блоки устройства соединены следую щим образом. Первый и второй выходы ;формирователя 1, вход которого соеди- ней с входной шиной 2, соединены с ;информационными входами первого и вто рого блоков 4 и 5 синхронизации. Выходы тактового генератора 3 соединены I с .тактовьми входами блоков 4 и 5, а iего первый выход, кроме того - с пер- iвым входом первого элемента И 6, вто- ;рой вход которого объединен с первым : входом второго элемента И 7 и подключен :к прямому выходу триггера 16, под- ключенного вторым входом к выходу первого блока 4,

Выход первого элемента И 6 соединен с первым входом первого коммута- тора 17, второй вход которого объеди| нен с первым входом пятого элемента I И 10, с информационным входом регист- ; ра 13 и подключен к прямому выходу I элемента И 8, подключеннного инверс- ньм выходом к первому входу четвертого элемента И 9. Первый выход первого коммутатора 17 соединен со счетным входом первого счетчика 19, выходы которого через второй коммутатор 18 соединены поразрядно с входами третьего элемента-И 8. Первый вход элемента ИЛИ 11 соединен с выходом второго элемента И 7, подключенного первым входом к выходу второго блока 5 синхронизации, второй вход элемента ИЛИ 11 соединен с вторым выходом коммутатора 17, а выход элемента ИЛИ 11 подключен к вторым входам четвертого и пятого элементов И 9 и 10, к первому

входу триггера 16, а через элемент 12 задержки -к тактовому входу регистра 13 и к входу сброса первого счетчика 19. Прямой и ийверсный выходы последнего разряда регистра 13 соединены с третьими входами соответственно четвертого 9 и пятого 10 элементов И, выходы которых подключены соответственно к вычитающему и суммирующему входам второго счетчика 20,.подключенного выходами к входам двух цифровых компараторов 14 и 15, выходы которых соединены с выходными шинами. Устройство вырабатывает одно из трех решений: меньше, равно и больше путеь усреднения результатов п последних по времени сравнений входных интервалов времени Т

Xi

с эталонным

0 5 0 с Q .. 0

5

полняются в цифровой форме.

Прежде чем перейти к описашггО , работы устройства остановимся на функциях и специфике отдельных его блоков.

На шину 2, т.е. на вход формирователя 1, поступают прямоугольные импульсы .различной длительности. Формирователь 1 импульсов формирует на выходах короткие импульсы: на первом выходе - в момент появления сигнала на входе (по переднему фронту входного сигнала), на втором выходе - в момент исчезновения входного сигнала (по заднему фронту входного сигнала).

Тактовый генератор 3 непрерывно генерирует на выходах короткие импульсы высокой стабильной частоты с периодом Тд, причем тактовые импульсы на первом и втором его выходах сдвинуты во времени на .

Блоки 4 и 5 синхронизации одина- ковы. Импульс, поступающий на информационный вход блока, запоминается в нем и выдается на выход блока одновременно с тактовым импульсом, поступающим с того выхода тактового генератора 3, который не соединен с входом элемента И 6 (предполагается, что частота тактовых импульсов существен- но вьш1е частоты импульсов на информационном входе блока синхронизации). Благодаря наличие этих блоков импуль- сы с выходов формирователя 1 поступают синхронно с тактовыми импульсами, что позволяет избежать сбоев в работе устройства.

Число входов третьего элемента И 8 равно числу m разрядов первого счет- : чика 19, кроме прямого выхода этот

314

элемент имеет также инверсный выход, сигнал на котором является логическим отрицанием сигнала на прямом выходе.

Элемент 12 задерживает импульсы на короткое время, достаточное для прохождения импульса через элемент И 9 или 10.

Регистр 13 выполнен сдвиговым. Импульс, поступающий на его тактовый вход, смещает содержимое регистра на один разряд вправо,записьшая также в первый (левый) разряд, освобождающийся при сдвиге, логический сигнал, присутствующий в это время на инфор- мационном входе регистра (т.е. на. прямом выходе элемента И 8), число разрядов регистра равно числу п сравнений, результаты которых усредняются при принятии решения.

Цифровой компаратор 14 поддерживает на выходе единичный сигнал только в том случае, когда выполняется условие

,,(1)

где К - содержимое счетчика 20, поступающее на одну из двух групп входов компараторов 14 и 15;

К - число, устанавливаемое на второй группе входов,компаратора 14 (это число может устанавливаться с помощью - специального блока, не показанного на чертеже, либо поступать от внешнего устройства) .

Цифровой компаратор 15 поддерживает на выходе единичный сигнал только

При вьтолнении условия

,(2)

где К - число, установленное на второй группе входов компаратора 15 аналогично числу К на входах компаратора 14. Первый коммутатор 17 передает импульс, поступающий на его первый вход либо на первый выход, если на втором входе коммутатора 17 отсутствует единичный управляющий сигнал, либо на второй выходу - если указанный сигнал присутствует.

Второй коммутатор 18 представляет собой m двухпозидионньк переключателей, он позволяет подключить -й вход элемента И 8 ( ,2,. .. ,т) либо к пря мому, либо к инверсному выходу i-ro разряда счетчика 19, и, следовательно обеспечить появление единичного сигна

1

ла на прямом выходе элемента И 8 при

любом наперед заданном значении NO содержимого N счетчика 19, т.е. при выполнении условия

. (3)

Счетчик 20 выполнен реверсивным, его емкость должна быть достаточной для записи числа п.

Принцип действия устройства состоит в том, что длительности входных интервалов времени (,2,...,) сравниваются в цифровой форме с заданной (эталонной) длительностью , результат каждого сравнения (Меньше - О, Больше - 1) записьша- ется в первый разряд п-разрядного регистра 13, содержимое которого сдвигется на один разряд вправо после каждого сравнения, с помощью этого регистра в счетчике 20 формируется число К, равное количеству результатов Больше, полученных в п последних по времени сравнениях. Это число сопоставляется в компараторах 14 и 15 с заранее заданными нижней и границами К и К , , при выполнении условия (1) принимается решение Меньше, при выполнении уело-- ВИЯ (2) - решение Больше , если ни одно из этих ..условий не вьшолня- ется, т.е. выполняется условие

о

5

0

.

0

5

,

(4)

принимается решение Равно.

Таким образом, решение вырабатьта- ется по скользящей выборке - по результатам п последних во времени сравнений, оно может измениться после каждого очередного сравнения; (А не только после п сравнений, как в известном устройстве).

Устройство работает следующим образом.

В исходном состоянии регистр 13, триггер 16, счетчики 19 и 20 установлены в нуль, коммутатор 18 обеспечивает срабатывание элемента И 8 при значении Ыд, соответствующем эталон- ному интервалу о . На вторых группах входов цифровых компараторов 14 и 15 установлены соответственно числа Kj, и К . При этом элемент И 6 закрыт по второму входу, сигнал на прямом выходе элемента И 8 отсутствует, ввиду чего первый вход коммутатора 17 подключен к его вому выходу.

В момент появления сигнала на входной шине 2 устройства формируется ко

5U0336

роткий импульс на первом выходе формирователя 1, .поступающий на информационный вход первого блока 4 синхронизации. Ближайший во времени тактовый , импульс с второго выхода тактового генератора 3, передает этот импульс на выход-блока .е. на второй вход триггера 16, в результате чего появляется единичньгй сигнал на втором ю входе элемента И 6, и тактовые ;пульсы начинают поступать через этот ;элемеут и коммутатор 17 на счетный ;вход первого счетчика 19, открывается

также (по второму входу) второй эле- 15 элемент 12 задержки, сдвинет содержи- мент И 7,мое регистра 13 на один разряд вправо

В момент, когда сигнал на входной шине 2 исчезает, формируется короткий

импульс на втором выходе формироваи возвратит в нуль счетчик 19. По - скольку элементы И 9 и 10 при этом закрыты по второму входу, содержимое теля 1. Обозначим через N число так- 20 счетчика 20 не изменится, а в первом товых импульсов, поступивших на пер- разряде регистра 13 будет записан ;вый вход элемента 6 (следовательно нуль, кодирующий результат сравнения jlHa счетный вход счетчика 19) в интер- Меньше (поскольку сигнал на инфор- :вале времени С, между импульсами на мационном входе регистра, т.е. на первом и на втором выходах формирова- 25 прямом выходе элемента И 8 при этом теля 1. Если с,д, то (так отсутствует). :как NJ С,/Т) , и, следовательно, после некоторого тактового импульса будет достигнуто равенство (3). В ре- зультате появится сигнал на прямом выходе третьего элемента И 8 и очередной тактовый импульс пройдет теАналогично будут обработаны входные интервалы о х - хп- - Р зультате в счетчике 20 будет сформи- 30 ровано число К, равное количеству результатов Больше среди п результатов проведенных сравнений. Обозначим сигналы на выходах первого и второго цифровых компараторов 14 и 15

Аналогично будут обработаны входные интервалы о х - хп- - Р зультате в счетчике 20 будет сформи- 30 ровано число К, равное количеству результатов Больше среди п результатов проведенных сравнений. Обозначим сигналы на выходах первого и вто рого цифровых компараторов 14 и 15

;перь не на первый, а на второй выход

коммутатора 17, поступая через ИЛИ 11 на первый (нулевой) вход (на выходных шинах 21 и 22 устройст|Триггера 16 и закрывая тем самым эле- ва) через S, и S.

|Менты И 6 и 7. Этот же импульс прой1дет через пятый элемент И 10 (поскольЕсли вьтолНяется условие (1), то получаем сочетание выходных сигналов

|ку в последнем разряде регистра 13 за- , , кодирующее решение Мень- лисан нуль, т.е. единичный сигнал ше.

рассматриваемом случае о , -, ъ через элемент И 7 не проходит (триггер 16 уже установлен в нуль).

)(, Гд, то выполнение условия (3) достигнуто не будет, ц импульс с второго выхода формирователя 1 (в момент окончания интервала 2 х, ) , передаваемый тактовым импульсом на выход блока 5 синхронизации, пройдет через открытый элемент И 7 и элемент ИЛИ 11. Этот импульс возвратит триггер нуль, закрывая тем самым элемент И 6, а затем, пройдя через

и возвратит в нуль счетчик 19. По - скольку элементы И 9 и 10 при этом закрыты по второму входу, содержимое счетчика 20 не изменится, а в первом разряде регистра 13 будет записан нуль, кодирующий результат сравнения Меньше (поскольку сигнал на инфор- мационном входе регистра, т.е. на прямом выходе элемента И 8 при этом отсутствует).

Аналогично будут обработаны входные интервалы о х - хп- - Р зультате в счетчике 20 будет сформи- ровано число К, равное количеству результатов Больше среди п результатов проведенных сравнений. Обозначим сигналы на выходах первого и второго цифровых компараторов 14 и 15

Если вьтолНяется условие (1), то получаем сочетание выходных сигналов

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Устройство для определения отношения двух напряжений | 1983 |

|

SU1151994A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

Изобретение может быть использовано в составе контрольно-измерительных и управляющих систем. Время- импульсный компаратор содержит формирователь 1 импульсов, входную шину 2, триггер 16, злемент ИЛИ 11, элемент 12 задержки, счетчики 19, 20 импульсов, элементы И 6-10, регистр 13, блоки 4,5 синхронизации, коммутаторЬг 17, 18, цифровые компараторы 14,15, тактовый генератор 3 импульсов, выходные шины 21, 22. Времяимпульсный компаратор имеет повышенные быстродействие и точность, 1 ил.

сутствует на третьем входе элемента И 10) на суммирующий вход второго счетчика 20, а затем, пройдя через элемент. 12 задержки, сдвинет содержимое регистра 13 на один разряд вправо, запишет в его первый (левый) разряд единицу (сигнал на прямом выходе элемента И 8 -, кодирующий результат данного сравнения) и устаноЕсли выполняется условие (2), то получаем сочетание , 84 кодирующее решение Больше.

Если вьтолняется условие (-4) име- 45 ем сочетание S,0, , кодирующее решение Равно Результаты всех п сравнений хранятся при этом в регистре 13, причем они размещены в нем справа налево в вит в нуль счетчик 19. Таким образом, gQ порядке получения - результат первого, результат Больше первого сравнения самого старого сравнения записан в будет записан в первый разряд регист- п-ом последнем разряде, результат

последнего сравнения (п-го)- в первом (левом) разряде.

После выполнения очередного срав- , нения содержимое регистра 13 будет сдвинуто аналогично описанному на один разряд вправо,а в освобождающийся при этом левый разряд будет запира 13, в счетчике 20 также будет записана единица - количество результатов Больше, полученных в п послед- Vg них сравнениях (пока проведено только одно сравнение). Импульс, формируемый на выходе блока 5 синхронизации по окончании интервала сГ, .в

ан результат этого последнего сравения (сигнал с прямого выхода элеента И 8) содержимое последнего разряда регистра при этом теряется. Таим образом, в регистре 13 всегда ранятся результаты п последних сравений.

Если в последнем разряде регистра 13 записан нуль, то единичный сигнал имеется на третьем входе элемента И 10 и отсутствует на третьем входе элемента И 9, ввиду чего при Г о импульс с выхода элемента ИЛИ 11, возникающий когда достигается вьтолнение условия (3), проходит через элемент И 10 на суммирующий вход счетчика 20, увеличивая его содержимое на единицу, Если же при этом Гх; Z, то оба элемента И 9 и 10 оказываются закрытыми (элемент И 9 - по третьему, а элемент И 10 - по первому входу) и содержимое счетчика 20 не изменяется.

Если в последнем разряде регистра 13 записана единица, то в случае Г,,j Од оба элемента И 9 и 10 оказьшаются закрытыми (элемент И 9 - по первому, а элемент И 10 - по третьему входу) и содержимое счетчика 20 не меняется, а в случае Г импульс с выхода элемента ИЖ 11, возникающий при окон чании интервала , проходит через открытый по обоим (первому и третьему) входам элемент И 9 на вычитающий вход счетчика 20, уменьшая его содер- жимое на единицу. Таким образом, содержимое счетчика 20 всегда равно чис- лу результатов Больше, полученных в п последних сравнениях.

Благодаря усреднению результатов п последних сравнений по принципу скользящей выборки (скользящего среднего) рещение вырабатывается устройством после каждого входного импульса с учетом результатов предыдущих п-1 сравнений, т.е, быстродействие устройства повьппается в п раз при сохранении высокой помехоустойчивости, обеспечиваемой усреднением. Реализация в устройстве задания эталонного интервала времени и сравнения его с входными интервалами в цифровой форме обеспечивает высокую точность отдельных сравнений, результаты которых усредняются. Формула изобретения

Времяимпульсный компаратор, содержащий фо{)мирователь импульсов, вход которого соединен с входной ши0

5

0

5

0

5

0

5

0

5

ной устройства, триггер, элемент ИЛИ, элемент задержки, первый и второй счетчики импульсов, и первый,второй, третий, четвертый и пятьш элементы И, выход второго из которых соединен с первым входом элемента ИЛИ, выход которого подключен к первому входу триггера, а выход пятого элемента И соединен с суммирующим входом второго счетчика импульсов, отличающийся тем, что, с целью повьппе- ния быстродействия и точности, в него введены регистр, первый и второй блоки синхронизации, первый и второй ком мутаторы, первый и второй цифровые компараторы и тактовый генератор импульсов, выходы которого подключены к тактовым входам первого и второго блоков синхронизации, а первый выход, кроме того - к первому входу первого элемента И, второй вход которого объединен с первым входом второго - элемента И и подключен к выходу триггера, второй вход которого подключен к выходу первого блока синхронизации информационный вход которого соединен с первым выходом формирователя импульсов, второй выход которого подключен к информационному входу второго блока синхронизации, выход которого подключен к второму в.ходу второго элемента И, выход первого элемента И соединен с первым входом первого коммутатора, второй вход которого соединен с первым входом пятого элемента И и информационным входом регистра и подключен к прямому выходу третьего элемента И, инверсный выход которого подключен к первому входу четверт того элемента И, а входы - поразрядно через второй коммутатор соединены с выходами первого счетчика импульсов, счетньй вход которого соединен с первым выходом первого коммутатора, второй выход которого подключен к второму входу элемента ИЛИ, выход которого соединен с вторыми входами четвертого и пятого элементов И, а также через элемент задержки - с входом сброса .первого счетчика импульсов и тактовым входом регистра, прямой и инверсный выходы последнего разряда которого соединены с третьими входами соответственно четвертого и пятого элементов И, при этом выход четвертого элемента И подключен к вычитающему входу второго счетчика импульсов, выходы которого соединены поразрядно

9140336110

с входами первого и второго цифровых которых соединены с первой и второй компараторов соответственно, выходы выходными шинами соответственно.

| Устройство для селекции импульсных сигналов | 1982 |

|

SU1129727A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Времяимпульсный компаратор | 1982 |

|

SU1081785A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-15—Публикация

1986-11-28—Подача