сл С

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ | 1990 |

|

RU2022346C1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для тренировки операторов | 1989 |

|

SU1714648A1 |

| Устройство для обработки измерительной информации | 1984 |

|

SU1231511A1 |

Изобретение может быть использовано в качестве персонального преобразователя информации в сетях ЭВМ, АСУ, при обмене данными с удаленными терминалами и в других случаях, когда необходима защита информации от неавторизованного чтения при хранении и передаче данных. Цель изобретения - повышение криптостойкости и быстродействия. Устройство содержит блок управления, счетчик, шифраторы и элементы ИЛИ, два узла коммутации, три коммутатора и коммутатор инверсных преобразований. 2 з.п. ф-лы, 2 ил.

Изобретение относится к устройствам преобразования цифровой информации с целью защиты ее от неавторизованного чтения при передаче по каналам связи и хранении на машинных носителях и может быть использовано в сетях ЭВМ, АСУ, при обмене данными с удаленными терминалами и в других случаях, когда возникает необходимость хранения и передачи конфиденциальной информации.

Цель изобретения - повышение криптостойкости и быстродействия.

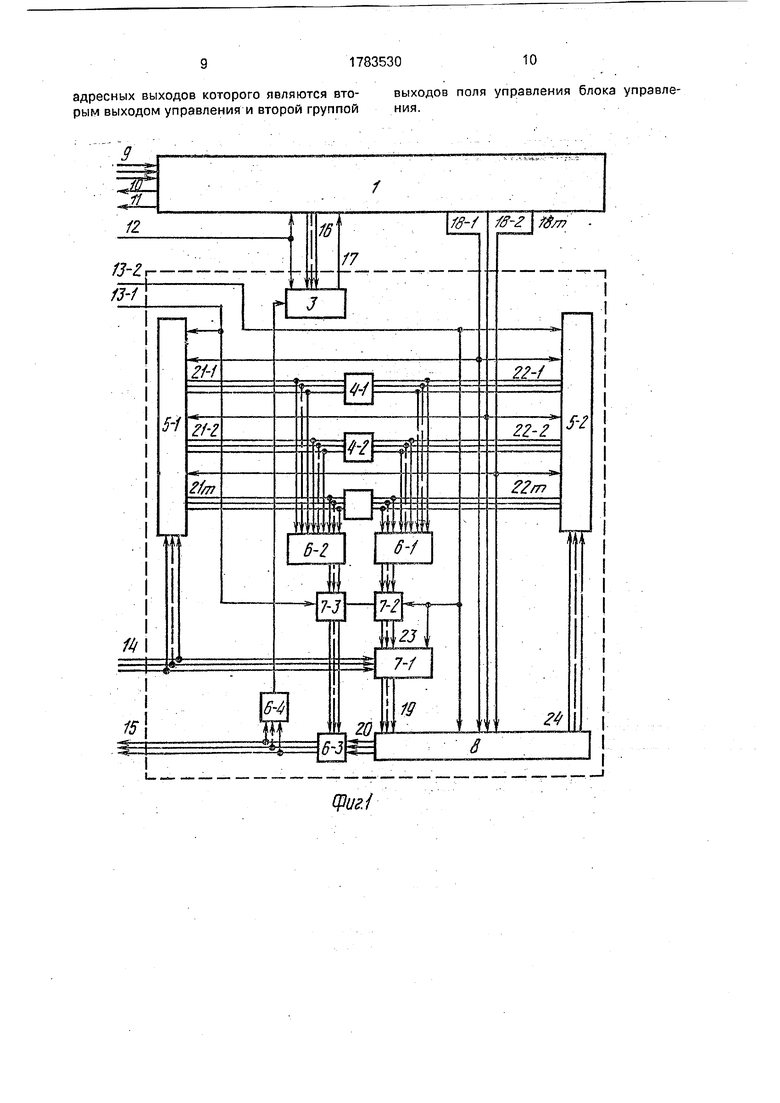

На фиг. 1 и 2 приведена функциональная схема устройства кодирования.

На фиг.1 показаны блок управления 1, блок преобразования информации 2, содержащий счетчик 3, шифраторы 4, узел коммутации 5, элементы ИЛИ 6, коммутаторы 7 и коммутатор инверсных преобразований 8.

В исходном состоянии на выходе блока 1 управления сигналов нет, в коммутаторе

7-1 вход 14 запрещен, а вход 23 соединен с выходом 19, который через коммутатор 8 соединен с его выходом 20, коммутаторы 7-2, 7-3 разрешены, узлы коммутации 5-1, 5-2 запрещены.

При подаче на вход 13-1 сигнала он поступает в узел коммутации 5-1, в котором разрешается вход 14, и на вход коммутаторе 7-3, который запрещается.

Затем поступает код на вход 9 блока 1 управления. После приема полного кода кодирования на его выходе 10 формируется сигнал, поступающий на выход устройства, при этом подача кода на вход 9 запрещается.

Приняв код кодирования, блок 1 управления формирует уставку на выходе 16, поступающую в счетчик 3, а (акже сигнал выбора текущей подпрограммы преобразования на выходе, например, 18-2, поступающие на входы узлов коммутации 5-1, 5-2,

XS

сл

U5 О

в которых разрешаются выходы 21-2, 22-2. Кроме того, сигнал поступает на вход 18-2 коммутатора 8, в котором подготавливается соответствующая подпрограмма инверсных преобразований. Кроме того, поступает сиг- нал готовности на выход 11.

В этом случае сообщения с входа 14 через узел коммутации 5-1 поступают: через группу элементов ИЛИ 6-2 на вход за- прещенного коммутатора 7-3; через шифратор 4-2, в котором искажаются по закону данного шифратора, группу элементов ИЛИ 6-1, коммутатор 7-2 на вход 23 коммутатора 7-1, и с его выхода 19 через коммутатор 8, в котором проходят соответ- ствующие инверсные преобразования, поступают на выход 20, с которого через группу элементов ИЛИ 6-3 подаются на выход 15, а также на вход элемента ИЛИ 6-4.

Признаки сообщений с выхода элемен- та ИЛИ 6-4 поступают на счетный вход счетчика 3, в котором суммируются с уставкой, При переполнении счетчика 3 на его выходе .17 формируется сигнал, поступающий в блок 1 управления, в котором: снимается сигнал готовности с выхода 11; на вход 16 подается новая уставка, которая запоминается в счетчике 3, сигнал с выхода 17 снимается; снимается сигнал с выхода 18-2 и подается на другой выход, например 18-1; подается сигнал готовности на выход 11.

В этом случае сообщения с входа 14 через узел 5-1, его выход 21-1, шифратор 4-1, в котором искажаются по другому закону, группу элементов ИЛИ 6-1, коммутато- ры 7-2, 7-1 поступают на вход 19 коммутатора 8, в котором производятся другие инверсные преобразования, и с его выхода 20 через группу элементов ИЛИ 6-3 поступают на выход 15, а также через эле- мент ИЛИ 6-4 на вход счетчика 3, в котором суммируются с новой уставкой.

Так реализуются прямые преобразования.

После окончания работы сигнал с выхо- да 13-1 снимается, и на вход 12 поступает сигнал сброса, который подается в счетчик 3 и блок 1 обнуляет их, при этом с выходов 10, 11, 18 блока 1 управления сигналы снимаются и устройство возвращается в исход- ное состояние.

При обратных преобразованиях сигнал поступает на вход 13-2 и подается: на вход узла коммутации 5-2, в котором разрешается вход 24; на вход коммутатора 8 инверс- ных преобразований, в котором запрещается выход 20 и разрешается выход 24; на вход коммутатора 7-2 и запрещает его; на вход коммутатора 7-1, в котором выход 19 переключается на вход 14.

Затем на вход 9 подается тот же код, что и при прямых преобразованиях, при этом на выходах 10, 18-2 и 11 формируются сигналы, на вход 16 счетчика 3 поступает та же уставка.

После этого на вход 14 поступают искаженные сообщения, которые через коммутатор 7-1 поступают на вход 19 коммутатора 8, где аналогично проходят инверсные преобразования, и с его выхода 24 через второй узел коммутации 5-2, его выход 22-2 поступают в шифратор 4-2, где реализуются обратные преобразования, после чего чистые сообщения через группу элементов ИЛИ 6-2, коммутатор 7-3, группу элементов ИЛИ 6-3 поступают на выход 15, а признаки таких сообщений подаются на вход счетчика 3, в котором суммируются с уставкой.

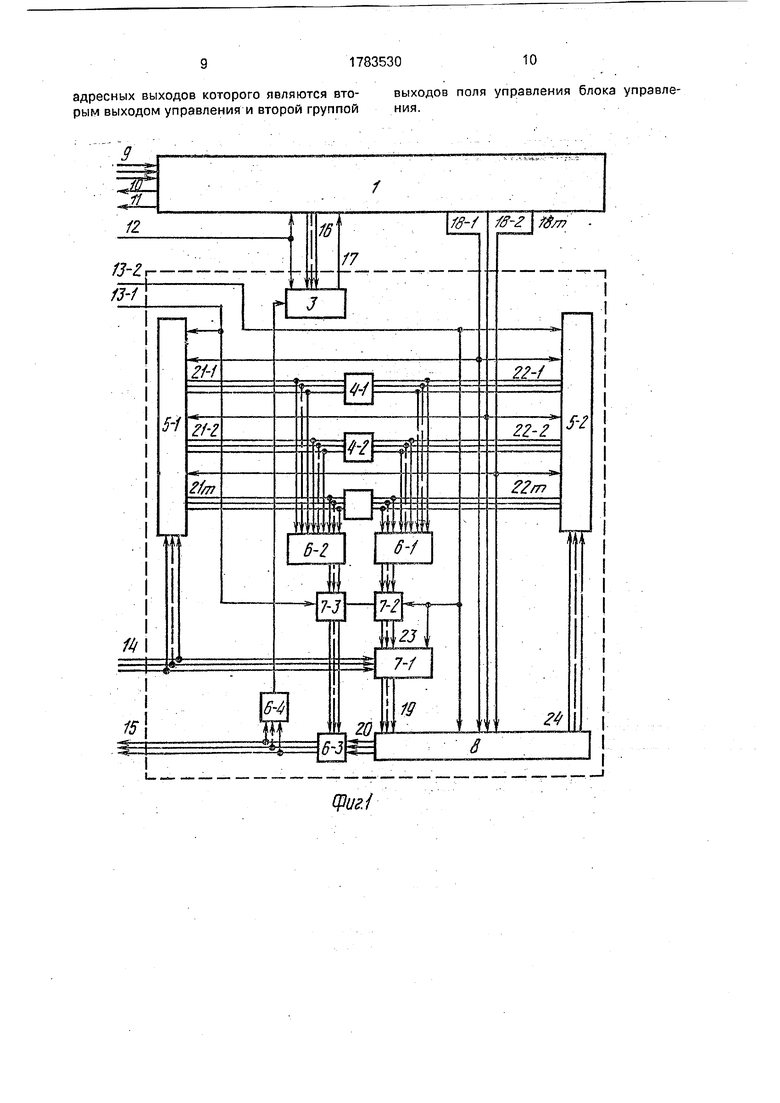

На фиг.2 показан блок 1 управления, содержащий память программ преобразования 25, накопитель подпрограмм 26, формирователь уставок 27, задатчик алгоритма 28, узел ввода подпрограмм 29. При этом адресные входы 9 блока управления являются информационными входами памяти 25 программ преобразования, первые 30, вторые 31 и третьим 32 информационные выходы которой соединены соответственно с входами накопителя 26 подпрограмм, формирователя 27 уставок и установочными входами задатчика 28 алгоритмов, первый выход 36 которого соединен с входом сброса накопителя 26 и входом сдвига памяти 25, управляющий выход 10 которой является первым выходом управления блока и соединен с вторым входом задатчика 28, третий вход 17 которого является входом логического условия блока, первая группа 16 выходов поля управления которого является выходом формирователя 27 уставок, управляющие входы которого соединены с первой группой выходов 35 узла 29 ввода подпрограмм, вторая группа выходов 34 и первая группа входов 33 которого соединена с входами и выходами накопителя 26 подпрограмм, при этом вход сброса блока соединен с входами сброса памяти 25, задатчика 28 и узла 29 ввода подпрограмм, управляющие вход 40 и выход 39 которого соединены соответственно с вторым выходом и четвертым входом задатчика 28 алгоритма, вход 37 продвижения и первый 38, второй 41 выходы продвижения которого соединены соответственно с выходом продвижения и первым, вторым входами продвижения узла 29, управляющий выход 11 и группа адресных выходов 18 которого являются вторым выходом управления и второй группой выходов поля управления блока.

В исходном состоянии сигналов на выходах памяти 25, накопителя 26, формирователя 27, задатчика 28 и узла 29 нет.

Память 25 программ преобразования, после приема на входе 9 полного кода клю- ча, формирует сигнал на выходе 10, поступающий на выход блока, при этом подача кода на вход 9 прекращается, и на вход задатчика 28, в котором передается на выход 36, и поступает на вход сброса накопи- теля 26 и вход продвижения памяти 25.

В этом случае на выходы 30, 31, 32 поступают соответствующие коды, после чего в памяти 25 реализуется операция сдвига, которая необходима для выдачи на эти вы- ходы нового кода в следующем цикле работы. Пусть сигналы поступали на входы 30-1 и30т накопителя подпрограмм26, который запоминает адреса выбранных подпрограмм и формирует сигналы на выходах 33-1, 33 т, поступающие в узел 29 ввода подпрограмм. Сигналы с выхода 32 поступают в задатчик 28, который задает соответствующий алгоритм выбора адресов подпрограмм в узле 29. Предполагается, что заданный ал го ритм требует последовательного введения выбранных адресов. Кроме того, задатчик 28 формирует сигнал продвижения на выход 38. Код с входа 31 формирователя 27 передается на выход 16, как уставка для первой и второй в группе подпрограммы.

Сигнал с выхода 38 задатчика 28 поступает- в узел 29, на выходах 11 готовности и 18-1 адреса первой в группе выбранных подпрограмм формируются сигналы, посту- лающие на выход блока.

Начинается передача данных, и после передачи группы сообщений на вход 17 задатчика 28 поступает сигнал, который передается на вход продвижения 38 узла 29 ввода подпрограмм, в котором: снимаются сигналы с выходов 11 и 18-1; формируется сигнал на выходе 34-1, поступающий в накопитель 26, с выхода 33-1 которого снимается сигнал; формируются сигналы на выходах Ли 18т; формируется сигнал на выходе 35-1, поступающий в формирователь 27, на выход 16 которого, с заданной задержкой, поступает новый (искаженный) код уставки, при этом снимается сигнал с входа 27 задатчика 28.

Начинается передача следующей группы сообщений, и после ее окончания на вход 17 снова подается сигнал, через задат- чик 28 передаваемый на вход 38 узла 29, в котором снимаются сигналы готовности и адреса обработанной подпрограммы с выходов 11 и 18 m и формируется сигнал на выходе 34 т, поступающий в накопитель 26,

с выхода 33 m которого сигнал снимается. Кроме того, формируются сигналы на выходах 37 и 35 т.

Сигнал с выхода 37 поступает в задэт- чик 28 и. передается на выход 36, с которого поступает в накопитель 26 и на вход продвижения памяти 25, подающей на выходы 30, 31, 32 новые коды. Пусть сигналы поступили на выходы 30-2, ... , тогда в накопителе 26 формируются сигналы на выходах 33-2, .... с которых они поступают в узел 29, где формируются сигналы на выходах 18-2 и 11, а также снимается сигнал с выхода 37. Код с выхода 32 поступает в задатчик 28, который задает новый алгоритм ввода выбранных адресов подпрограмм, например разделение выбранных программ на две группы и ввод одной из групп или поочередный ввод подпрограмм из таких групп.

Сигнал с выхода 35 узла 29 поступает в формирователь 27, который код с входа 31 с задержкой, достаточной для ввода новой 18-2, ... группы подпрограмм, передает на выход 16 блока, при этом снимается сигнал с входа 17.

После этого продолжается передача данных, для преобразования которых выбраны адреса новой группы подпрограмм 18-.2,... Так продолжается до поступления на вход 12 сигнала сброса, выдаваемого на входы памяти 25, задатчика 28, узла 26, которые возвращаются в исходное состояние.

Формула изобретения 1. Устройство кодирования, содержащее блок управления и блок преобразования информации, причем выходы блока преобразования информации являются выходами устройства, вход сброса которого соединен с входом сброса блока управления, первый и второй выходы управления которого являются выходами конца приема информации и выходом готовности приема информации устройства соответственно, информационные входы блока преобразования информации соединены с информационными входами устройства, отличающееся тем, что, с целью повышения крип- тостойкости и быстродействия, входы управления загрузкой и выводом блока преобразования информации являются одноименными входами устройства, адресные входы блока управления являются входами задания кода типа кодирования устройства, первая и вторая группы выходов поля управления блока управления соединены с первой и второй группами адресных входов блока преобразования информации соответственно, выход конца преобразования которого соединен с входом логического условия блока управления, а его вход сброса является входом сброса устройства.

управляющий вход которого соединен с первым разрядом входа управления блока и с управляющими вх одами второго узла коммутации первого и второго коммутаторов,

второй разряд входа управления блока соединен с управляющими входами первого узла коммутации и третьего коммутатора, выход третьей группы элементов ИЛИ является выходом блока и через элемент ИЛИ

соединен со счетным входом счетчика, выход переполнения которого соединен с выходом конца преобразования блока, первая группа адресных входов которого соединена с группой информационных входов счетчика, вход сброса которого является входом сброса блока, при этом выход первого коммутатора соединен с группой информационных входов коммутатора инверсных преобразований.

3, Устройство поп.1,отличающее- с я тем, что блок управления содержит память программ преобразования, накопитель подпрограмм, формирователь уставок,

задатчик алгоритмов и узел ввода подпрограмм, при этом адресные входы блока управления являются информационными входами памяти программ преобразования, первые, вторые и третьи информационные

выходы которой соединены соответственно с входами накопителя подпрограмм, формирователя уставок и установочными входами задатчика алгоритмов, первый выход которого соединен с входом сброса накопителя

подпрограмм и входом сдвига памяти программ преобразования, управляющий выход которой является первым выходом управления блока и соединен с вторым входом задатчика алгоритмов, третий вход которого является входом логического условия блока, первая группа выходов поля управления которого является выходом формирователя уставок, управляющие входы которого соединены с первой группой

выходов узла ввода подпрограмм, вторая группа выходов и первая группа входов которого соединены с входами и выходами соответственно накопителя подпрограмм, при этом вход сброса блока управления соединен с входами сброса памяти программ преобразования, задатчика алгоритмов и узла ввода подпрограмм, управляющие вход и выход которого соединены соответственно с вторым выходом и четвертым входом задатчика алгоритмов, вход продвижения, первый и второй выходы продвижения которого соединены соответственно с выходом продвижения и первым, вторым входами продвижения узла ввода

подпрограмм, управляющий выход и группа

адресных выходов которого являются вто- выходов поля управления блока управле- рым выходом управления и второй группой ния.

Фиг/

| Хоффман Л.Ф.Ю | |||

| Современные методы защиты информации | |||

| М.: Сов.радио, с.108- 127, рис.7.1 -7.7, 1980 | |||

| Устройство кодирования | 1985 |

|

SU1300639A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-23—Публикация

1989-11-22—Подача