Изобретение относится к вычислительной технике и может быть использовано для передачи информации между цифровой вычислительной машиной и периферийными устройствами или между периферийными устройствами с малой функциональной сложностью аппаратуры для реализации данного устройства.

Известны также способ и устройство для передачи данных, по котором передаются синхронные биты первого и второго видов внутри блока, причем число синхробитов, относящихся ко второму виду, соответствует условию 2NM-N-1 2:1 и

Недостатком способа и устройства является большая сложность. Оно содержит

одно устройство одного типа 46, четыре устройства второго типа 40, два устройства третьего типа 42, два устройства четвертого типа.

Известно устройство для приема и передачи информации, содержащее три регистра, три группы элементов И, генератор импульсов, дешифратор, индикатор, два элемента задержки, усилитель, два элемента ИЛИ, три триггера. Выходы первого регистра соединены с входами элементов И первой группы. Выход генератора соединен с вторыми входами элементов И первой группы. Выход первого триггера соединен с третьими входами элементов И первой группы. Выход второго регистра соединен с первыми входами элементов И второй группы.

vj 00

00

ся

W 00

Выход первого элемента задержки соединен с третьими входами элементов И второй группы. Выходы третьего регистра соединены с входами дешифратора выходы которого соединены с первыми входами элементов И третьей группы. Выход элемента И соединен с первым входом индикатора. Указан- ное устройство является наиболее близким и выбрано в качестве прототипа.

Недостатком этого устройства является большая сложность. Дня его реализации необходимо большое количество оборудования.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство для передачи дискретной информации, содержащее дешифратор, два элемента задержки, три регистра, три элемента И, два канала связи, шину тактовых импульсов, причем информационные кроме первого входы первого регистра соединены с информационными входами устройства, выход первого регистра соединен с первым входом первого элемента И, содержит формирователь импульсов, счетчик импульсов, триггер, элемент И-НЕ, элемент НЕ при- этом информационные входы дешифратора соединены с адресными входами устройства. Первый вход первого регистра подсоединен к шине логической единицы, а вход последовательной информации этого регистра подсоединен к шине логического нуля, выход дешифратора соединен с входом за- писи первого регистра и с установочным входом триггера. Шина тактовых импульсов соединена с входом синхронизации первого регистра и вторыми входами первого и второго элементов И, и через первый элемент НЕ - с входом элемента И-НЕ. Выход первого элемента И соединен через первый канал связи с информационным входом второго регистра и входом второго элемента задержки, выход которого соединен через второй формирователь с входом третьего элемента И. Единичный выход триггера содинен с первым входом второго элемента И, выход которого соединен с счетным вхоом сметчика и через первый элемент задер- ки, второй канал связи с входом инхронизации второго регистра и через второй элемент НЕ с вторым входом третьго элемента И, выход которого соединен с входом синхронизации третьего регистра, нформационные входы которого соединеы с выходами разрядов второго регистра, выходы с выходами устройства, инверсый выход триггера соединен с входом броса счетчика, выходы разрядов которого оединены с группой входов элемента И-НЕ, выход которого соединен с входом сброса триггера.

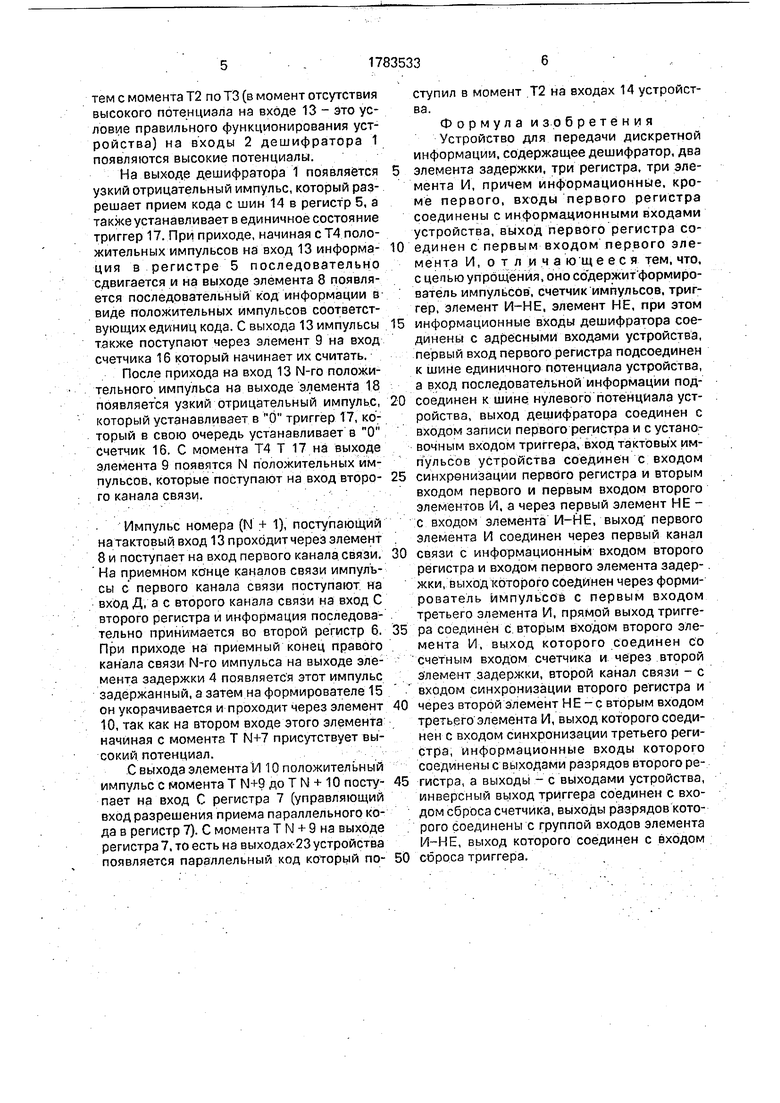

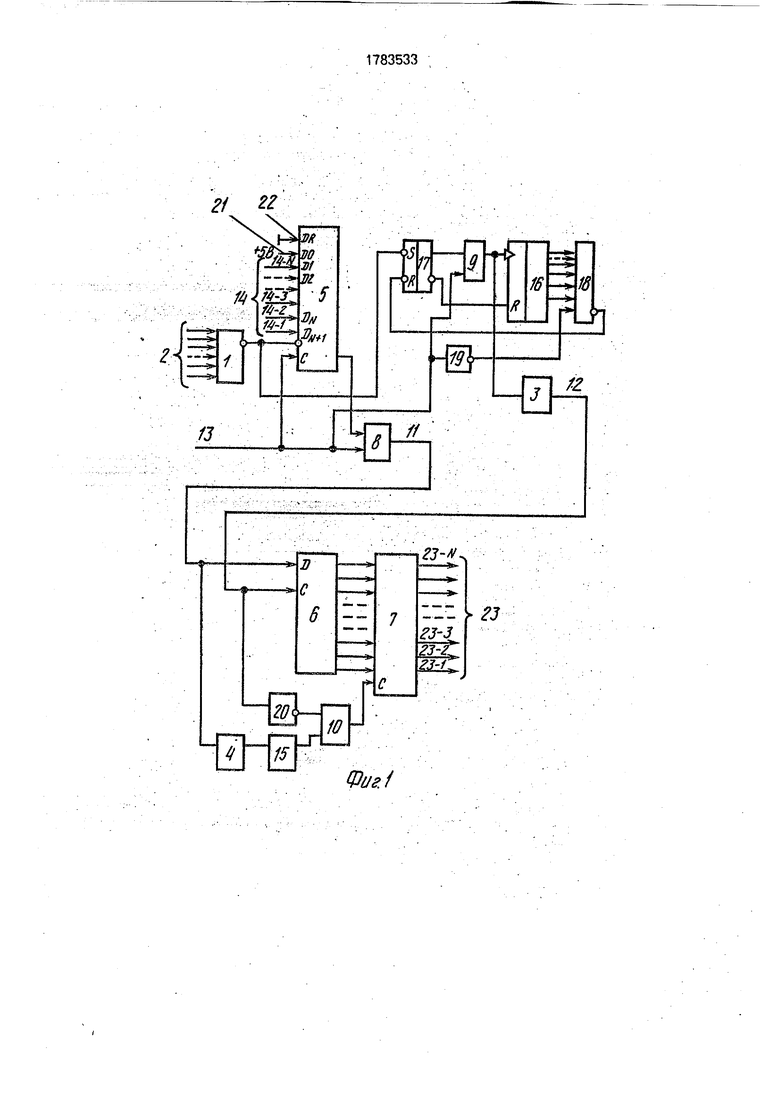

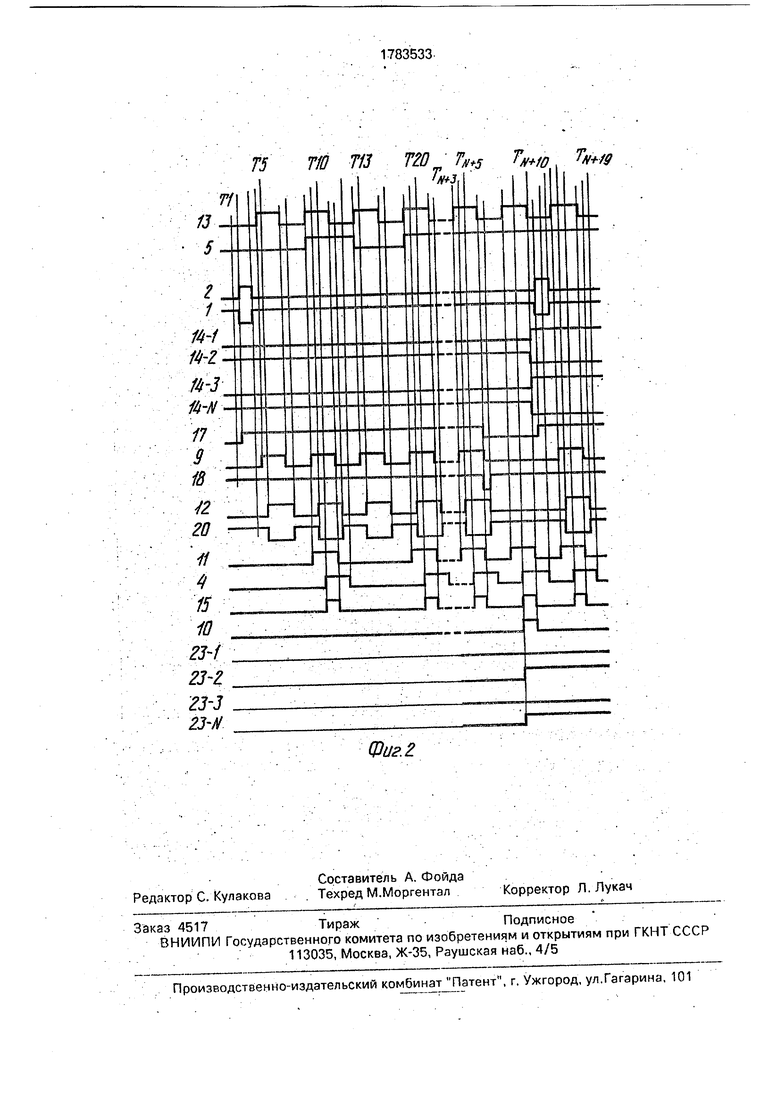

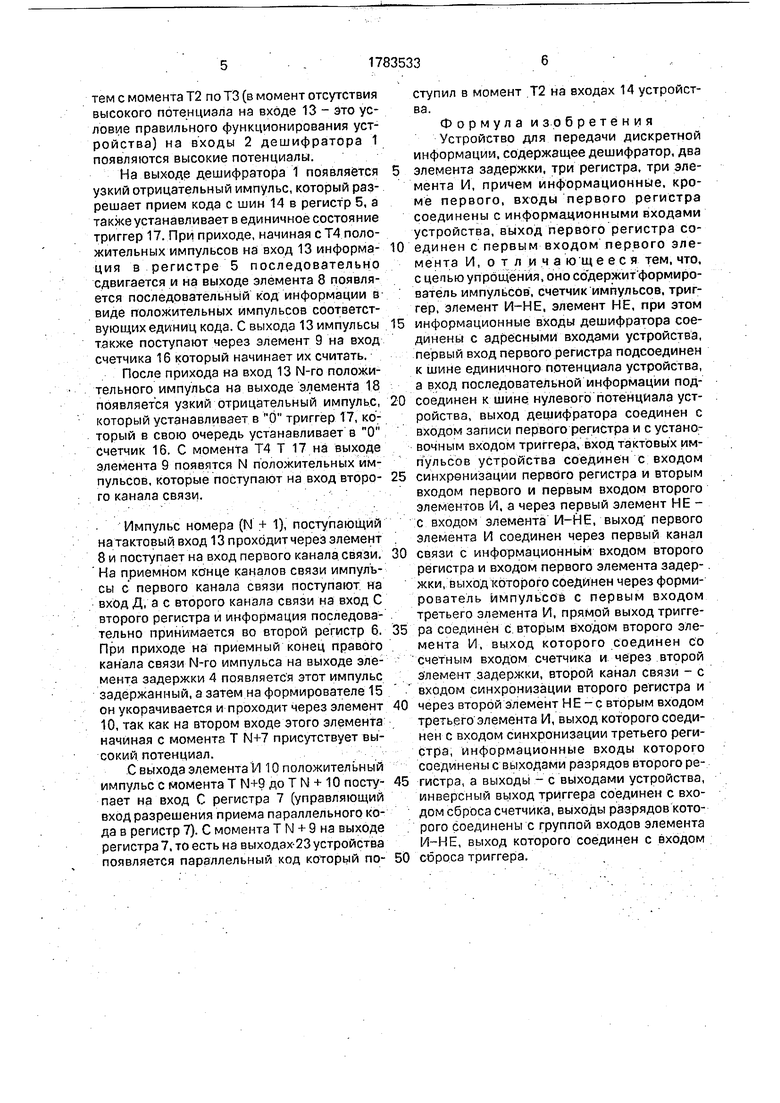

На фиг.1 приведена структурная схема устройства; на фиг.2 - временная диаграм- 5 ма работы устройства,

Устройство для передачи дискретной информации см. фиг.1 содержит дешифратор 1, входы которого соединены с адресными входами выбора устройства 2, элементы

10 задержки 3, 4, регистры 5, б, 7, элементы И 8, 9,10, каналы связи 11, 12, шину тактовых импульсов 13, причем информационные кроме первого входы первого регистра 5 соединены с информационными входами

15 устройства 14. Выход первого регистра 5 соединен с первым входом первого элемента И 8. Устройство содержит также формирователь импульсов 15, счетчик импульсов 16, триггер 17, элемент И-НЕ 18, два эле0 мента НЕ 19, 20. Первый вход 21 первого регистра 5 подсоединен к шине логической единицы, а вход 22 последовательной информации этого регистра подсоединен к шине логического нуля. Выход дешифрато5 ра 1 соединен с входом записи первого регистра- бис входом триггера 17. Вход тактовых импульсов 13 соединен с входом синхронизации первого регистра 5 и вторыми входами первого и второго элементов И

0 8,9, и через первый элемент Н Е 19 с входом элемента И-НЕ, выход первого элемента И 8 соединен через первый канал связи 11с информационным входом второго регистра

6и входом второго элемента задержки 4, 5 выход которого соединен через формирова

тель 15 с входом третьего элемента И 10. Единичный выход триггера 17 соединен с первым входом второго элемента И 9, выход которого соединен с счетным входом счет0 чика 16 и через первый элемент задержки, второй канал связи 12с входом синхронизации второго pei истра 6 и через второй элемент НЕ 20 с вторым входом третьего элемента И 10, выход которого соединен с

5 входом синхронизации третьего регистра 7. Информационные входы третьего регистра

7соединены с выходами разрядов второго регистра 6, а выходы с выходами устройства 23. Инверсный выход триггера 17 соединен

0 с входом сброса счетчика 16, выходы разрядов которого соединены с группой входов элемента И-НЕ, выход которого соединен с входом сброса триггера 17.

Работает устройство следующим обра5 зом. Предположим в первоначальный момент времени ТО на параллельные входы 14 устройства подается параллельный код, который необходимо передать через каналы связи в другую часть устройства расположенному на значительном расстоянии Затем с момента Т2 по ТЗ (в момент отсутствия высокого потенциала на входе 13 - это условие правильного функционирования устройства) на входы 2 дешифратора 1 появляются высокие потенциалы.

На выходе дешифратора 1 появляется узкий отрицательный импульс, который разрешает прием кода с шин 14 в регистр 5, а также устанавливает в единичное состояние триггер 17. При приходе, начиная сТ4 положительных импульсов на вход 13 информация в регистре 5 последовательно сдвигается и на выходе элемента 8 появляется последовательный код информации в виде положительных импульсов соответствующих единиц кода. С выхода 13 импульсы также поступают через элемент 9 на вход счетчика 16 который начинает их считать.

После прихода на вход 13 N-ro положительного импульса на выходе элемента 18 появляется узкий отрицательный импульс, который устанавливает в О триггер 17, который в свою очередь устанавливает в О счетчик 16. С момента Т4 Т 17 на выходе элемента 9 появятся N положительных импульсов, которые поступают на вход второго канала связи.

Импульс номера (N + 1), поступающий на тактовый вход 13 проходит через элемент 8 и поступает на вход первого канала связи. На приемном конце каналов связи импулъ- сы с первого канала связи поступают на вход Д, а с второго канала связи на вход С второго регистра и информация последовательно принимается во второй регистр 6. При приходе на приемный конец правого канала связи N-ro импульса на выходе элемента задержки 4 появляется этот импульс задержанный, а затем на формирователе 15 он укорачивается и проходит через элемент 10, так как на втором входе этого элемента начиная с момента Т N+7 присутствует высокий потенциал.

С выхода элемента 1110 положительный импульс с момента ТМНЗдоТЫ + Ю поступает на вход С регистра 7 (управляющий вход разрешения приема параллельного кода в регистр 7). С момента Т N + 9 на выходе регистра 7, то есть на выходах 23 устройства появляется параллельный код который поступил в момент Т2 на входах 14 устройства.

Формула изобретения Устройство для передачи дискретной информации, содержащее дешифратор, два 5 элемента задержки, три регистра, три элемента И, причем информационные, кроме первого, входы первого регистра соединены с информационными входами устройства, выход первого регистра со0 единен с первым входом первого элемента И, отл ичающееся тем, что. с цепью упрощения, оно содержит формирователь импульсов, счетчик импульсов, триггер, элемент И-НЕ, элемент НЕ, при этом

5 информационные входы дешифратора соединены с адресными входами устройства, первый вход первого регистра подсоединен к шине единичного потенциала устройства, а вход последовательной информации под0 соединен к шине нулевого потенциала устройства, выход дешифратора соединен с входом записи первого регистра и с установочным входом триггера, вход тактовых импульсов устройства соединен с входом

5 синхренизации первого регистра и вторым входом первого и первым входом второго элементов И, а через первый элемент НЕ - с входом элемента И-НЕ, выход первого элемента И соединен через первый канал

0 связи с информационным входом второго регистра и входом первого элемента задержки, выход которого соединен через формирователь импульсов с первым входом третьего элемента И, прямой выход тригге5 ра соединен с вторым входом второго элемента И, выход которого соединен со счетным входом счетчика и через второй элемент задержки, второй канал связи - с входом синхронизации второго регистра и

0 через второй элемент Н Е - с вторым входом третьего элемента И, выход которого соединен с входом синхронизации третьего регистра, информационные входы которого соединены с выходами разрядов второго ре5 гистра, а выходы - с выходами устройства, инверсный выход триггера соединен с входом сброса счетчика, выходы разрядов которого соединены с группой входов элемента И-НЕ, выход которого соединен с входом

0 сброса триггера.

21 &

Nu

ш

#4

&F

i Тле//

6-«--о

/f TLJ

ЛР

7 J/ 1й

5 fy fat с

S

-

if

F

J

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель | 1991 |

|

SU1777176A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для управления полупровод-НиКОВыМ НАКОпиТЕлЕМ | 1979 |

|

SU842811A1 |

| Устройство для ввода информации | 1982 |

|

SU1130854A1 |

Изобретение относится к вычислительной технике и может быть использовано для передачи информации.между цифровой вычислительной машиной и периферийными устройствами или между периферийными устройствами с малой функциональной сложностью аппаратуры для реализации данного устройства. Целью изобретения является упрощение устройства. В устройство, содержащее дешифратор, два элемента задержки, три регистра, три элемента И, два канала связи, шину тактовых импульсов, причем информационные, кроме первого, входы первого регистра соединены с информационными входами устройства, выход первого регистра соединен с первым входом первого элемента И, введены формирователь импульсов, счетчик импульсов, триггер, элемент И-НЕ, элемент НЕ, В устройстве периферийное устройство проще, т.е. содержит меньше аппаратуры. В среднем при передаче кодов длиной 16 бит и более получается экономия в количестве оборудования более 25%. 2 ил. сл

/J

д

6

un

пГ

/ J

8

//

Ј7-л

,C

Щ

23

Фм/

Фиг. г

| Патент ГДР Ns 230947, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для приема и передачи информации | 1984 |

|

SU1203569A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1992-12-23—Публикация

1991-01-22—Подача