(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУПРОВОДНИКОВЫМ

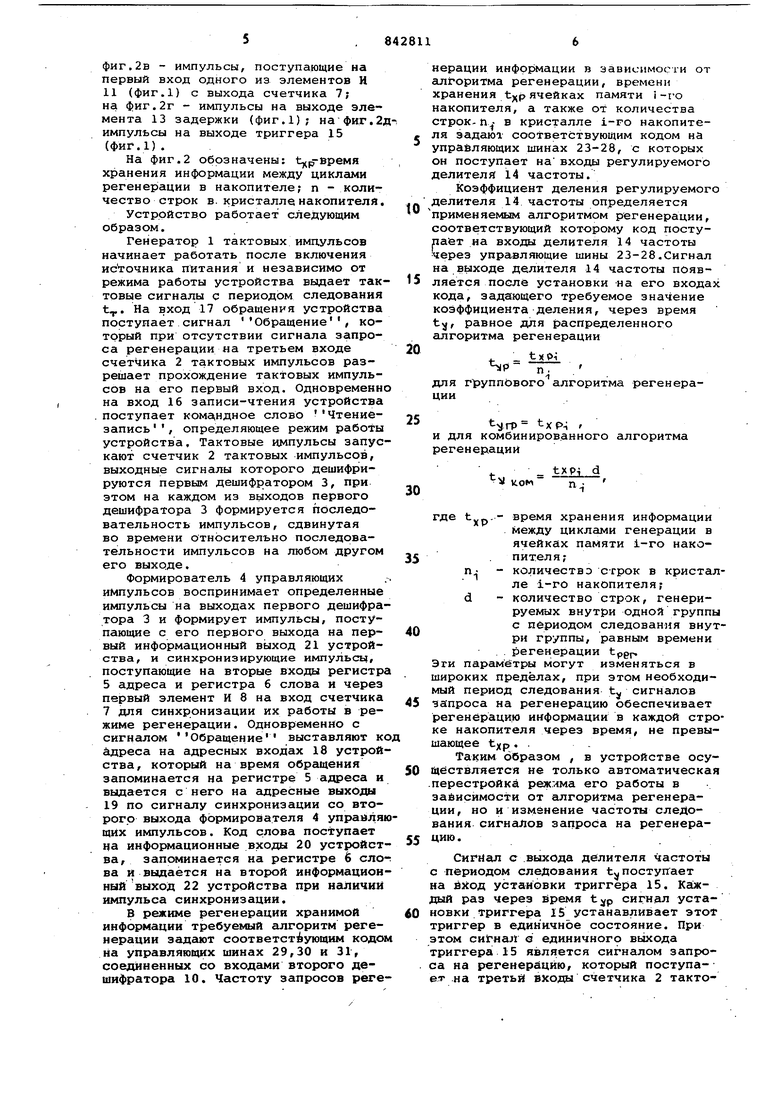

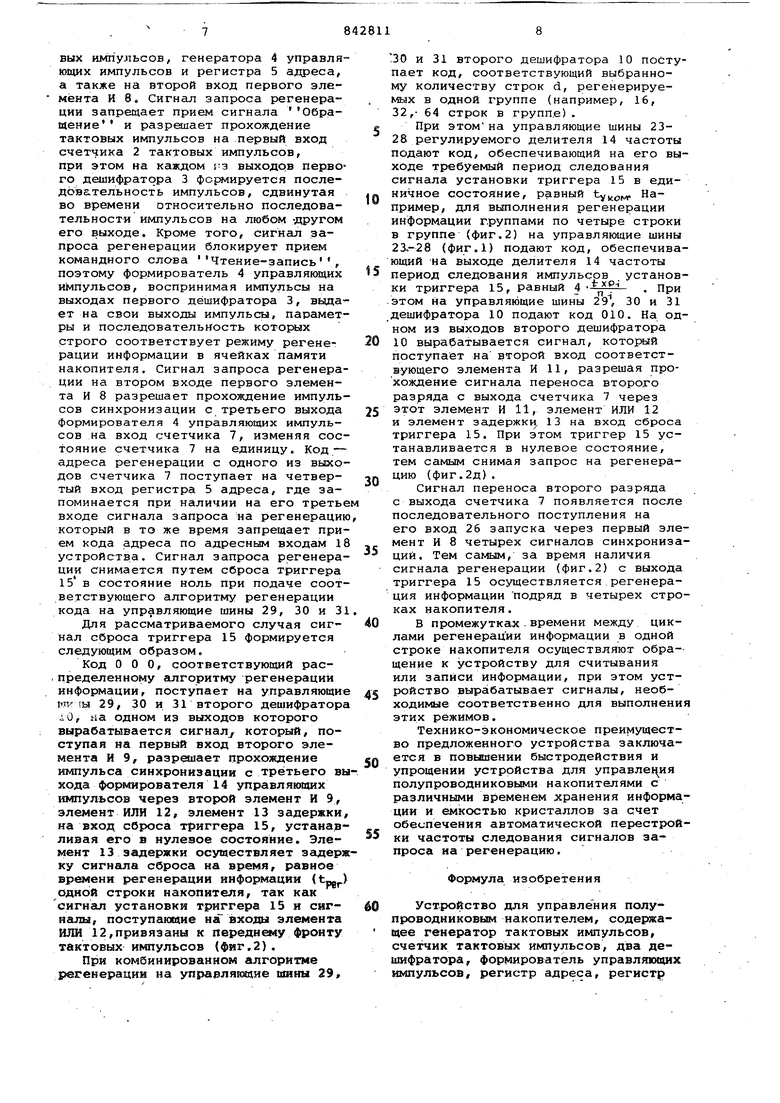

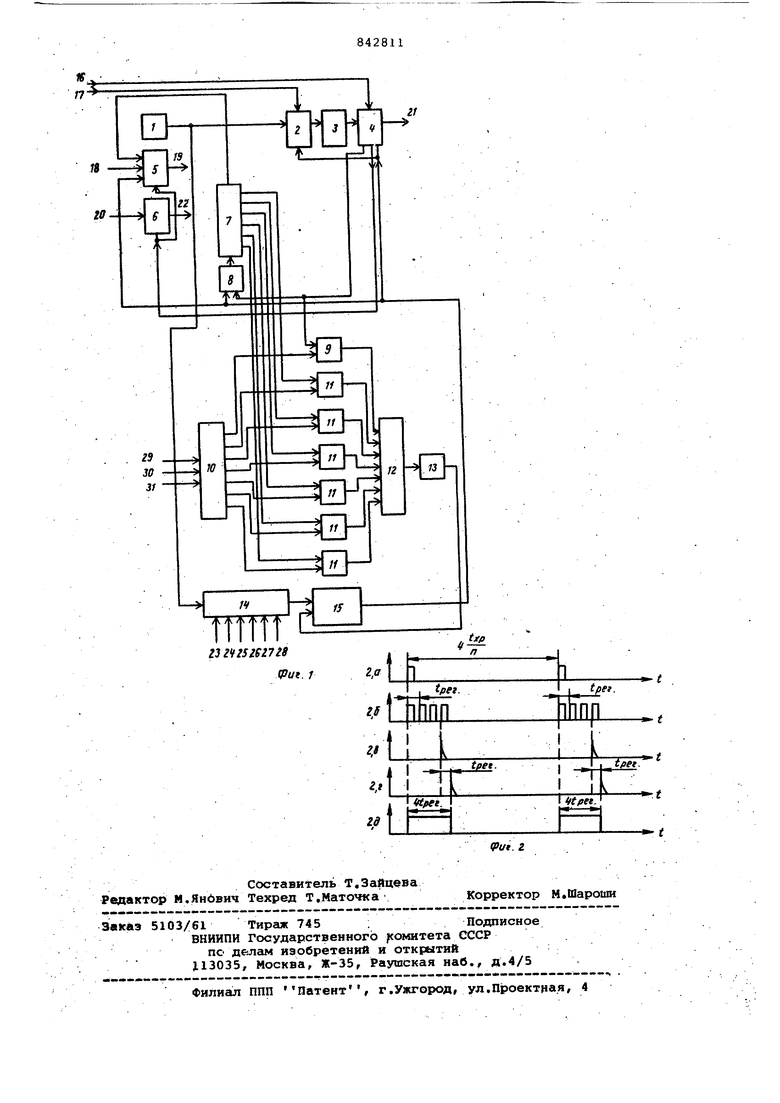

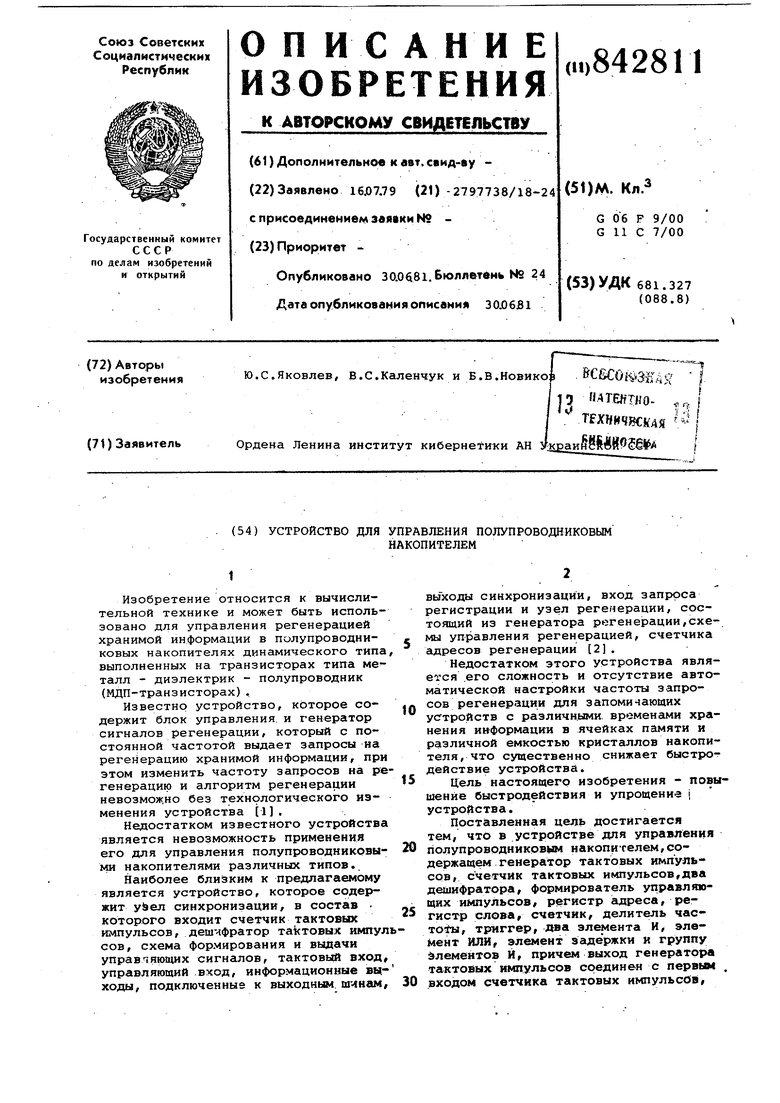

НАКОПИТЕЛЕМ выходы которого подключены ко входа первого дешифратора, выходы которог соединены с первым входом формирова ля управляющих импульсов, первый выход которого является первым инфо мационным выходом устройства, вторы входы счетчика тактовых икшульсов и .формирователя управляющих импульсов являются соответственно входами обращения и чтения-записи устройства, первые входы и выходы регистров адреса и слова являются соответственно адресными входами и выходами, информационными входами и вторым ин формационным выходом устройства, вторые входы регистров адреса и слова .подключены ко второму выходу формирователя управляющих импульсов .третий и четвертый входы регистра адреса соединены соответственно с третьим входом формирователя управляющих импульсов и с одним из выходов счетчика, одни из входов делител частоты подключены к одним из управ ляющих шинiустройства, а входы второго дешифратора - к другим управляю щим шинам, выходы счетчика соединены с первыми входами элементов И группы вторые входы которых подключены к одним из выходов второго дешифратора первые входы первого и второго элементов И соединены с третьим выходом формирователя управляющих импуль сов, третий вход которого подключен к третьим входс1м счетчика тактовых импульсов и регистра адреса, второму входу первого элемента И и выходу . триггера, выход первого элемента И соединен со входом счетчика, второй вход второго элемента И подключен к другому выходу второго дешифратора выход второго элемента И и выходы элементов И группы соединены с соответствующими входами элемента ИЛИ, выход которого подключен ко входу элемента задержки, выход которого соединён со входом сброса триггера, вход установки которого подключен к выходу делителя частоты, другой вход которого соединен с выходом генератора тактовых импульсов. На фиг.1 изображена Функциональ1 ая схема предложенногоустрюйства на фиг. 2 - временная диаграмма 1$аботы устройства. Устройство содержит (фиг.1)генератор 1 тактовых импульсов, счетчик 2 тактовых импульсов, первый дешифратор 3, формирователь 4 управлякндйх импульсов, регистр 5 адреса, регистр б слова, счетчик 7, первый 8 и второй 9 элементы И, второй дешифратор 10, группу элементов И 11, элемент ИЛИ 12, .элемент 13 задержки, делитель 14 частоты,-являющийся регулируемым, триггер 15, вход 16 запись-чтение, вход 17 обращения адресные входы 18 и выходы 19, информационный вход 20, первый 21 и второй 22 информационные выход} и управляющие шины 23-31. Выход генератора 1 тактовых импульсов соединен с первым входом счетчика 2 тактовых импульсов, выходы которого Подключены ко входам первого дешифратора 3. Выходы первого дешифратора 3 соединены с первым входом формирователя 4 управляющих импульсов, первый выход которого является первым информацио41ным выходом 21 устройства. Вторые входы счетчика 2 тактовых импульсов, и формирователя 4 управляющих импульсор являются соответственно входами 17 обращения и 16 чтения-записи устройства. Первые входы и выходы регистра 5 адреса и регистра б слова являются соответственно адресными входами 18 и выходами 19, информационными входами 20 и вторым информационным выходом 22 устройства. Вторые входы регистров 5 адреса и б слова подключены ко второму выходу формирователе 4 управляющих импульсов . Третий и четвертый входы регистра 5 адреса соединены соответственно с третьим входом формирователя 4 управляющих импульсов и с одним из выходов счетчика 7. Одни из входов делителя 14 частоты подключены к одним из управляющих шин 23-28, а входы второго дешифратора 10 к другим управляющим шинам 29-31. Другие выходы счетчика 7 соединены соответственно с- первыми входами, группы элементов И 11, вторые входы которых подключены к одним из выходов второго дешифратора 10. Первые входы первого 8 и второго 9 элементов И соединены с третьим выходом формирователя 4 управляющих импульсов, третий вход которого подключен, к третьим входам счетчика 2 тактовых импульсов и регистра 5 адреса, второму входу первого элемента И 8 и выходу триггера 15. Выход первого элемента И 8 соединен со входом счетчика 7. Второй вход второго элемента И 9 подключен к другому выходу второго дешифратора 10. Выход второго элемент. И 9 и выходы группы элеме.нтов И 11 соединены с соответствующими входами элемента ИЛИ 12, выход которого подключен ко входу элемента 13 задержки.. Выход элемента 13 задержки соединен со входом сброса триггера 15, вход установки которого подключен к выходу делителя 14 частоты, другой вход которого соединен с выходом генератора 1 тактовых импульсов. На фиг.2 а изображены импульсы на выходе делителя 14 частоты (фиг.1); на фиг.26 -импульсы синхронизации на третьем выходе фо1 4ир6вателй 4 управляющих импульсов (фиг.1), период следования которых равен времени регенерации tp на фиг.2в - импульсы, поступающие на первый вход одного из элементов И 11 (фиг.1) с выхода счетчика 7; на фиг.2г - импульсы на выходе элемента 13 задержки (фиг.1); на фиг.2 импульсы на выходе триггера 15 (фиг.1). На фиг.2 обозначены: 1(5Время хранения информации между циклами регенерации в накопителе; п - количество строк в. кристалле накопителя. Устройство работает следующим образом. Генератор 1 тактовых имдульсов начинает работать после включения источника питания и независимо от режима работы устройства выдает так товые сигналы с периодом следования t. На вход 17 обращения устройства поступает сигнал Обращение, который при отсутствии сигнала запроса регенерации на третьем входе счетчика 2 тактовых импульсов разрешает прохождение тактовых импульсов на его первый вход. Одновременн на вход 16 записи-чтения устройства поступает командное слово Чтениезапись , определяющее режим работы устройства, Тактовые импульсы запус кают счетчик 2 тактовых импульсов, выходные сигналы которого дешифрируются первым дешифратором 3, при этом на каждом из выходов первого дешифратора 3 формируется последовательность импульсов, сдвинутая во времени относительно последовательности импульсов на любом другом его выходе. Формирователь 4 управляющих импульсов воспринимает определенные импульсы на выходах первого дешифра тора 3 и формирует импульсы, поступающие с его первого выхода на первый информационный выход 21 устройства, и синхронизирующие импульсы, поступающие на вторые входы регистр 5 адреса и регистра б слова и через первый элемент И 8 на вход счетчика 7 для синхронизации их работы в режиме регенерации. Одновременно с сигналом Обращение выставляют к адреса на адресных входах 18 устрой ства, который на время обращения запоминается на регистре 5 адреса и выдается с него на адресные выходы 19 по сигналу синхронизации со второго выхода формирователя 4 управля щих импульсов. Код слова поступает на информационные входы 20 устройст ва, запоминается на регистре 6 сло ва и выдаётся на второй информацион ный выход 22 устройства при наличии импульса синхронизации. В режиме регенерации хранимой информации требуемый алгоритм регенерации задают соответствующим кодо на управляющих шинах 29,30 и 31, соединенных со входами второго дешифратора 10. Частоту запросов реге нерации инфрЕ мации в зависимости от алгоритма регенерации, времени хранения ячейках памяти i-го накопителя, а также от количества строк. п,|- в кристалле i-ro накопителя задают соответствующим кодом на управляющих шинах 23-28, с которых он поступает на входы регулируемого делителя 14 частоты. Коэффициент деления регулируемого делителя 14 частоты определяется применяемым алгоритмом регенерации, соответствующий которому код поступает на входы делителя 14 частоты через управляющие шины 23-28.Сигнал на выходе делителя 14 частоты появляется после установки -на его входах кода, задающего требуемое значение коэффициента деления, через время t, равное для распределенного алгоритма регенерации для группового алгоритма регенерации txp , и для комбинированного алгоритма регенерации V.OM где tjjp.- время хранения информации между циклами генерации в ячейках памяти 1-го накопителя; - количество строк в кристалле i-ro накопителя; d - количество строк, генерируемых внутри одной группы с периодом следования внутри группы, равным времени . . регенерации tpg Эги параметры могут изменяться в широких пределах, при этом необходимый период следования t сигналов запроса на регенерацию обеспечивает регенерацию информации в каждой строке накопителя через время, не превышающее txp . Таким образом , в устройстве осуществляется не только автоматическая перестройка режима его работы в зависимости от алгоритма регенерации, но и изменение частоты следования сигналов запроса на регенерацию. Сигнал с выхода делителя частоты с периодом следования t nocTynaeT на вход установки триггера 15. Кажый раз через время сигнал установки триггера 15 устанавливает этот триггер в единичное состояние. При этом си)7нал о единичного вЕЛхода триггера 15 является сигналом запроа на регенерацию, который поступает на третьи входы счетчика 2 тактовых импульсов, генератора 4 управляющих импульсов и регистра 5 адреса, а также на второй вход первого элемента И 8. Сигнал запроса регенерации запрещает прием сигнала Обращение и разронает прохождение тактовых импульсов на первый вход счетчика 2 тактовых импульсов, при этом на каждом РЭ выходов первого дешифратора 3 формируется последовательность импульсов, сдвинутая во времени относительно последовательности импульсов на любом -другом его выходе. Кроме того, сигнал запроса регенерации блокирует прием командного слова Чтение-запись, поэтому формирователь 4 управляющих импульсов, воспринимая импульсы на выходах первого дешифратора 3, выдает на свои выходы импульсы, параметры и последовательность которых строго соответствует режиму регенерации информации в ячейках памяти накопителя. Сигнал запроса регенерации на втором входе первого элемента И 8 разрешает прохождение импульсов синхронизации с третьего выхода формирователя 4 управляющих импульсов на вход счетчика 7, изменяя состояние счетчика 7 на единицу. Код- адреса регенерации с одного из выходов счетчика 7 поступает на четвертый вход регистра 5 адреса, где запоминается при наличии на его третье входе сигнала запроса на регенерацию который в то же время запрещает прием кода адреса по адресным входам 18 устройства. Сигнал запроса регенерации снимается путем сброса триггера 15 в состояние ноль при подаче соответствующего алгоритму регенерации кода на управляющие шины 29, 30 и 31

Для рассматриваемого случая сигнал сброса триггера 15 формируется следующим образом.

Код 000, соответствующий рас1пределениому алгоритму регенераций информации, поступает на управляющие im 1Ы 29, 30 и 31 второго дешифратора iO, на одном из выходов которого вырабатывается сигнал который, поступая на первый вход второго элемента И 9, разрешает прохождение импульса синхронизации с третьего выхода формирователя 14 управляющих импульсов через второй элемент И 9, элемент ИЛИ 12, элемент 13 задержки, иа вход сброса триггера 15, устанавливая его в нулевое состояние. Элемент 13 задержки осуществляет задержку сигнала сброса на время, равное времени регенерации информации tpg одной строки накопителя, так как сигнал установки триггера 15 и сигналы, поступающие Ha входы элемента ИЛИ 12,привязаны к переднему фронту тактовых импульсов (фиг.2).

При комбинированном алгоритме регенерации на управлякяцие шины 29,

30 и 31 второго дешифратора 10 поступает код, соответствующий выбранному количеству строк d, регенерируемых в одной группе (например, 16, 32,- 64 строк в группе) .

При этомна управляющие шины 2328 регулируемого делителя 14 частоты подают код, обеспечивающий на его выходе требуемый период следования сигнала установки триггера 15 в единичное состояние, равный Например, для выполнения регенерации информации группами по четыре строки в группе (фиг.2) на управляющие шины 23.-28 (фиг.1) подают код, обеспечивающий на выходе делителя 14 частоты период следования импульсов . установки триггера 15, равный 4 „ . При .этом на управляющие шины 29, 30 и 31 дешифратора 10 подают код 010. На одном из выходов второго дешифратора 10 вырабатывается сигнал, который поступает на второй вход соответствующего элемента И 11, разрешая прохождение сигнала переноса второго разряда с выхода счетчика 7 через этот элемент И 11, элемент ИЛИ 12 и элемент задержки, 13 на вход сброса триггера 15. При этом триггер 15 устанавливается в нулевое состояние, тем самым снимая запрос на регенерацию (фиг.2д),

Сигнал переноса второго разряда с выхода счетчика 7 появляется после последовательного поступления на его вход 26 запуска через первый элемент И 8 четырех сигналов синхронизации. Тем самым, за время наличия сигнала регенерации (фиг.2) с выхода триггера 15 осуществляется регенерация информации подряд в четырех строках накопителя.

В промежутках времени между циклами регенерации информации в одной строке накопителя осуществляют обращение к устройству для считывания или записи информации, при этом устройство вырабатывает сигналы, необходимые соответственно для выполнени этих режимов.

Технико-экономическое преимущество предложенного устройства заключается в повыаении быстродействия и упрощении устройства для управлец ия полупроводниковыми накопителями с различными временем хранения информации и емкостью кристаллов за счет обеспечения автоматической перестройки частоты следования сигналов запроса на регенерацию.

Формула изобретения

Устройство для управления полупроводниковым накопителем, содержащее генератор тактовых импульсов, счетчик тактовых импульсов, два дешифратора , формирователь управляющих нмпульсов, регистр адреса, регистр

слова, счетчик, делитель частоты, триггер, два элемента И, элемент ИЛИ элемент задержки и группу элементов И, причем выход генератора тактовых импульсов соединен с первым входом счетчика тактовых импульсов, выходы которого подключены ко входам первого дешифратора, выходы которого соединены с первым входом формирователя управляющих импульсов,. первый выход которого является первым информационным выходом устройства, вторые вхо ды счетчика тактовых импульсов и формирователя управляющих импульсов являются соответственно входами обращения и чтения-записи устройства, первые входы и выход: регистров адреса и слова являются соответственно адресными входсши и выхода ми, информационными входами и вторьул информационным выходом устройства, вторые входы регистров адреса и елова подключены ко второму выходу фор:мирователя управляющих импульсов, третий и четвертый входы регистра адреса соединены соответственно с третьим входом формирователя управляющих импульсов и с одним из .выходов счетчика, одни из входов делителя частоты подключены к одним из управляющих шин устройства,/а входы второго дешифратора - к другим управляющим шинам, отличающееся тем, что, с целью повышения быстродействия, и упрощения устройства, в нем другие выходы счетчика соединены с первыми входами элементов И группы, вторые входы которых подключены к одним из выходов второго дешифратора, первые входы первого и второ.го элементов И соединены с третьим Выходом формирователя управляющих импульсов, третий вход которого подключен к третьим входам счетчика тактовых импульсов и регистра адреса, второму входу первог элемента И и выходу триггера, выход первого элемента И соединен со входом счетчика, второй вход второго элемента И подключен к другому выходу, второго дешифратора, выход второго элемента И и выходы элементов И группы соединены с соответствующими входами элемента ИЛИ, выход которого подключен ко входу.элемент задержки, выход которого соединен со входом сброса триггера, вход установки которого подключен к выходу делителя частоты, другой вход которого соединен с выходом генератора тактовых импульсов.

Источники информации, принятие во внимание при экспертизе

1.Авторское свидетельство СССР по заявке 2507749/18-24,

кл. G 06 F 9/00, 1978,

2.Авторское свидетельство СССР по заявке 2546736/18-24,

кл. G Об F 9/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| Устройство для регенерациииНфОРМАции B диНАМичЕСКиХблОКАХ пАМяТи | 1979 |

|

SU809388A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Запоминающее устройство | 1989 |

|

SU1718272A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

Авторы

Даты

1981-06-30—Публикация

1979-07-16—Подача