Изобретение относится к радиотехнике и может использоваться в анализаторах ошибок при контроле каналов связи.

Цель изобретения - повышение точности при одновременном увеличении помехоустойчивости

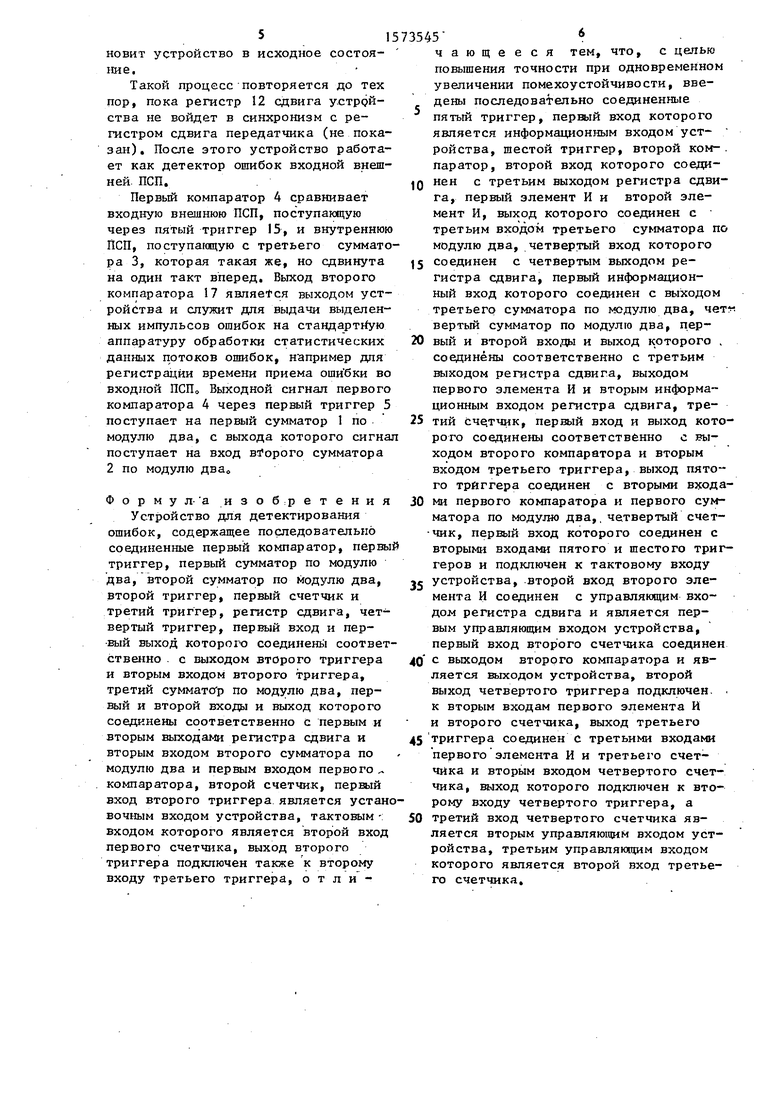

На чертеже представлена структурная электрическая схема предлагаемого устройства

Устройство для детектирования ошибок содержит первый 1, второй 2 и третий 3 сумматоры по модулю два, первый компаратор 4, первый 5, второй 6, третий 7 и четвертый 8 триг- , геры, первый 9 и второй 10 счетчики, первый элемент И 11, регистр 12 сдвига, включающий первый 1201 и втор ой 12.2 разряды и элемент И 12оЗ, тре- тий счетчик 13, четвертый сумматор 1 по модулю два, пятый 15 и шестой 16 триггеры, второй компаратор 17, четвертый счетчик 18 и второй элемент И 19.

Устройство работает следующим образом.

При подаче сигнала Лог.1 на первый управляющий вход устройства управляющим выходом разряда 12„1 регистра 12 сдвига сигнал Лог01 (высокий потенциал открывает элементы И 12„3 и 19. На их выходе появляется сигнал Лог.О или Лог.1 в зависимости от того, какой сигнал поступает на их вторые входы. При подаче сигнала Лог.О на первый

30 гистра 12 сдвига записана безошибочная информация, т0е0 регистр 12 сдвига устройства войдет в синхронизм с регистром сдвига передатчика (не показан), то на следующем этапе, когда на инверсном выходе третьего триггера 7 установится Лог00 и разрешен счет тактов четвертым счетчиком 18 и счет ошибок третьим счетчи ком 13, а первый элемент И 11 закрыт,

управляющий вход устройства управляющим выходом разряда 12„1 регистра 12 40третий счетчик 13 за число тактовых сдвига сигнал Лог,0 (низкий потен-периодов m при правильном выборе га циап) закрывает элементы И 12,3 ии (1+йО не достигает до своего моду- 19, т.е. на их выходах всегда присут-ля счета (1+оО (при ожидаемом распре- ствует сигнал Лог.О, что равносиль-делении ошибок во входной ПСП). На но отключению сигнала с выхода раз- 45выходе четвертого счетчика 18 появит- ряда 12.1 регистра 12 сдвига и сигна-ся импульс, который установит Лог,0 ла ошибки от третьего сумматора 3„

на прямом выходе четвертого триггера 8, который закроет первый элемент И 1 1 и разрешит счет ошибок вторым счетчиком 10, Т0е0 третий этап синхронизации закончится.

Одновременно после включения устройства импульс синхронизации (начальной установки) устанавливает второй 6, третий 7 и четвертый 8 триггеры, первый 9, третий 13 и четвертый 18 счетчики - в исходное состояние, при котором на выходе первого 9 и четвертого 18 счетчиков и прямом выходе третьего триггера 7 устанавливается уровень Лог.О, а на прямом выходе четвертого триггера 8 - уровень Лог.1. При этом на выходе второго

10

s

205735454

триггера б и третьего счетчика 13 устанавливается уровень Лог. О, который разрешает первому счетчику 9 счет тактов с тактового входа устройства;, Модуль счета четвертого счетчика 18, равный числз (га), и модуль счета третьего счетчика-13, равный числу (1+с/), устанавливается предварительно сигналами управления на соответствующих управляющих входах устройства. Второй компаратор 17 начинает сравнение входной внешней ПСП, поступающей через пятый 15 и шестой 16 триггеры и формируемой на третьем выходе регистра 12 сдвига (выход разряда 12,1) внутренней ПСП. При этом импульсы ошибок с выхода второго компаратора 17 проходят на третий счетчик 13 и на первый элемент И 11„ Последний открыт уровнями Лог.1 с инверсного выхода третьего триггера 7 и прямого выхода четвертого триггера 8. Поэтому импульсы ошибок воз25 действуют на регистр 12 сдвига через четвертый сумматор 14 до тех пор, пока первый счетчик 9 не досчитает число тактовых импульсов до (п+1) ,, Если при этом в разрядах 12,1 и 12,2 ре30 гистра 12 сдвига записана безошибочная информация, т0е0 регистр 12 сдвига устройства войдет в синхронизм с регистром сдвига передатчика (не показан), то на следующем этапе, когда на инверсном выходе третьего триггера 7 установится Лог00 и разрешен счет тактов четвертым счетчиком 18 и счет ошибок третьим счетчи- ком 13, а первый элемент И 11 закрыт,

35

40третий счетчик 13 за число тактовых периодов m при правильном выборе га и (1+йО не достигает до своего моду- -ля счета (1+оО (при ожидаемом распре- -делении ошибок во входной ПСП). На 45выходе четвертого счетчика 18 появит- -ся импульс, который установит Лог,0

третий счетчик 13 за число тактовых периодов m при правильном выборе га и (1+йО не достигает до своего моду- ля счета (1+оО (при ожидаемом распре- делении ошибок во входной ПСП). На выходе четвертого счетчика 18 появит- ся импульс, который установит Лог,0

на прямом выходе четвертого триггера 8, который закроет первый элемент И 1 1 и разрешит счет ошибок вторым счетчиком 10, Т0е0 третий этап синхронизации закончится.

Если на втором этапе синхронизации в регистре 12 сдвига записана хотя бы одна ошибка, которая принята во входной ПСП, на третьем этапе синхронизации третий счетчик 13 за число тактовых периодов m успевает достичь до своего модуля счета (1 + сО и положительный импульс на его выходе установит устройство в исходное состояние.

Такой процесс повторяется до тех пор, пока регистр 12 сдвига устройства не войдет в синхронизм с регистром сдвига передатчика (не показан). После этого устройство работает как детектор ошибок входной внешней ПСП.

Первый компаратор 4 сравнивает входную внешнюю ПСП, поступающую через пятый триггер 15, и внутреннюю ПСП, поступающую с третьего сумматора 3, которая такая же, но сдвинута на один такт вперед. Выход второго компаратора 17 является выходом устройства и служит для выдачи выделенных импульсов ошибок на стандартную аппаратуру обработки статистических данных потоков ошибок, например для регистрации времени приема ошибки во входной ПСПо Выходной сигнал первого компаратора 4 через первый триггер 5 поступает на первый сумматор 1 по модулю два, с выхода которого сигнал поступает на вход второго сумматора 2 по модулю два0

Формул а изобретения

Устройство для детектирования ошибок, содержащее последовательно соединенные первый компаратор, первы триггер, первый сумматор по модулю два, второй сумматор по модулю два, второй триггер, первый счетчик и третий триггер, регистр сдвига, четвертый триггер, первый вход и первый выход которого соединены соответственно с выходом второго триггера и вторым входом второго триггера, третий сумматсгр по модулю два, первый и второй входы и выход которого соединены соответственно с первым и вторым выходами регистра сдвига и вторым входом второго сумматора по модулю два и первым входом первого компаратора, второй счетчик, первый вход второго триггера является установочным входом устройства, тактовым - входом которого является второй вход первого счетчика, выход второго триггера подключен также к второму входу третьего триггера, отличающееся тем, что, с целью повышения точности при одновременном увеличении помехоустойчивости, введены последовательно соединенные пятый триггер, первый вход которого является информационным входом устройства, шестой триггер, второй компаратор, второй вход которого соедиQ нен с третьим выходом регистра сдвига, первый элемент И и второй элемент И, выход которого соединен с третьим входом третьего сумматора по модулю два, четвертый вход которого

5 соединен с четвертым выходом регистра сдвига, первый информационный вход которого соединен с выходом третьего сумматора по модулю два, чет вертый сумматор по модулю два, пер0 вый и второй входы и выход которого , соединены соответственно с третьим выходом регистра сдвига, выходом первого элемента И и вторым информационным входом регистра сдвига, тре5 тий сче.тчик, первый вход и выход которого соединены соответственно с выходом второго компаратора и вторым входом третьего триггера, выход пятого триггера соединен с вторыми входа0 ми первого компаратора и первого сумматора по модулю два, четвертый счет- чик, первый вход которого соединен с вторыми входами пятого и шестого триггеров и подключен к тактовому входу

5 устройства, второй вход второго элемента И соединен с управляющим входом регистра сдвига и является первым управляющим входом устройства, первый вход второго счетчика соединен

0 с выходом второго компаратора и является выходом устройства, второй выход четвертого триггера подключен к вторым входам первого элемента И и второго счетчика, выход третьего

5 триггера соединен с третьими входами первого элемента И и третьего счетчика и вторым входом четвертого счетчика, выход которого подключен к второму входу четвертого триггера, а

0 третий вход четвертого счетчика является вторым управляющим входом устройства, третьим управляющим входом которого является второй вход третьего счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2279184C2 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| Устройство для детектирования ошибок | 1990 |

|

SU1709542A1 |

| Устройство для детектирования ошибок | 1985 |

|

SU1251335A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Устройство для синхронизации @ -последовательности | 1984 |

|

SU1225002A1 |

| Устройство для передачи информации шумоподобными сигналами | 1984 |

|

SU1256239A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности при одновременном увеличении помехоустойчивости. Устройство содержит три сумматора 1-3 по модулю два, первый компаратор 4, четыре триггера 5 - 8, два счетчика 9,10, первый элемент И 11, регистр сдвига 12, включающий первый и второй разряды 12.1, 12.2 и элемент И 12.3, третий счетчик 13, четвертый сумматор 14 по модулю два, пятый и шестой триггеры 15, 16, второй компаратор 17, четвертый счетчик 18, второй элемент И 19. В зависимости от подачи управляющего сигнала /лог.1 или лог.0/ на первый управляющий вход открываются или закрываются элементы И 12.3 и 19. Второй компаратор 17 начинает сравнение внешней псевдослучайной последовательности (ПСП) и внутренней ПСП. По сигналу разности осуществляется вхождение устройства в синхронизм с регистром сдвига передатчика. После этого устройство начинает работать как детектор ошибок входной внешней ПСП. 1 ил.

| Авторское свидетельство СССР | |||

| Устройство для детектирования ошибок | 1985 |

|

SU1251335A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-23—Публикация

1988-12-12—Подача