Изобретение относится к области радиоизмерительной техники и может быть использовано в анализаторах ошибок при контроле качества работы систем связи.

Детектор ошибок решает следующие задачи:

а) формирования внутренней тест-последовательности;

б) синхронизации внутренней тест-последовательности входной внешней тест-последовательностью;

в) выделения ошибок из входной тест-последовательности путем сравнения входной внешней и внутренней тест-последовательностей;

г) подсчета количества ошибок счетчиком ошибок.

Тест-последовательность подается на объект контроля, с которого поступает на анализатор ошибок для проверки качества работы объекта контроля. В качестве тест-последовательности наиболее частот используется псевдослучайная последовательность (ПСП) максимальной длины (М-последовательность).

Известны устройства для детектирования ошибок [1, 2], в которых используются систематические свойства М-последовательностей, которые позволяют достаточно точно проводить измерение количества ошибок. Всю работу таких устройств при каждой попытке входа в режим синхронизации можно разбить на три этапа: установка начального состояния, запись информации и проверка отсутствия ложной синхронизации. При успешной попытке входа в режим синхронизации устройство начинает свою основную работу - детектирования и анализа потока ошибок. За счет определения факта ложной синхронизации устройства и запрещения его работы (запрещения счета ошибок) на время, необходимое для повторной синхронизации, повышается точность измерений, так как при этом запрещается регистрация ошибок, в число которых могут входить ошибки, появившиеся на входе счетчика ошибок в результате ложной синхронизации устройства и отсутствующие во входной последовательности. Затраты времени на проверку отсутствия ложной синхронизации и (в случае необходимости) повторную синхронизацию устройства составляют 3n тактовых интервалов [1], где n - число разрядов (длина) регистра сдвига, в который производится запись входной информации.

Недостатком таких устройств является недостаточная помехоустойчивость - невозможность синхронизации при приеме входной внешней М-последовательности с максимальным средним по времени коэффициентом ошибок  так как если на этапах записи информации или проверки отсутствия ложной синхронизации во входной внешней М-последовательности будет присутствовать хотя бы одна ошибка (в каком-либо из 2·n битов информации), то такие устройства (детекторы ошибок) будут возвращаться в исходное начальное состояние, при этом подсчет ошибок производиться не будет.

так как если на этапах записи информации или проверки отсутствия ложной синхронизации во входной внешней М-последовательности будет присутствовать хотя бы одна ошибка (в каком-либо из 2·n битов информации), то такие устройства (детекторы ошибок) будут возвращаться в исходное начальное состояние, при этом подсчет ошибок производиться не будет.

Известно устройство для детектирования ошибок, взятое в качестве прототипа [3], в котором используются систематические свойства М-последовательностей [4], которые позволяют проводить измерения количества ошибок в системе цифровой связи.

Недостатком такого устройства является невозможность определения места возникновения ошибок в последовательно-параллельной цепи устройств системы цифровой связи и, следовательно, невозможность диагностики такой системы с точностью до неисправной части (блока, узла и т.д.).

Задачей, на решение которой направлено заявляемое техническое решение устройства для детектирования ошибок, является определение места возникновения ошибок в последовательно-параллельной цепи устройства системы цифровой связи, что позволит диагностировать такие системы по месту неисправности. Для этого каждому блоку контролируемого объекта ставится в соответствие некоторая величина ошибок, производящая возмущающее воздействие.

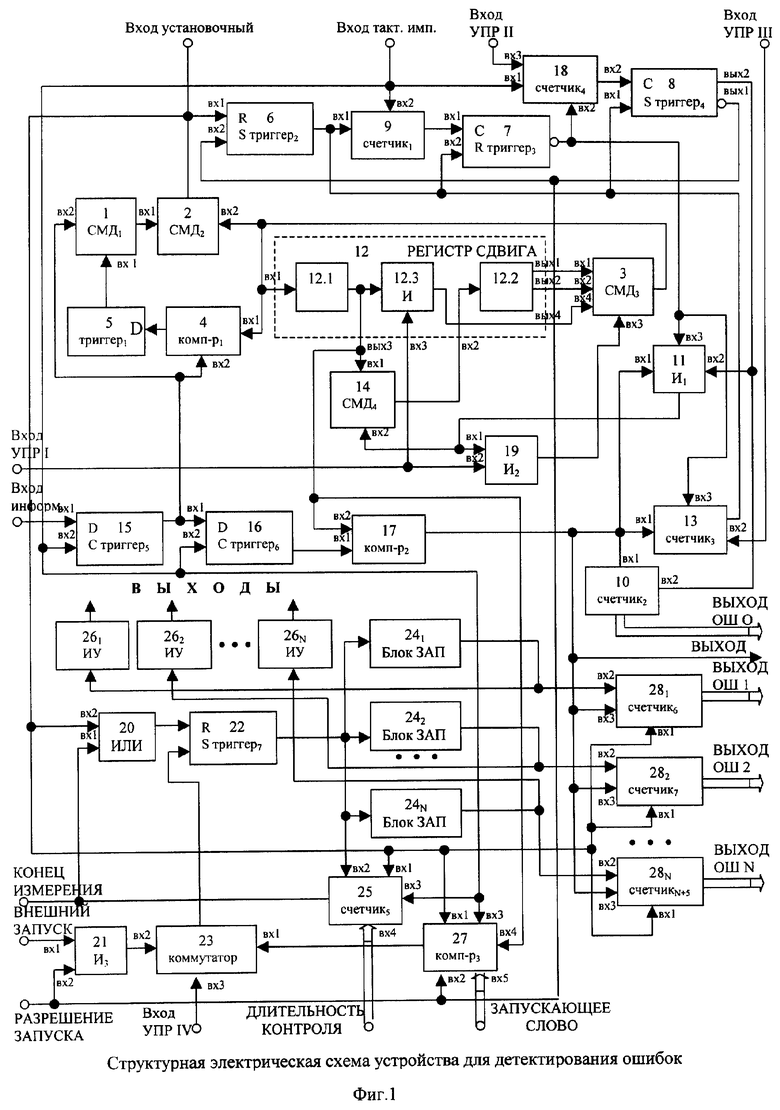

Сущность технического решения предлагаемого изобретения заключается в том, что в устройство для детектирования ошибок, содержащее последовательно соединенные первый компаратор 4, первый триггер 5, первый сумматор по модулю два 1, второй сумматор по модулю два 2, второй триггер 6, первый счетчик 9 и третий триггер 7, регистр сдвига 12, четвертый триггер 8, первый вход и первый выход которого соединены соответственно с выходом второго триггера 6 и вторым входом второго триггера 6, третий сумматор по модулю два 3, первый и второй входы и выход которого соединены соответственно с первым и вторым выходами регистра сдвига 12 и вторым входом второго сумматора по модулю два 2 и первым входом первого компаратора 4, второй счетчик 10, первый вход второго триггера 6 является установочным входом устройства, тактовым входом которого является второй вход первого счетчика 9, выход второго триггера 6 подключен также к второму входу третьего триггера 7, последовательно соединенные пятый триггер 15, первый вход которого является информационным входом устройства, шестой триггер 16, второй компаратор 17, второй вход которого соединен с третьим выходом регистра сдвига 12, первый элемент «И» 11 и второй элемент «И» 19, выход которого соединен с третьим входом третьего сумматора по модулю два 3, четвертый вход которого соединен с четвертым выходом регистра сдвига 12, первый информационный вход которого соединен с выходом третьего сумматора по модулю два 3, четвертый сумматор по модулю два 14, первый и второй входы и выход которого соединены соответственно с третьим выходом регистра сдвига 12, выходом первого элемента «И» 11 и вторым информационным входом регистра сдвига 12, третий счетчик 13, первый вход и выход которого соединены соответственно с выходом второго компаратора 17 и вторым входом третьего триггера 7, выход пятого триггера 15 соединен с вторыми входами первого компаратора 4 и первого сумматора по модулю два 1, четвертый счетчик 18, первый вход которого соединен с вторыми входами пятого 15 и шестого 16 триггеров, подключен к тактовому входу устройства, второй вход второго элемента «И» 19 соединен с управляющим входом регистра сдвига 12 и является первым управляющим входом устройства, первый вход второго счетчика 10 соединен с выходом второго компаратора 17 и является выходом устройства, второй выход четвертого триггера 8 подключен к вторым входам первого элемента «И» 11 и второго счетчика 10, выход третьего триггера 7 соединен с третьими входами первого элемента «И» 11 и третьего счетчика 13 и вторым входом четвертого счетчика 18, выход которого подключен к второму входу четвертого триггера 8, а третий вход четвертого счетчика 18 является вторым управляющим входом устройства, третьим управляющим входом которого является второй вход третьего счетчика 13, введены элемент «ИЛИ» 20, третий элемент «И» 21, седьмой триггер 22, коммутатор 23, третий компаратор 27, N исполнительных устройств 26, счетчиков 28 и N блоков запуска 24, первый вход элемента «ИЛИ» 20 соединен с выходом пятого счетчика 25 и является выходом «КОНЕЦ ИЗМЕРЕНИЯ» устройства, установочный вход которого соединен с вторым входом элемента «ИЛИ» 20, первым входом пятого счетчика 25, первым входом третьего компаратора 27 и первыми входами от 6 до (N+5) счетчиков 281÷28N, выходы которых и выход второго счетчика 10 являются выходами ошибок устройства, выход элемента «ИЛИ» 20 соединен с R-входом седьмого триггера 22, S-вход которого подключен к выходу коммутатора 23, первый и второй входы которого соединены соответственно с выходом третьего компаратора 27 и выходом третьего элемента «И» 21, а управляющий вход коммутатора 23 является четвертым управляющим входом устройства, внешним запускающим входом которого является первый вход третьего элемента «И» 21, второй вход которого соединен с вторым входом третьего компаратора 27 и с первым инвертирующим выходом четвертого триггера 8 и является выходом «РАЗРЕШЕНИЕ ЗАПУСКА» устройства, выход седьмого триггера 22 соединен с входами первого, второго, ...N-го блока запуска 241÷24N и с вторым входом пятого счетчика 25, третий вход которого соединен с третьим входом третьего компаратора 27 и с тактовым входом устройства, четвертый вход третьего компаратора 27 соединен с третьим выходом регистра сдвига 12, а пятый вход является входом «ЗАПУСКАЮЩЕГО СЛОВА» устройства, входом «ДЛИТЕЛЬНОСТЬ КОНТРОЛЯ» которого является четвертый вход пятого счетчика 25, выходы первого, второго, ...N-го блоков запуска 241÷24N подключены соответственно к входам первого, второго, ...N-го исполнительного устройства 261÷26N и к вторым входам соответственно шестого, седьмого, ...(N+5)-го счетчиков 281÷28N, третьи входы которых подключены к выходу второго компаратора 17, выходы исполнительных устройств являются выходами устройства.

Сущность изобретения поясняется чертежами:

На фиг.1 представлена структурная электрическая схема заявляемого устройства для детектирования ошибок, где обозначено:

1, 2, 3 - первый, второй и третий сумматоры по модулю два (СМД);

4 - первый компаратор;

5, 6, 7, 8 - первый, второй, третий и четвертый триггеры;

9, 10 - первый и второй счетчики;

11 - первый элемент «И»;

12 - регистр сдвига (PC), включающий первый и остальные разряды 12.1; 12.2; и элемент «И» 12.3;

13 - третий счетчик;

14 - четвертый сумматор по модулю два;

15, 16 - пятый и шестой триггеры;

17 - второй компаратор;

18 - четвертый счетчик;

19 - второй элемент «И»;

20 - элемент «ИЛИ»;

21 - третий элемент «И»;

22 - седьмой триггер;

23 - коммутатор;

241÷24N - первый, второй, ...N-й блоки запуска;

25 - пятый счетчик;

261÷26N - первое, второе, ...N-e исполнительные устройства;

27 - третий компаратор;

281÷28N - шестой, седьмой ...(N+5)-й счетчики.

Обозначения входов триггеров:

R - вход установки логического нуля;

S - вход установки логической единицы.

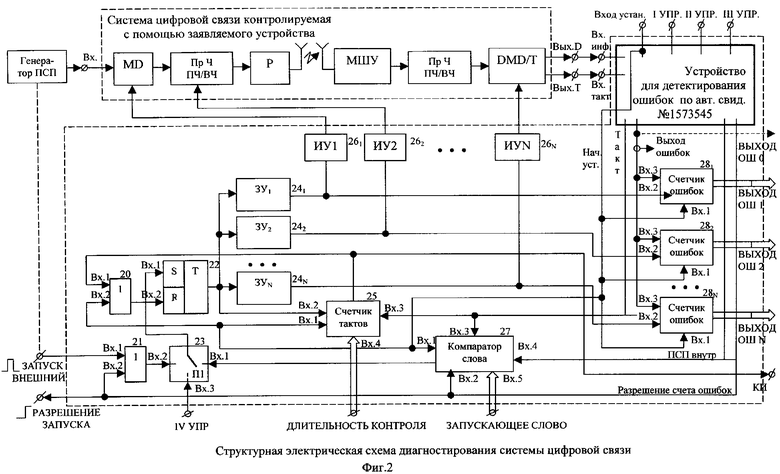

На фиг.2 представлена структурная электрическая схема диагностирования системы цифровой связи, где обозначено:

ЗУ1÷ЗУN - запускающие устройства;

I - элемент «ИЛИ»;

Т-R-S - триггер;

П1 - переключатель;

И - элемент «И»;

ИУ1, ИУ2,...ИУN - исполнительные устройства;

МД - модулятор;

Прч ПЧ/ВЧ - преобразователь частоты ПЧ/ВЧ;

Р - усилитель мощности;

МШУ - малошумящий усилитель;

Прч ВЧ/ПЧ - преобразователь частоты ВЧ/ПЧ;

ДМД/т - демодулятор со схемой восстановления тактовых импульсов.

На фиг.2 цифра рядом с элементом соответствует порядковому номеру элемента в заявляемом устройстве.

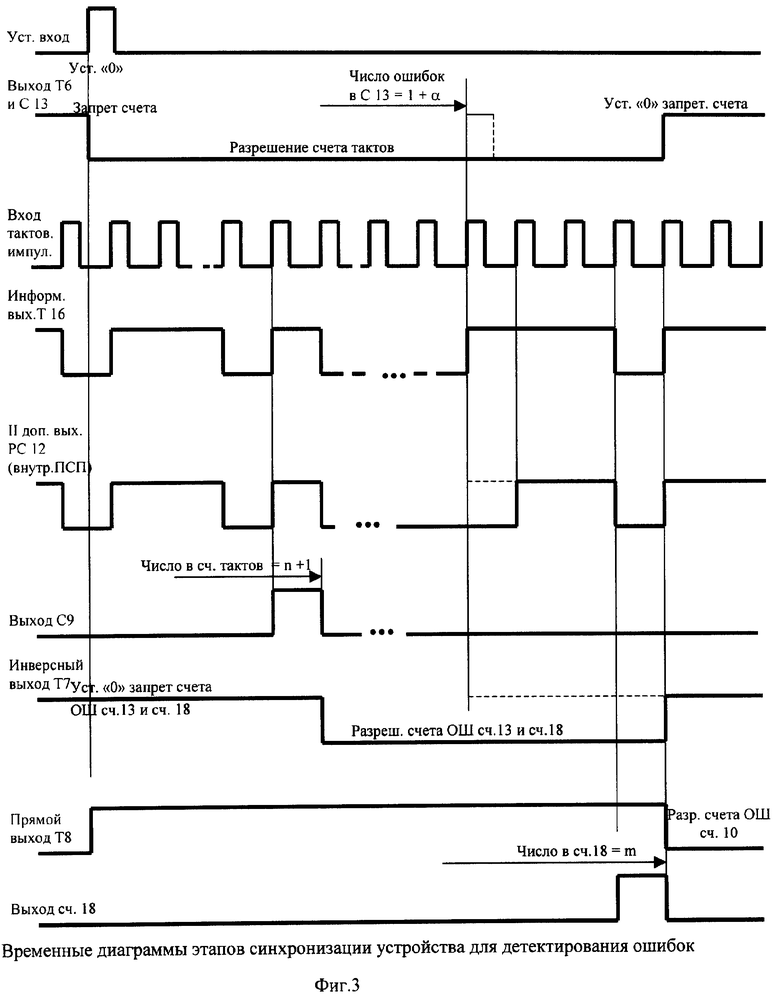

На фиг.3 представлены временные диаграммы этапов синхронизации устройства для детектирования ошибок.

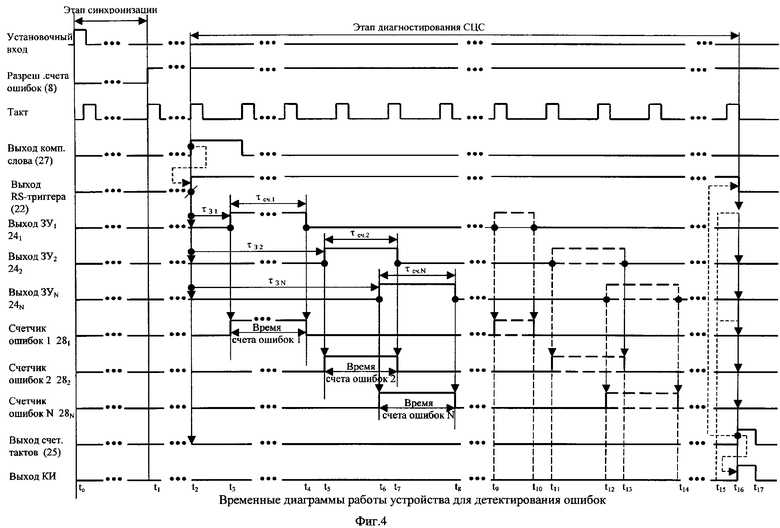

На фиг.4 представлены временные диаграммы работы устройства для детектирования ошибок.

Устройство построено следующим образом: первый СМД 1 подключен к входу второго СМД 2, второй вход которого соединен с выходом третьего СМД 3, первый и второй входы которого подключены соответственно к первому и второму выходу PC 12, третий выход которого соединен с одним из входов компаратора 17, а первый вход 1-го разряда подключен ко второму входу СМД 2, первый вход СМД 1 соединен с выходом триггера 5, выход СМД 2 подключен к установочному входу устройства и к R-входу триггера 6, прямой выход которого соединен с R-входом триггера 7, с S-входом триггера 8, первым входом счетчика 9, выход которого подключен к С-входу триггера 7, а второй вход является тактовым входом устройства, выход компаратора 17 соединен с первым входом счетчика 10, второй вход которого подключен к прямому выходу триггера 8, инверсный выход которого соединен с S-входом триггера 6; первый вход счетчика 10 подключен также к первому входу элемента «И» 11, к выходу устройства; второй вход счетчика 10 подключен также ко второму входу элемента «И» 11, третий вход которого соединен с инверсным выходом триггера 7 и третьим входом счетчика 13, первый вход которого подключен к выходу компаратора 17, второй вход - к третьему управляющему входу (управление модулем счета (1+α)) устройства, а выход - к прямому выходу триггера 6; выход элемента «И» 11 соединен со вторым входом СМД 14, первый вход которого подключен к третьему выходу PC 12, а выход - к второму информационному входу (2-го разряда) PC 12, вход управления которого соединен с первым управляющим входом (обратная связь 1-го разряда) устройства, информационный вход которого подключается к входу D-триггера 15, прямой выход которого соединен с входом D-триггера 16, вторым входом СМД 1 и первым входом компаратора 4, а выход триггера 16 соединен с другим входом компаратора 17; входы С триггеров 15 и 16 соединены между собой и подключены к входу тактовых импульсов устройства и к первому входу счетчика 18, второй вход которого соединен с инверсным выходом триггера 7, третий вход является вторым управляющим входом (модулем счета m) устройства, а выход подключен к входу С триггера 8, выход компаратора 4 соединен с D-входом триггера 5, а второй вход подключен к первому входу (1-го разряда) PC 12; первый вход второго элемента «И» 19 соединен со вторым входом СМД 14, второй вход - с первым управляющим входом (обратной связью 1-го разряда) устройства, а выход - с третьим входом СМД 3, первый вход элемента «ИЛИ» 20 соединен с выходом счетчика 25, который является также выходом устройства «КОНЕЦ ИЗМЕРЕНИЯ», второй его вход соединен с установочным входом устройства, который одновременно соединен с первыми входами счетчика 25, компаратора 27 и счетчиков 281, 282, ...28N ошибок (где N - число блоков или узлов контролируемого объекта, в которые вводят управляющее воздействие), выход элемента «ИЛИ» 20 соединен с входом R-триггера 22, а S-вход этого триггера подключен к выходу коммутатора 23, первый вход которого подключен к выходу компаратора 27, его второй вход соединен с выходом элемента «И» 21, его третий управляющий вход является управляющим входом устройства; первый вход элемента «И» 21 является внешним запускающим входом устройства, а его второй вход соединен с инвертирующим выходом триггера 8, который также соединен со вторым входом компаратора 27 и является выходом «РАЗРЕШЕНИЕ ЗАПУСКА» устройства; выход триггера 22 соединен с входами блоков 241, ...24N запуска и со вторым входом счетчика 25, а третий вход этого счетчика соединен с тактовым входом устройства, который также соединен с третьим входом компаратора 27; четвертый вход счетчика 25 является входом «ДЛИТЕЛЬНОСТЬ КОНТРОЛЯ» устройства; четвертый вход компаратора 27 соединен с четвертым выходом регистра 12 сдвига, а его пятый вход является входом «ЗАПУСКАЮЩЕЕ СЛОВО» устройства; выход блока 241 запуска подключен к входу исполнительного устройства 261 и ко второму входу счетчика 281 ошибок, а третий вход этого счетчика соединен с выходом компаратора 17, который подключен одновременно к третьим входам счетчиков 282, 283, ...28N, вторые входы каждого из этих счетчиков соединены соответственно с выходами блоков 242, 243, ...24N запуска, которые также соответственно подключены и к входам исполнительных устройств 262, 263, ...26N, выходы всех исполнительных устройств являются выходами устройства и подключаются к соответствующим устройствам диагностируемой системы цифровой связи для включения возмущающих воздействий; выходы счетчиков ошибок 281, 282, ...28N, счетчика ошибок 10 являются выходами ошибок устройства.

Устройство для детектирования ошибок работает следующим образом.

После включения устройства импульс начальной установки (момент времени t0, фиг.4). поданный на установочный вход устройства, устанавливает триггеры 6, 7, 8, 22, счетчики 9, 13, 18, 25, 281, ...28N, компаратор 27 в исходное состояние, при котором на выходе счетчиков 9, 18, 25, на прямом выходе 1 триггера 6 и на выходе компаратора 27 устанавливается уровень «лог.0», а на прямом выходе триггера 8 и на выходе Т7 - уровень «лог.1», а счетчики 9, 13, 18, 281, ...28N устанавливаются в ну левое состояние, а в счетчик 25 записывается число с его четвертого входа, определяющее длительность этапа диагностирования в тактах. С этого момента начинается этап синхронизации (фиг.3).

При подаче сигнала «лог.1» на первый управляющий вход устройства управляющий выходом разряда 12.1 регистра 12 сдвига сигнал «лог.1» (высокий потенциал) открывает элементы «И» 12.3 и 19. На их выходе появляется сигнал «лог.0» или «лог.1» в зависимости от того, какой сигнал поступает на их вторые входы. При подаче сигнала «лог.0» на первый управляющий вход устройства управляющий выходом разряда 12.1 регистра 12 сдвига сигнал «лог.0» (низкий потенциал) закрывает элементы «И» 12.3 и 19, т.е. на их выходах всегда присутствует сигнал «лог.0», что равносильно отключению сигнала с выхода разряда 12.1 регистра 12 сдвига и сигнала ошибки от третьего сумматора 3. Модуль счета четвертого счетчика 18, равный числу (m), и модуль счета третьего счетчика 13, и равный числу (1+α), устанавливается предварительно сигналами управления на соответствующих управляющих входах устройства. Второй компаратор 17 начинает сравнение входной внешней псевдослучайной последовательности (ПСП), поступающей через триггеры 15, 16 и формируемой на третьем выходе регистра 12 сдвига (выход разряда 12.1) внутренней ПСП. При этом импульсы ошибок с выхода второго компаратора 17 проходят на третий счетчик 13 и на первый элемент «И» 11. Последний открыт уровнями «лог.1» с инверсного выхода третьего триггера 7 и прямого выхода четвертого триггера 8. Поэтому импульсы ошибок воздействуют на регистр 12 сдвига через четвертый сумматор 14 до тех пор, пока первый счетчик 9 не досчитает число тактовых импульсов до (n+1). Если при этом в разрядах 12.1 и 12.2 регистра 12 сдвига записана безошибочная информация, т.е. регистр сдвига 12 устройства войдет в синхронизм с регистром сдвига передатчика (не показан), то на следующем этапе, когда на инверсном выходе третьего триггера 7 установится «лог.0» и разрешен счет тактов четвертым счетчиком 18 и счет ошибок третьим счетчиком 13, а первый элемент «И» 11 закрыт, третий счетчик 13 за число тактовых периодов m, при правильном выборе m и (1+α), не достигает до своего модуля счета (1+α) (при ожидаемом распределении ошибок во входной ПСП). На выходе четвертого счетчика 18 появится импульс, который установит «лог.0» на прямом выходе четвертого триггера 8, который закроет первый элемент «И» 11 и разрешит счет ошибок вторым счетчиком 10, т.е. третий этап синхронизации закончится.

Если на втором этапе синхронизации в регистре сдвига 12 записана хотя бы одна ошибка, которая принята во входной ПСП, то на третьем этапе синхронизации третий счетчик 13 за число тактовых периодов m успевает досчитать до своего модуля счета (1+α), и положительный импульс на его выходе установит устройство в исходное состояние.

Такой процесс повторяется до тех пор, пока регистр сдвига 12 устройства не войдет в синхронизм с регистром сдвига «передатчика» (не показан). После этого устройство работает как детектор ошибок входной внешней ПСП.

После вхождения в синхронизм детектора ошибок (момент времени t1, фиг.4) на инвертирующем выходе четвертого триггера 8 устанавливается сигнал «лог.1», который разрешает работу компаратора 27, сообщает пользователю о готовности устройства к детектированию ошибок и разрешает прохождение внешнего запуска через третий элемент «И» 21.

При внутреннем запуске выход коммутатора 23 подключен к выходу компаратора 27. После прихода разрешающего сигнала по его третьему входу компаратор 27 начинает сравнение поступающей на его четвертый вход ПСП с запускающим словом, присутствующим на его пятом входе. При совпадении содержания запускающего слова с фрагментом ПСП появляется импульсный сигнал «лог.1» на выходе компаратора 27 (момент времени t2, фиг.4).Этот сигнал устанавливает выход седьмого триггера 22 в состояние «лог.1», который дает разрешение на работу блоков 241, 242, ...24N запуска и работу счетчика 25 тактов. Каждый блок запуска имеет два регулируемых параметра: время задержки начала работы исполнительного устройства (времена: τз1=t3-t2; τз2=t5-t2; τзN=t6-t2) и время работы исполнительного устройства (и синхронное с ним время счета ошибок соответствующими счетчиками 281, 282, ...28N) - τсч.1=t4-t3; τсч.2=t7-t5; τсч.N=t8-t7.

В соответствии с выбранными параметрами τз и τсч. каждый блок запуска запускает работу своего исполнительного устройства 261, 262, ...26N и разрешает счет ошибок соответствующим счетчикам 281, 282, ...28N. Исполнительные устройства 261, 262, ...26N включают возмущающее воздействие на «свои» устройства диагностируемой системы цифровой связи. Возмущающие воздействия должны приводить к небольшому увеличению количества ошибок в диагностируемой последовательно-параллельной цепи устройств системы цифровой связи относительно ее фонового значения.

За один этап диагностирования каждое исполнительное устройство может запускаться многократно (моменты времени t9; t15 для первого исполнительного устройства 261; момент времени t11 для второго исполнительного устройства 262; момент времени t12 для N-го исполнительного устройства 26N; фиг.4) и тем самым в соответствующем счетчике ошибок 281, 282, ...28N можно накапливать ошибки.

Этап диагностирования заканчивается, когда содержание счетчика тактов 25 окажется нулевым и на его выходе появится сигнал «лог.1», который через первый вход элемента «ИЛИ» 20 поступит на R-вход седьмого триггера 22 и установит сигнал «лог.0» на его выходе и тем самым будет заблокирована дальнейшая работа блоков запуска 241, 242, ...24N, исполнительных устройств 261, 262, ...26N и счетчиков ошибок 281, 282, ...28N. Одновременно сигнал «лог.1» с выхода счетчика 25 сообщает пользователю об окончании этапа диагностирования и возможности считывания количества ошибок со счетчиков 281, 282, ...28N (выходы «ВЫХОД ОШ 1», «ВЫХОД ОШ 2», «ВЫХОД ОШ N»).

Таким образом, каждому блоку системы цифровой связи будет поставлена в соответствие некоторая величина ошибок. Эта величина будет зависеть от исправности блока. Если предварительно у заведомо исправной системы цифровой связи произвести возмущающие воздействия на ее блоки и записать показания счетчиков ошибок 281, 282, ...28N (фоновое количество ошибок), то сравнивая полученное количество ошибок i-го блока (i=1, 2, ...N) контролируемой системы цифровой связи с фоновым количеством ошибок этого же блока при таком же воздействии, можно сделать вывод о его исправности.

Таким образом, появляется возможность определения места возникновения ошибок в последовательно-параллельной цепи устройств системы цифровой связи и, следовательно, возможность диагностики такой системы с точностью до неисправной части (блока, узла и т.д.).

Кроме внутреннего запуска в устройстве может быть использован внешний запуск. При этом выход коммутатора 23 соединяется с его вторым входом.

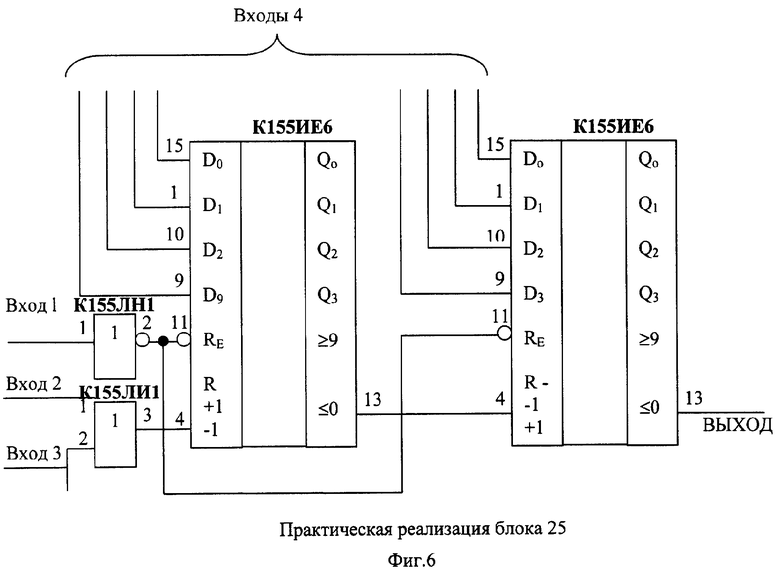

Практическая реализация блоков предлагаемого устройства может быть выполнена следующими способами:

- блоки 1÷19 - аналогично соответствующим блокам по прототипу;

- блок 20 - на элементах 2 «ИЛИ», входящих в состав микросхемы К155ЛЛ1, входы элемента - выводы 1, 2, выход - вывод 3, питание - вывод 14 (+5 вольт), корпус - вывод 7; [3]

- блок 21 - на элементах 2 «И», входящих в состав микросхемы К155ЛИ1, входы элемента - выводы 1, 2, выход - вывод 3, питание - вывод 14 (+5 вольт), корпус - вывод 7;

- блок 22 - на микросхеме К155ЛЕ1 в соответствии с фиг.5;

- блок 23 - на элементах микросхемы К155ЛР1 с последующим инвертированием выходного сигнала, вывод микросхемы 2 - вход 1, вывод микросхемы 4 - вход 2, выводы микросхемы 3 и 5, объединенные вместе - вход 3; питание - вывод 14 (+5 вольт), корпус - вывод 7;

- блоки 241÷24N - серийно выпускаемые генераторы Г5-82 [4, стр.189] с установкой на его выходе микросхемы 155ЛИ1, где на первый вывод микросхемы подключен выход генератора Г5-82, на ее второй вывод и на вход Г5-82 подается входной сигнал запускающего устройства с блока 22, выход микросхемы - выход блока, питание - вывод 14 (+5 вольт), корпус - вывод 7;

- блок 25 - на микросхемах серии К155 в соответствии с фиг.6;

- блоки 261÷26N - на логических элементах «НЕ» с открытым коллектором, входящими в состав микросхемы 155ЛИ2, входы элементов - выводы 1, 3, 5, 9, 11, 12, выходы - выводы 2, 4, 6, 8, 10, 13 соответственно, питание - вывод 14 (+5 вольт), корпус - вывод 7;

- блок 27 - на микросхемах серии К 155 (параллельных компараторах и регистрах сдвига) в соответствии с [5];

- блоки 281÷28N - на микросхемах К155ИЕ2 (двоично-десятичный 4-разрядный счетчик) и микросхемах К155ЛИ1. Первый вывод микросхемы К155ЛИ1 является первым входом счетчика ошибок, второй вывод этой же микросхемы является вторым входом счетчика ошибок, а третий вывод микросхемы К155ЛИ1 соединен с 14 выводом микросхемы К155ИЕ2 (вход С1), входы 2 и 3 (входы R0) микросхемы К155ИЕ2, соединенные вместе, являются третьим входом счетчика ошибок. Вывод 12 (выход Q0) этой же микросхемы соединен с ее выводом 1 (вход С2). Выводы 12, 9, 8, 11 являются выходами счетчика ошибок («Выход ОШ»). Для наращивания емкости счетчика до необходимого числа микросхемы К155ИЕ2 соединяются последовательно, при этом вывод 11 предыдущей микросхемы соединяется с выводом 14 последующей.

ЛИТЕРАТУРА:

1. Авторское свидетельство СССР №944123 кл. Н 04 В 3/46, 1980 г.

2. Авторское свидетельство СССР №1251335 кл. Н 04 В 3/46, 1985 г.

3. Авторское свидетельство СССР №1573545 кл. Н 04 В 3/46, 1990 г. (прототип).

4. Кирьянов К.Г. К теории сигнатурного анализа. Техника средств связи, сер. РИТ, вып.2, 1980 г.

5. Шило В.Л. Популярные цифровые микросхемы. Справочник, М., Радио и связь, 1987 г.

6. Каталог «Изделия промышленности средств связи», сер. Радиоизмерительные приборы, 1987/1988, издание 24-е, М., 1987 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| Устройство для детектирования ошибок | 1985 |

|

SU1251335A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Устройство для детектирования ошибок | 1988 |

|

SU1573545A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2270527C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК | 1996 |

|

RU2109405C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Устройство для распознавания сигналов объектов | 1989 |

|

SU1674183A1 |

| Компаратор | 1990 |

|

SU1755253A1 |

Изобретение относится к радиоизмерительной технике и может быть использовано для выделения ошибочных символов из информационной последовательности. Сущность устройства для детектирования ошибок состоит в определении места нахождения неисправности в последовательно-параллельной системе цифровой связи, что позволяет диагностировать такие системы по месту неисправности. Технический результат состоит в повышении помехоустойчивости и расширении функциональных возможностей. 6 ил.

Устройство для детектирования ошибок, содержащее последовательно соединенные первый компаратор, первый триггер, первый сумматор по модулю два, второй сумматор по модулю два, второй триггер, первый счетчик и третий триггер, регистр сдвига, четвертый триггер, первый вход и первый выход которого соединены соответственно с выходом второго триггера и вторым входом второго триггера, третий сумматор по модулю два, первый и второй входы и выход которого соединены соответственно с первым и вторым выходами регистра сдвига и вторым входом второго сумматора по модулю два и первым входом первого компаратора, второй счетчик, первый вход второго триггера является установочным входом устройства, тактовым входом которого является второй вход первого счетчика, выход второго триггера подключен также к второму входу третьего триггера, последовательно соединенные пятый триггер, первый вход которого является информационным входом устройства, шестой триггер, второй компаратор, второй вход которого соединен с третьим выходом регистра сдвига, первый элемент И и второй элемент И, выход которого соединен с третьим входом третьего сумматора по модулю два, четвертый вход которого соединен с четвертым выходом регистра сдвига, первый информационный вход которого соединен с выходом третьего сумматора по модулю два, четвертый сумматор по модулю два, первый и второй входы и выход которого соединены соответственно с третьим выходом регистра сдвига, выходом первого элемента И и вторым информационным входом регистра сдвига, третий счетчик, первый вход и выход которого соединены соответственно с выходом второго компаратора и вторым входом третьего триггера, выход пятого триггера соединен с вторыми входами первого компаратора и первого сумматора по модулю два, четвертый счетчик, первый вход которого соединен с вторыми входами пятого и шестого триггеров, подключен к тактовому входу устройства, второй вход второго элемента И соединен с управляющим входом регистра сдвига и является первым управляющим входом устройства, первый вход второго счетчика соединен с выходом второго компаратора и является выходом устройства, второй выход четвертого триггера подключен к вторым входам первого элемента И и второго счетчика, выход третьего триггера соединен с третьими входами первого элемента И и третьего счетчика и вторым входом четвертого счетчика, выход которого подключен к второму входу четвертого триггера, а третий вход четвертого счетчика является вторым управляющим входом устройства, третьим управляющим входом которого является второй вход третьего счетчика, отличающееся тем, что в него введены элемент ИЛИ, третий элемент И, седьмой триггер, коммутатор, третий компаратор, N исполнительных устройств, (N+1) счетчиков и N блоков запуска, первый вход элемента ИЛИ соединен с выходом пятого счетчика и является выходом "КОНЕЦ ИЗМЕРЕНИЯ" устройства, установочный вход которого соединен с вторым входом элемента ИЛИ, первым входом пятого счетчика, первым входом третьего компаратора и первыми входами от 6 до (N+5) счетчиков, выходы которых и выход второго счетчика являются выходами ошибок устройства, выход элемента ИЛИ соединен с R-входом седьмого триггера, S-вход которого подключен к выходу коммутатора, первый и второй входы которого соединены соответственно с выходом третьего компаратора и выходом третьего элемента И, а управляющий вход коммутатора является четвертым управляющим входом устройства, внешним запускающим входом которого является первый вход третьего элемента И, второй вход которого соединен с вторым входом третьего компаратора и с первым инвертирующим выходом четвертого триггера и является выходом "РАЗРЕШЕНИЕ ЗАПУСКА" устройства, выход седьмого триггера соединен с входами первого, второго, ...N-го блока запуска и с вторым входом пятого счетчика, третий вход которого соединен с третьим входом третьего компаратора и с тактовым входом устройства, четвертый вход третьего компаратора соединен с третьим выходом регистра сдвига, а пятый вход является входом "ЗАПУСКАЮЩЕГО СЛОВА" устройства, входом "ДЛИТЕЛЬНОСТЬ КОНТРОЛЯ" которого является четвертый вход пятого счетчика, выходы первого, второго, ...N-го блоков запуска подключены соответственно к входам первого, второго, ...N-го исполнительного устройства и к вторым входам соответственно шестого, седьмого, ...(N+5)-го счетчиков, третьи входы которых подключены к выходу второго компаратора, выходы исполнительных устройств являются выходами устройства.

| Устройство для детектирования ошибок | 1988 |

|

SU1573545A1 |

| Способ освобождения пустотных приборов от остаточных пустот | 1924 |

|

SU2479A1 |

| US 5796757 A, 18.08.1998 | |||

| Установка для выбивки литейных форм | 1980 |

|

SU884852A1 |

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

Авторы

Даты

2006-06-27—Публикация

2004-09-27—Подача