VJ

Ю

8

СА) О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1981 |

|

SU985962A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2344544C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Приемник многочастотных сигналов | 1985 |

|

SU1367170A1 |

Изобретение относится к радиотехнике и может быть использовано в системах передачи данных. Цель - повышение точности синхронизации в условиях воздействия интенсивных случайных помех. Устройство содержит дешифратор 1, распределитель 2, накопитель 31-Зм, счетчик 4 тактов, пороговый блок 5, блок 6 максимумов, блок 7 вычитания, блок 8 сравнения, элемент ИЛИ 9, элементы И Ют-Юм. Устройство позволяет установить синхронизацию с высокой точностью при достаточно сложной помеховой обстановке. Проверка синхронизации и её коррекции в случае сбоя производится постоянно. 3 ил. -........,. ..-.-. ..-. -...

Фие.Т

Йзобрётёняё относится к радиотехнике ..и может.бйт йШрлёзсв ано. в системах пе- р ёДачм данных . v:,.-,...,, ,.,,,,.:., .. ........

., /х Цель изобретения - повышение точности синхронизации в условиях воздействия 5 интенсивных случайных помех.

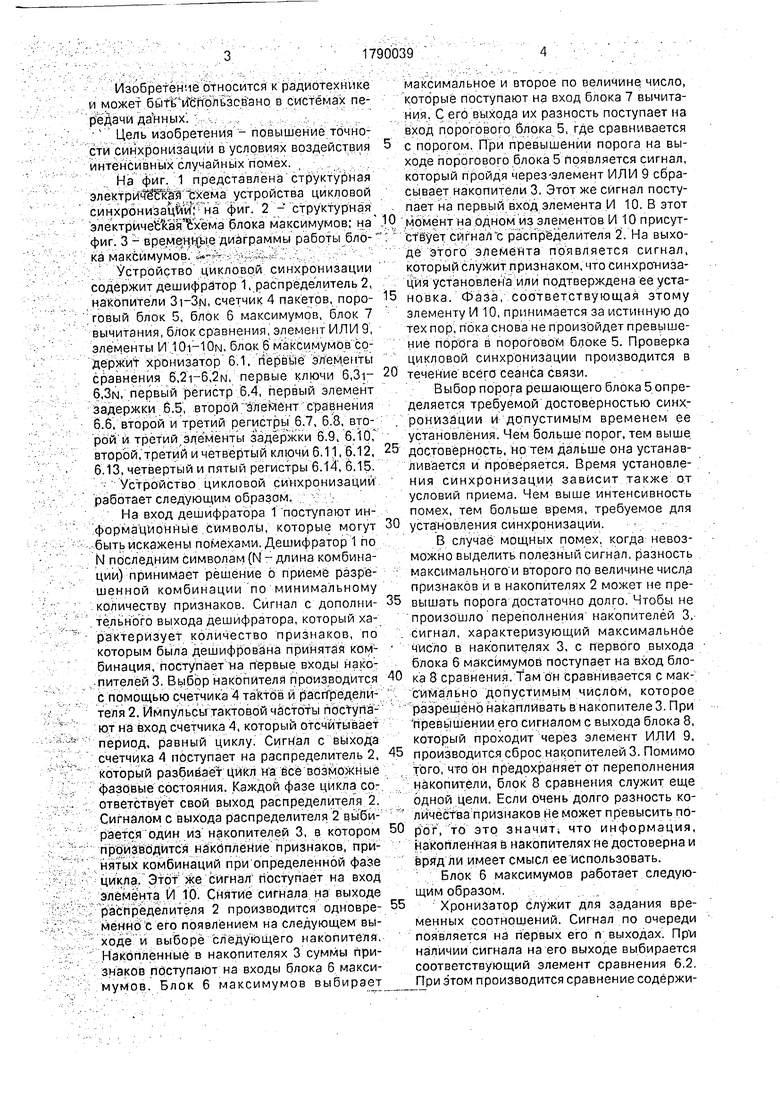

На фиг. 1 представлена структурная электри ч е й схема устройства цикловой синхрбнизацШ а фиг. 2 - структурная/ - электрйчеЬ1аяТхема блока максимумов; на ДО фиг. 3 - BpeMejH.Hbi,e диаграммы работы блб- :

:,( ка максимумов/&fc-i Ј&-Ј- ; .., ;.:;- , Устройство цикловой синхронизации содержит дешифратор 1 .распределитель 2, накопители 3|-3ы, счетчик 4 пакетов, поро- 15 . гов ый блок 5, блок 6 максимумов, блок 7 вычитания, блок сравнения, элемент ИЛИ 9, элементы l/1 .IOi-ION, блок 6 максимумов со- ,: держит хронизат.ор 6.1. первые элементы сравнения 6,21-6,2м, первые ключи 6,3i- 20 6,3м, первый регистр 6,4, первый элемент . задержки 6.5, второй Элемент сравнения : 6.6. второй и третий регистры 6.7, 6.8, вто- : рой й третий Элементы задержки 6.9. Б. 1.0Г . второй, третий и четвертый ключи 6.11,6.12, 25 6.13, четвертый и пятый регистры 6.14, 6.15. Устройство цикловой синхронизации . ; работает следующим образом, . : лНа вход дешифратора 1 прступают информационные символы, которые могут 30

- .-бытьискажены помехами. Дешифратор 1 по N последним символам (N - длина комбинации) принимает решение о приеме разрё- : . шенной комбинации по минимальному ;: :количеству признаков. Сигнал с дополни- 35 . тельного выхода дешифратора, который ха- г рактерйзует количество признаков, по которым была дешифрована принятая ком- бинация, поступает на первые входы нако- .пителёй 3. Выбор накопителя производится 40 с помощью счетчика 4 та Ктбв и расг ределй- : . теля 2. Импульсы тактовой частоты noctyna- ; ют на вход счетчика 4, который отсчитывает

период, равный циклу. Сигнал с выхода

счетчика А поступает на распределитель 2, 45 .-. который разбивает цикл ка ёсё вОзйожйыё фазовые состояния. Каждой фазе цикла со-. ответствует свой выход распределителя 2. Сигналом с выхода распределителя 2 цы би- рается Ьдин из накопителей 3, в котором 50 ; прЩЗШдйтся на кЬплёййе признаков, при- / ; унятых комбинаций при определенной фазе цик/ia, TOf Re сигнал поступает на вход . ;элемента И 10. Сняти ё сигнала на выходе с ::,: рас ripe делите л я 2 производится одновре- 55 ,. мённб с его появлением на следующем вы- . ; . ходе и выборе следующего накопителя. Накопленные в накопителях 3 суммы при- . знаков поступают на входы блока 6 макси- /: мумов. Блок 6 максимумов выбирае т

максимальное и второе по величине число, которые поступают на вход блока 7 вычитания, С его выхода их разность поступает на вход порогового блока 5, где Сравнивается с порогом. При превышении порога на выходе порогового блока 5 появляется сигнал, который пройдя через-элемент ИЛИ 9 сбрасывает накопители 3. Этот же сигнал поступает на первый вход элемента И 10. В этот момент на одном из элементов И 10 присут- стШует сигнал с распределителя 2. На выходе этого элемента появляется сигнал, который служит признаком, что синхро низа- ция установлена или подтверждена ее установка. Фаза, соответствующая этому элементу И 10, принимается за истинную до тех пор, пока снова не произойдет превышение поро га в пороговом блоке 5. Проверка Цикловой синхронизации производится в течение всего сеанса связи.

Выбор порога решающего блока 5 определяется требуемой достоверностью синхронизации и допустимым временем ее установления. Чем больше порог, тем выше, достоверность, но тем дальше она устанавливается и проверяется. Время установления синхронизации зависит также от условий приема. Чем выше интенсивность помех, тем больше время, требуемое для установления синхронизации.

В случае мощных помех, когда невозможно выделить полезный сигнал, разность максимального и второго по величине числа признаков и в накопителях 2 может не превышать порога достаточно долго. Чтобы не произошло переполнения накопителей 3.,- сигнал, характеризующий максимальное число в накопителях 3, с первого выхода блока 6 максимумов поступает на вход блока 8 сравнения. Там о н сравнивается с мак- с йма;льнр допустимым числом, которое разрешено накапливать в накопителе 3. При превышении его Сигналом с выхода блока 8, который проходит через элемент ИЛИ 9, производится сброс накопителей 3. Помимо того, что Он предохраняет от переполнения накопители, блок 8 сравнения служит еще одной цели. Если очень долго разность количества признаков не может превысить порог, то это значит; что информация, йакопленная в накопителях не достоверна и вряд ли имеет смысл ее использовать.

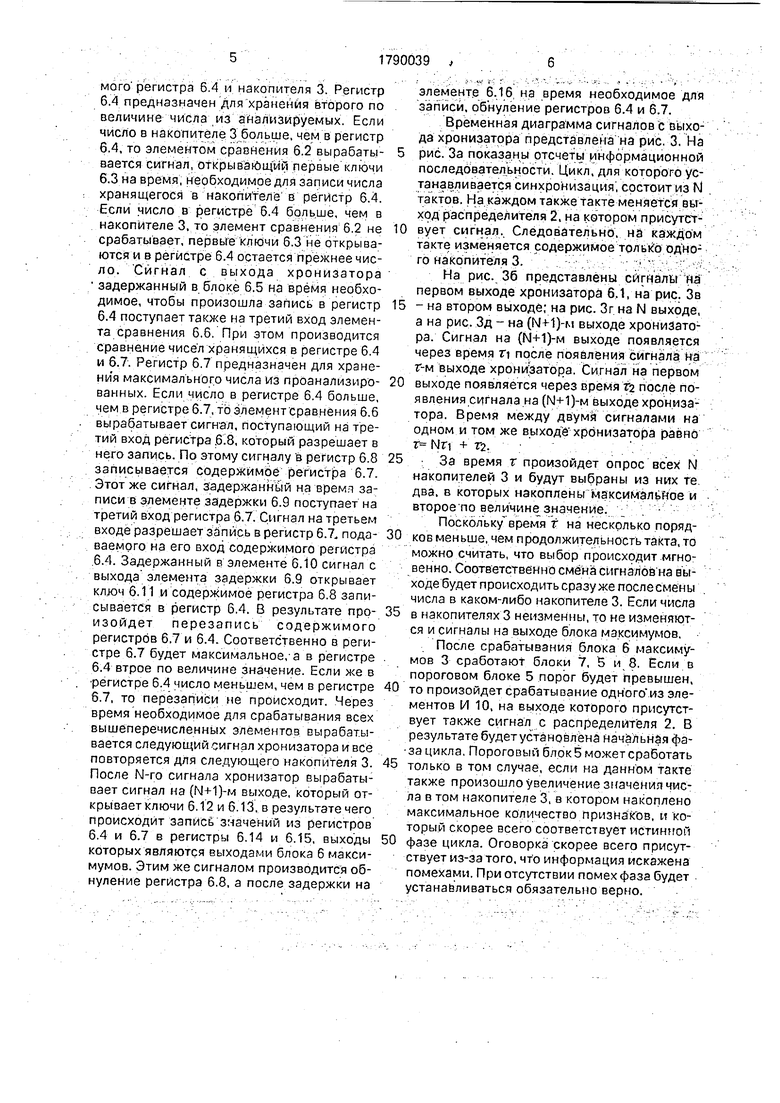

Блок 6 максимумов работает следующим образом.

Хронизэтор служит для задания временных соотношений. Сигнал по очереди появляется на первых его п выходах. Пр и наличии сигнала на его выходе выбирается соответствующий элемент сравнения 6,2. При этом производится сравнение содержимого регистра 6.4 и накопителя 3. Регистр 6.4 предназначен для хранения второго по величине числа из анализируемых. Если число в накопителе 3 больше, чем в регистр 6.4, то элементом сравнения 6.2 вырабатывается сигнал, открывающий первые ключи

элементе 6.16 на время необходимое для записи, обнуление регистров 6.4 и 6.7.

Временная диаграмма сигналов с выхода хронизатора представлена на рис. 3. На

рис. За показаны отсчеты информационной последовательности. Цикл, для которого устанавливается синхронизация , срстоитиз тактов. На каждом также такте меняется выход распределителя 2, на котором присутствует сигнал. Следовательно, на каждом

такте изменяется содержимое только одного накопителя 3. .. - :, v v. ; :;:; ::;.:-;:.

На рис. 36 представлены сигналы на

первом выходе хронизатора 6,1, на рис. Зв

- на втором выходе; на рис. Зг. на N выходе, а на рис. Зд - на (М+1)-м выходе хронизатора. Сигнал на (1М+1)-м выходе появляется через время ri после появления сигнала ШГ r-м выходе хронизатора. Сигнал на первом

выходе появляется через время тг после появления сигнала.на (N+1)-M выходе хронизатора. Время между двумя сигналами на одном и том же выходе хронизатора равно + гг.

. За время т произойдет опрос всех N накопителей 3 и будут выбраны из них те. два. в которых накоплены максимальное и второе/по величине значение. :: . Поскольку время t на несколько порядков меньше, чем продолжительность такта, то можно считать, что выбор происходит мгновенно. Соответственно смё1на сигналов на еы- ходе будет происходить сразу же после смены числа в каком-либо накопителе 3. Если числа

в накопителях 3 неизменны, то не изменяются и сигналы на выходе блока максимумов.

После срабатывания блока б максимумов 3 сработают блоки 7, 5 и 8. Если в пороговом блоке 5 порог будет превышен,

то произойдет срабатывание одного из элементов И 10, на выходе которого присутствует также сигнал с распределителя 2. В результате будет установлена начальная фа- за цикла. Пороговый блок 5 может сработать

только в том случае, если на данном такте также произошло увеличение значения числа в том накопителе 3, в котором накоплено максимальное количество признаков, и который скорее всего соответствует истинной

фазе цикла. Оговорка скорее всего присутствует из-за того, что информация искажена помехами. При отсутствии помех фаза будет устанавливаться обязательно верно.

Фо р.мула изобретения Я: Устройство цикловой синхронизации, сбде жащеё ёшиф рйтор/вх ШтЪрЬРй я ляётся входом информационных символов. N накопителей, кПервым входам которых подключён выход дешифратора, порбгрвый блбк и рбслёдоватёльно соединённые счет1 чйк тактов, вход которого является входом имттульйрб тактовойiчастоты, и распредели- тёль, выходы(которого пЪд ючены к втбрым входамf соответствующих накопителей, третьи входы которых соединены, б т;п й-; ч Ю lit ё е с я тем; что, с целью повышения точностйсинхронизацйЦв условиях воздействия интенсивных случайных помех, введё

5

ны блок максимумов, блок вычитания, блок сравнения, элемент ИЛИ, N элементов И, к первым входам которых и первому входу элемента ИЛ И подключен выход порогового блока, к входу котброго подключен выход блока вычитания, при этом вторые входы накопителей сбедйнёнц.с вторыми входами сЬотвётствующИх элементов И, а выходы на- кЬпйтёлёй подключены к входам блока мак- симумЬв, первый и второй выходы которого подключены к входам блока вычитания, причем второй выход блока максимумов через блок сравнения подключен к второму входу элемента ИЛИ, выход которого подключен к третьим входам накопителей.

| Устройство цикловой синхронизации | 1977 |

|

SU684757A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-01-23—Публикация

1991-03-14—Подача