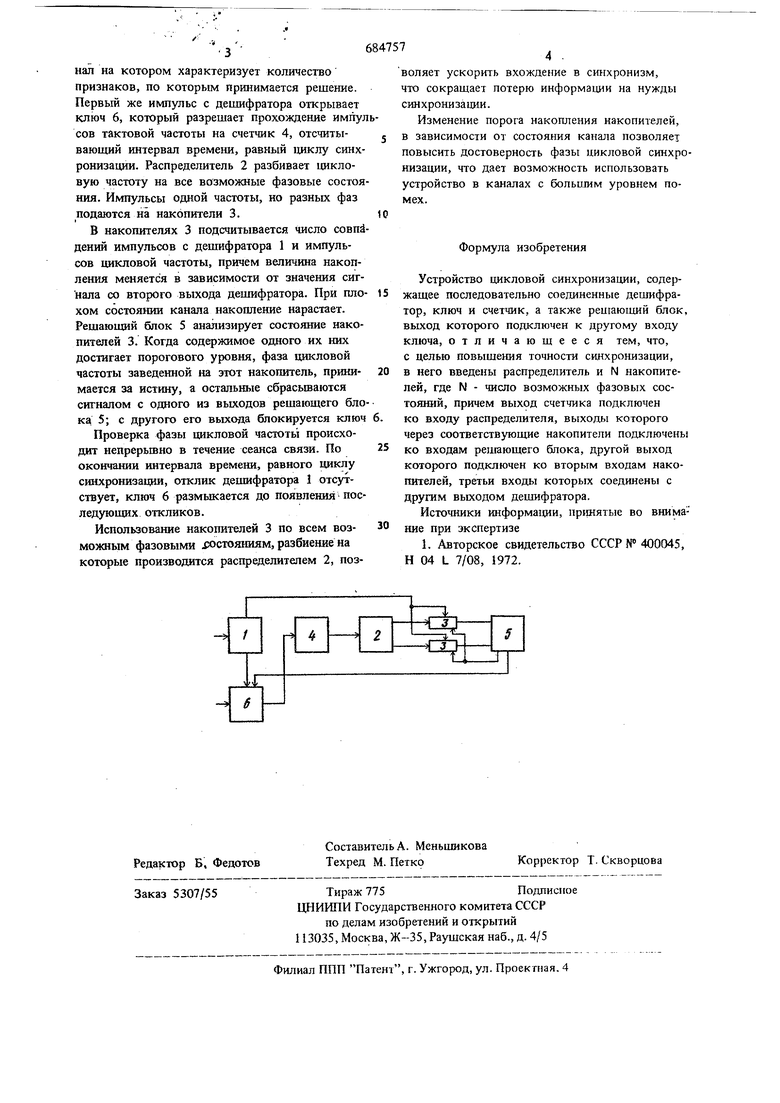

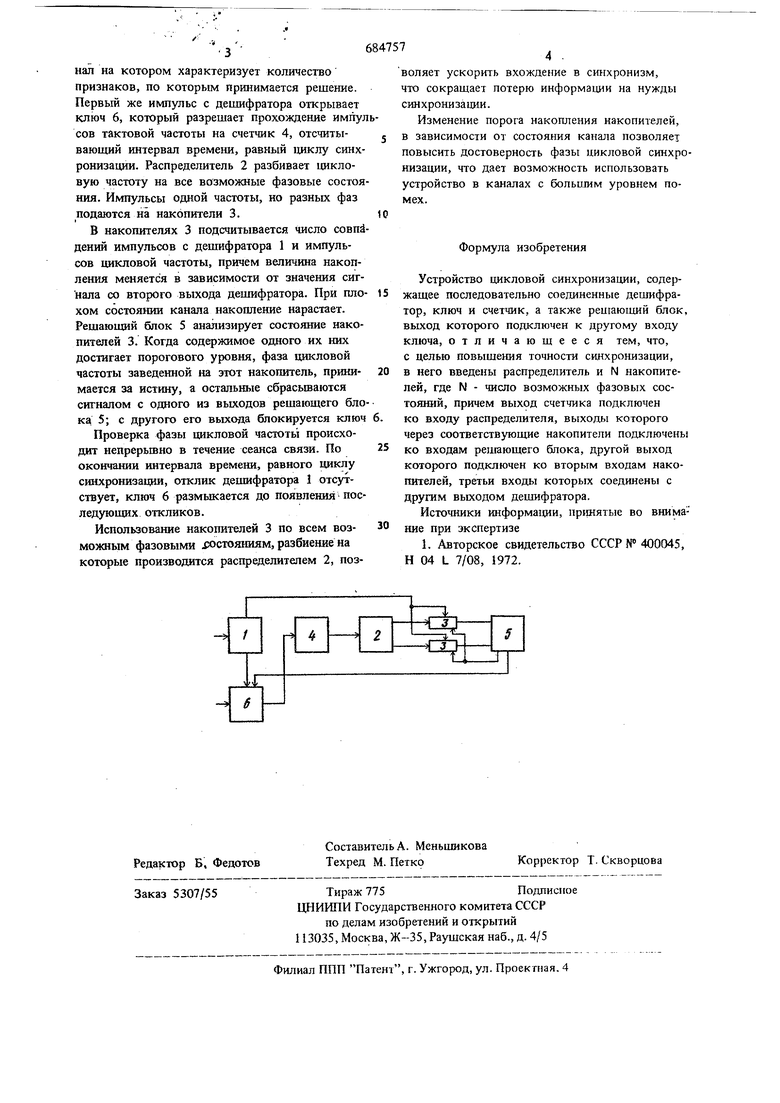

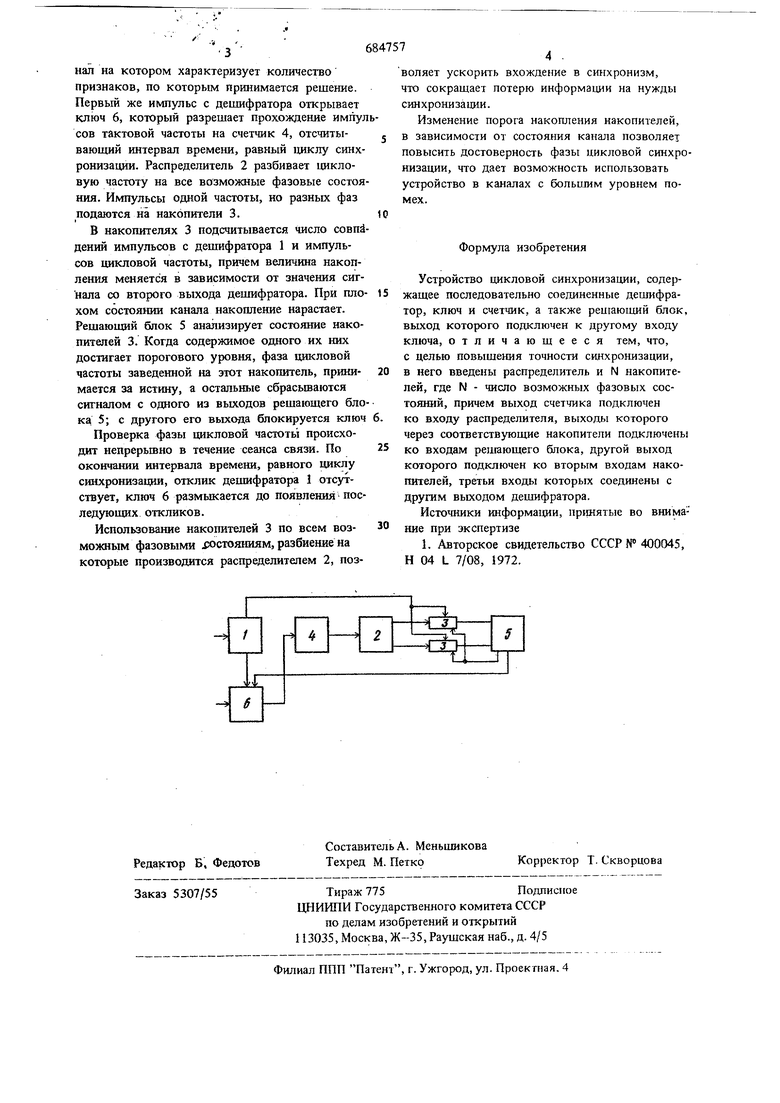

Изобретение относится к радиотехнике, может использоваться в системах передачи да1шы Известно устройство цикловой синхронизации, содержащее последовательно соединенные дешифратор, ключ и счетчик, а также решающ блок, выход которого подключен к другому входу ключа 1. Однако в известном устройстве подаваемая на вход дешифратора информация под воздействием помех может быть искажена двояко: либо неразрешенная комбинация трансформируется в разрешенную, либо часть признаков разрешенной комбинавди стирается. В первом случае дешифратор распознает трансформированную комбинацию, вследствие чего возможен сбой синхронизации. Во втором случае, даже при регулярном пропадании одного из признаков, устройство не может войти в синхронизм, так как депшфратор не может разпознать принимаемую информацию; Цель изобретения - повьаиение точности синхронизащш. Для этого в устройство цикловой синхронизации, содержащее последовательно соединенные дешифратор, ключ и счетчик, а также решающий блок, выход которого подключен к другому входу ключа, введены распределитель и N накопителей, где N - число возможных фазовых состояний, причем выход счетчика подключен ко входу распределителя, выходы которого через соответствующие накопители подключены ко входам решающего блока, другой выход которого подключен ко вторым входам накопителей, третьи входы которых соединены с другим выходом депшфратора. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство Ш1КЛОВОЙ синх{Юнизац11И содержит дешифратор 1, распределитель 2, N накопителей 3, счетчик 4, решающий блок 5, ключ 6. Устройство работает следую1Ш1м образом. На дешифратор 1 поступают информашюнные импульсы. Условия приема таковы, что возможны помехи типа вставок и стираний. Депшфратор принимает репшние о приеме разрешенной комбинаш{и по минимальному количеству признаков. Он имеет дополнительный выход, сигнал на котором характеризует количество признаков, по которым принимается решение. Первый же имнульс с дешифратора открывает ключ 6, который разрешает прохождение импулсов тактовой частоты на счетчик 4, отсчитывающий интервал времени, равный циклу синхронизации. Распределитель 2 разбивает цикловую частоту на все возможные фазовые состояния. Импульсы одной частоты, но разных фаз подаются на накопители 3.

В накопителях 3 подсчитывается число совпйдений импульсов с дешифратора 1 и импульсов цикловой частоты, причем величина накопления меняется в зависимости от значения сигнала со второго выхода дешифратора. При плохом состоявши канала накопление нарастает. Решающий блок 5 анализирует состояние накопителей 3. Когда содержимое одного их них достигает порогового уровня, фаза цикловой частоты заведенной на этот накопитель, принимается за истину, а остальные сбрасьшаются сигналом с одного из выходов решающего бло ка 5; с другого его выхода блокируется ключ

Проверка фазы цикловой частоты происходит непрерьтно в течение сеанса связи. По окончании интервала времени, равного циклу синхронизации, отклик дешифратора 1 отсутствует, ключ 6 размыкается до появления последующих откликов.

Использование накопителей 3 по всем возможным фазовыми .состояниям, разбиение на которые производится распределителем 2, позволяет ускорить вхождение в синхронизм, что сокращает потерю информации на нужды синхронизации.

Изменение порога накопления накопителей, в зависимости от состояния канала позволяет повысить достоверность фазы цикловой синхронизации, что дает возможность использовать устройство в каналах с больишм уровнем помех.

Формула изобретения

Устройство цикловой синхронизации, содержащее последовательно соединенные дешифратор, ключ и счетчик, а также решающий блок, выход которого подключен к другому входу ключа, отличающееся тем, что, с целью повышения точности синхронизации, в него введены распределитель и N накопителей, где N - число возможных фазовых состояний, причем выход счетчика подключен ко входу распределителя, выходы которого через соответствзтющие накопители подключены ко входам релгающего блока, другой выход которого подключен ко вторым входам накопителей, третьи входы которых соединены с другим выходом дешифратора.

Источники информации, прщятые во внимание при экспертизе

1. Авторское свидетельство СССР № 400045, Н 04 L 7/08, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1973 |

|

SU400045A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство синхронизации по циклам | 1980 |

|

SU886289A1 |

Авторы

Даты

1979-09-05—Публикация

1977-06-13—Подача