- к второму выходу счетчика, а выход - к второму входу счетчика, первому вхЬду вто- рого регистра и первому входу четвертого сумматора, второй вход которого подключен к генератору тактовых импульсов, а третий - к выходу второй группы элементов 2-2И-ИЛИ, первый вход которой подключен к выходу умножителя, второй вход - к выходу т(Ы|Рёра, третий :вход - к выходу триггера ч ерез греТий инвертор, четвертый вход - к выводу трер его егистра, соединенного с гтер|ым входом множителя, второй §ход схемы совпадения подключен к генератору тактовых импульсов, а выход- к второму входу второго регистра, первый вход второго инвертора-сумматора соединен с источником напряжения, первый вход второй группы элементов 1/1 подключен к выходу первого регистра, второй вход - к второму выходу первого инвертора-сумматора, а выход - к третьему входу второго регистра, первый вход третьей группы элементов 2-2И-ИЛИ соединен с первым выходом диодной матрицы, второй вход - с вторым выходом диодной матрицы, третий вход через третий инвертор-сумматор соединен с первым выходом диодной матрицы, а четвертый вход через четвертый инвертор соединен с вторым выходом диодной матрицы, выход третьей группы элементов 2-2И- ИЛИ подключен к первому входу третьего сумматора, к второму входу которого под- клю чён переключатель кода, а выход третьего сумматора соединен с вторым входом делителя, четвертым входом первой группы элементов 2-2И-ИЛ И и вторым входом второго инвертора-сумматора.

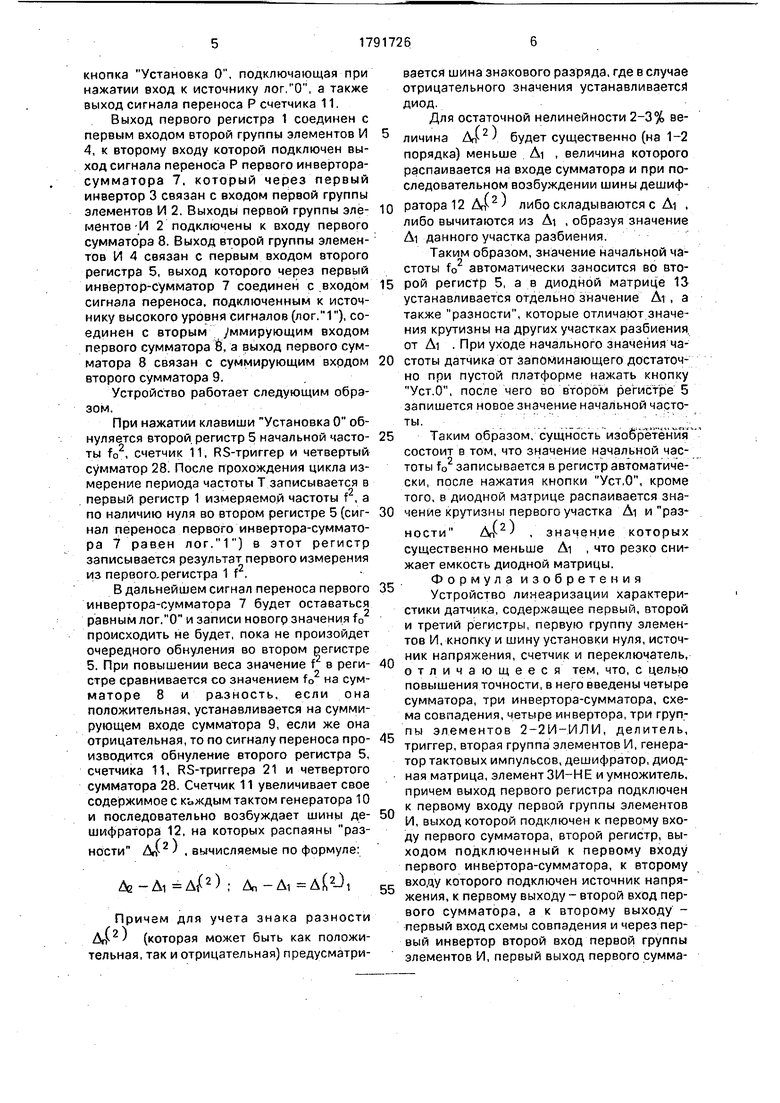

На чертеже представлена функциональная схема устройства.

Устройство содержит первый регистр 1, первую группу элементов И 2, первый инвертор 3, вторую группу элементов И 4, второй регистр 5, имеющий вход сигнала обнуления Р и счетный вход - С, схему совпадения 6, первый инвертор-сумматор 7 с входом сигнала переноса, подключенным к источнику высокого уровня сигнала лог.1, а выход Р - сигнала переноса связан с входом группы совпадения б и через первый инвертор 3-е входом первой группы элементов И 2, а также с входом второй группы элементов И 4. Первый сумматор 8, первый суммирующий вход которого связан с выходом пёрйой группы элементов И, второй вход - через первый инвертор-сумматор 7 с выходом второго регистра, а выход - с входом второго сумматора 9. Генератор тактовой частоты 10 подключен к счетному входу п-разрядного счетчика 11. Выходы счетчика 11 соединены с входными шинами дешифратора 12, подключенного к диодной матрице 13, емкостью 2 N х nf . Выходы диодной матрицы 13 соединены с первыми входами третьей группы элементов 2-2И-ИЛ И 14, на

вторые входы которой через третий инвертор-сумматор 15, имеющий вход сигнала переноса лог.1, подключенный к источнику высокого уровня сигналов, подключены входы диодной матрицы 13. Выход знакового

разряда диодной матрицы 13 через четвертый инвертор 16 соединен с первым управляющим входом третьей группы элементов 2-2Й-ИЛИ 14, выход которой связан с вторым суммирующим входом третьего сумматора 17, К первому суммирующему входу третьего сумматора 17. К первому суммирующему входу третьего сумматора 17 подсоединен установочный переключатель двоичного кода 18.

Первый управляющий вход первой группы элементов 2-2И-ИЛИ 19 через второй инвертор 20 связан с выходом сигнала переноса Р второго сумматора 9, который соединен с вторым управляющим входом

первой группы элементов 2-2И-ИЛИ 19 и с S-входом RS-триггера 21, Первые информационные входы первой группы элементов .2-2И-ЙЛИ 19 соединены с вторыми информационными входами этой группы через

второй инвертор-сумматор 22, подключенный к источнику высокого уровня сигналов (лог. Т ). Второй инвертор-сумматор 22 с ое- динен с вторым входом устройства деления 23, Первый вход устройства деления 23 сеян,

зан с выходом второго сумматора 9 а выход устройства деления 23 соединен с первым входом устройства умножения 24-, к второму входу которог.0 подключен выход третьего регистра 25, второй вход которого связан с

выходом второй группы элементов 2-2И- ИЛИ26. . .

Первый управляющий вход второй группы элементов 2-2И-ИЛИ 26 связан с выходом RS-триггера 21, который через третий

инвертор 27 соединен с вторыми управляющими входами второй группы элементов 2- 2И-ИЛИ 26, вторые входы которой связаны с выходом устройства умножения 24. Выходы второй группы элементов 2-2И-ИЛИ 26

подключены к четвертому сумматору 28, вход С которого связан с генератором тактовой частоты 10 и с первым входом схемы совпадения 6. Вход сигнала обнуления Р четвертого сумматора 28 соединен с выходом элемента ЗИ-НЕ 29, входом сигнала обнуления Р счетчика 11 и входом сигнала обнуления Р второго регистра 5. К входам элемента ЗИ-НЕ 29 подсоединены выход сигнала переноса Р первого сумматора 8,

кнопка Установка 0, подключающая при нажатии вход к источнику лог,О, а также выход сигнала переноса Р счетчика 11.

Выход первого регистра 1 соединен с первым входом второй группы элементов И

4. к второму входу которой подключен выход сигнала переноса Р первого инвертора- сумматора 7, который через первый инвертор 3 связан с входом первой группы элементов И 2. Выходы первой группы эле- ментов-И 2 подключены к входу первого сумматора 8. Выход второй группы элементов И 4 связан с первым входом второго регистра 5, выход которого через первый инвертор-сумматор 7 соединен с .входом сигнала переноса, подключенным к источнику высокого уровня сигналов (лог.1), соединен с вторым уммирующим входом первого сумматора 8, а выход первого сумматора 8 связан с суммирующим входом второго сумматора 9.

Устройство работает следующим образом.

При нажатии клавиши Установка 0 обнуляется второй регистр 5 начальной часто- ты fo2, счетчик 11, RS-триггер и четвертый сумматор 28. После прохождения цикла измерение периода частоты Т записывается в первый регистр 1 измеряемой частоты f , a по наличию нуля во втором регистре 5 (сиг- нал переноса первого инвертора-сумматора 7 равен лог.1) в этот регистр записывается результат первого измерения из первого.регистра 1 f .

В дальнейшем сигнал переноса первого инвертора-сумматора 7 будет оставаться равным лог.0 и записи нового значения f02 происходить не будет, пока не произойдет очередного обнуления во втором регистре

5. При повышении веса значение f в реги- стре сравнивается со значением f02 на сумматоре 8 и разность, если она положительная, устанавливается на суммирующем входе сумматора 9, если же она отрицательная, то по сигналу переноса про- изводится обнуление второго регистра 5, счетчика 11, RS-триггера 21 и четвертого сумматора 28. Счетчик 11 увеличивает свое содержимое с кьждым тактом генератора 10 и последовательно возбуждает шины де- шифратора 12, на которых распаяны разности Д|2 , вычисляемые по формуле:

Д2-Д1-Д/2); Дп-Д1 дЈ2Л

Причем для учета знака разности

Д|2 (которая может быть как положительная, так и отрицательная) предусматри5

10 15 20

5 0

5

0 5 0

5

вается шина знакового разряда, где в случае отрицательного значения устанавливается диод.

Для остаточной нелинейности 2-3% величина Arf2 будет существенно (на 1-2 порядка) меньше AI , величина которого распаивается на входе сумматора и при последовательном возбуждении шины дешифратора 12 либо складываются с Д| , либо вычитаются из Дт , образуя значение Дт данного участка разбиения.

Таким образом, значение начальной частоты f02 автоматически заносится во второй регистр 5, а в диодной матрице 13 устанавливается отдельно значение Дт, а также разности, которые отличают.значения крутизны на других участках разбиения, от Дт . При уходе начального значейия частоты датчика от запоминающего достаточно при пустой платформе нажать кнопку Уст.О, после чего во втором регистре 5 запишется новое значение начальной частоты. . Таким образом, сущность изобретения состоит в том, что значение начальной частоты f0 записывается в регистр автоматически, после нажатия кнопки Уст,0, кроме того, в диодной матрице распаивается значение крутизны первого участка Д| и разности Д|-2 , значение которых существенно меньше Дт , что резко снижает емкость диодной матрицы. Формула изобретения Устройство линеаризации характеристики датчика, содержащее первый, второй и третий регистры, первую группу элементов И, кнопку и шину установки нуля, источник напряжения, счетчик и переключатель, отличающееся тем, что, с целью повышения точности, в него введены четыре сумматора, три инвертора-сумматора, схема совпадения, четыре инвертора, три груп- пы элементов 2-2И-ИЛИ, делитель, триггер, вторая группа элементов И, генератор тактовых импульсов, дешифратор, диодная матрица, элемент ЗИ-НЕ и умножитель, причем выход первого регистра подключен к первому входу первой группы элементов И, выход которой подключен к первому входу первого сумматора, второй регистр, выходом подключенный к первому входу первого инвертора-сумматора, к второму входу которого подключен источник напряжения, к первому выходу - второй вход первого сумматора, а к второму выходу - первый вход схемы совпадения и через первый инвертор второй вход первой группы элементов И, первый выход первого сумматора подключен к первому входу второго сумматора, к второму входу которого подключён выход первой группы элементов 2- .2И-ИЛИ, к первому выходу - первый вход делителя, а к второму выходу - первый вход триггера, первый вход первой группы элементов 2-2И-ИЛИ и через второй инвертор второй вход этой группы, к третьему входу которой подключен выход второго1 pa-сумматора, первый вход которого соеди- нем с источником напряжения, выход генератора тактовых импульсов подключен к первому входу счетчика, первый выход которого через дешифратор подключен к входу диодной матрицы, второй выход первого сумматора подключен к первому входу элемента ЗИ-ИЕ, второй вход которого подключен через кнопку к шине установки нуля, третий вход - к второму выходу счетчика, а выход - к второму входу счетчика, первому входу второго регистра и первому входу четвертого сумматора, второй вход которого подключен к генератору тактовых импульсов, а третий - к выходу второй группы элементов 2-2И-ИЛИ, ггервый вход которой подключен к выходу умножителя, второй вход - к выходу триггера, третий вход -„к выходу триггера через третий инвертор, четвертый вход - к выходу третьего регистра,

соединенного с первым входом умножителя, второй вход которого подключен к выходу делителя, второй вход схемы совпадения подключен к генератору тактовых импульсов, а выход - к второму входу второго регистра,--, первый вход второго инвертора-сумматора соединен с источником напряжения, первый вход второй группы элементов И подключен к выходу первого регистра, второй вход - к второму выходу первого инвертора-сумматора, а выход - к третьему входу второго регистра, первый вход третьей группы элементов 2- 2И-ИЛИ соединен с первым выходом диодной матрицы, второй вход - с вторым выходом диодной матрицы, третий вход через третий инвертор-сумматор соединен с первым выходом диодной матрицы, а четвертый вход через четвертый инвертор соединен с вторым выходом диодной матрицы, выход третьей группы элементов 2-2Й- ИЛИ подключен к первому входу третьего сумматора, к второму входу которого подключен переключатель кода, а выход третьего сумматора соединен с вторым входом делителя, четвертым входом первой группы .элементов 2-2И-ИЛИ и вторым входом второго инвертора-сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1667214A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Электропривод постоянного тока | 1990 |

|

SU1741247A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Цифровой генератор сложных сигналов | 1986 |

|

SU1325451A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

/

8

Авторы

Даты

1993-01-30—Публикация

1990-05-31—Подача