Изобретение относится к области вычислительной техники и может быть использовано для микропрограммного управления устройств вычислительной техники.

Цель изобретения - сокращение аппаратурных затрат.

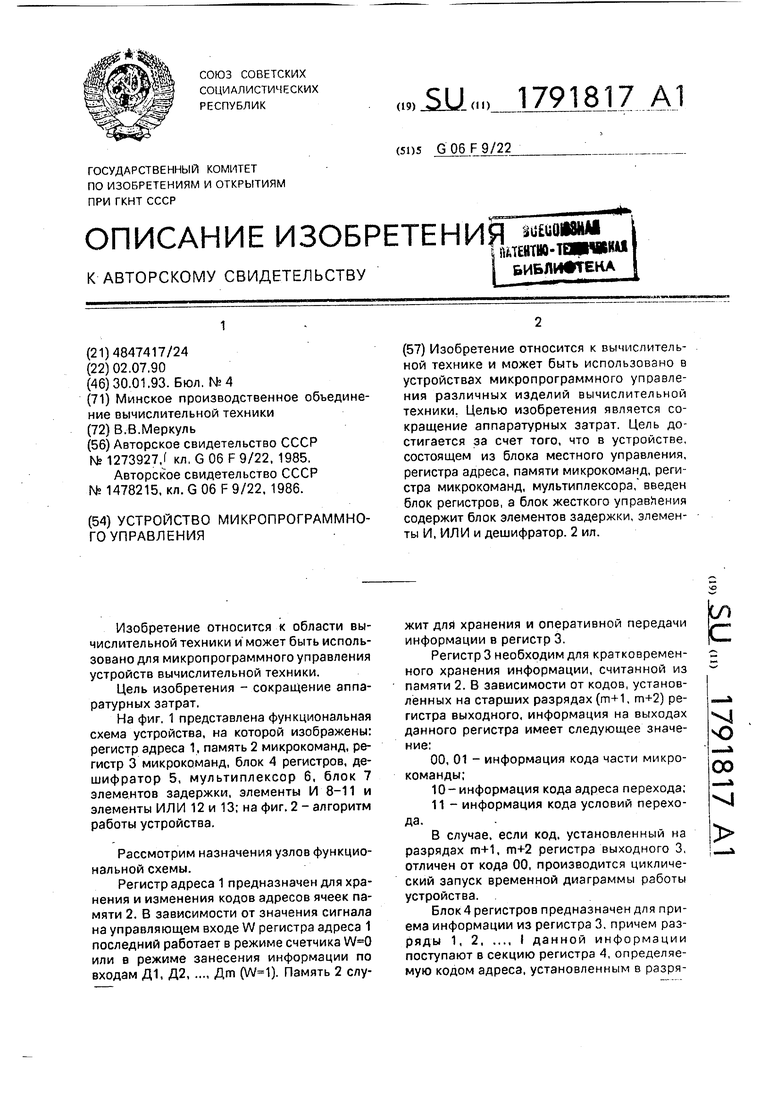

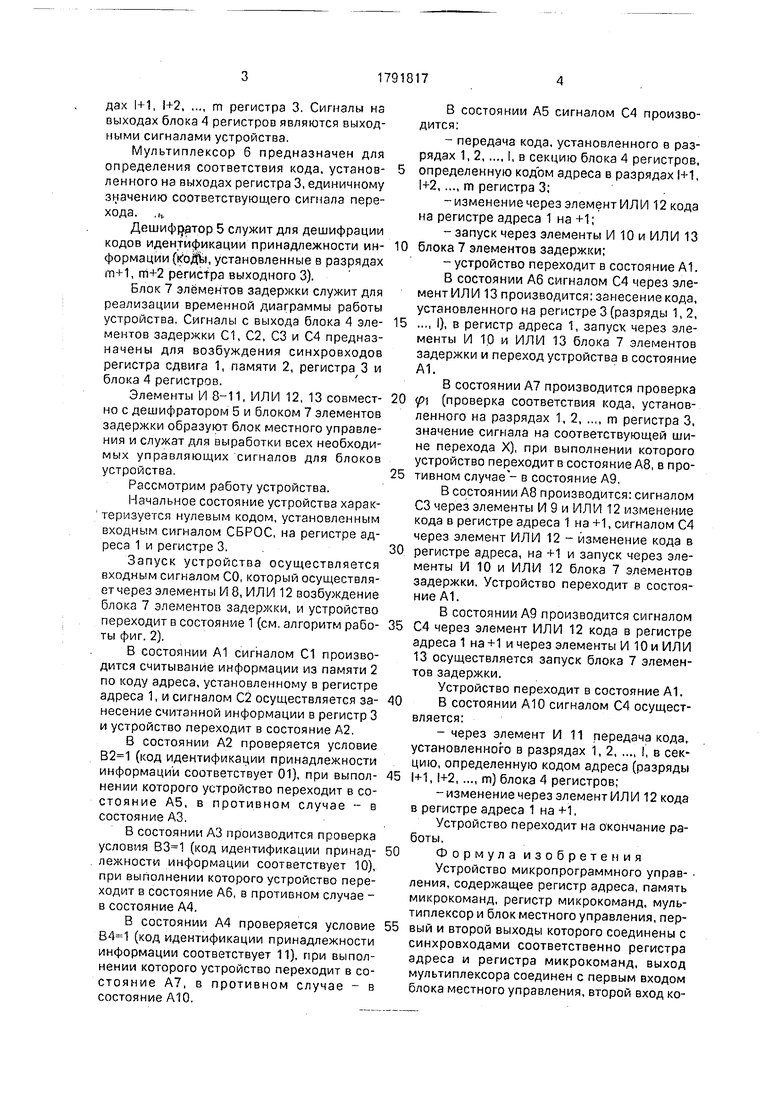

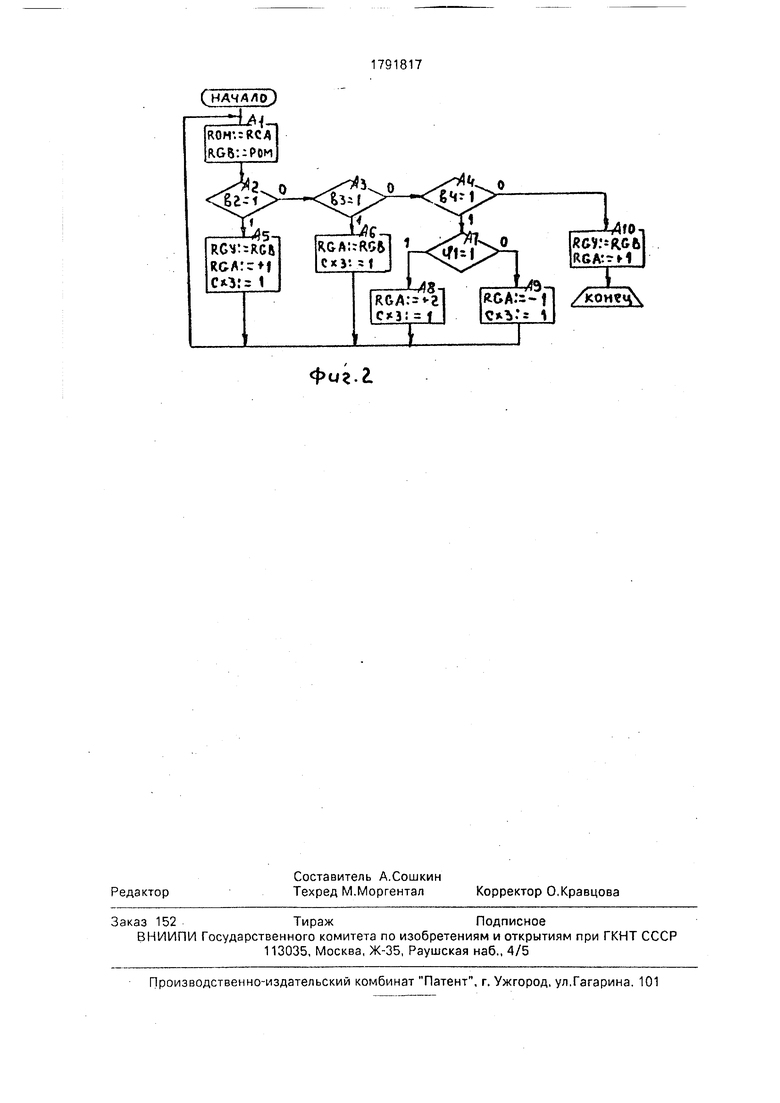

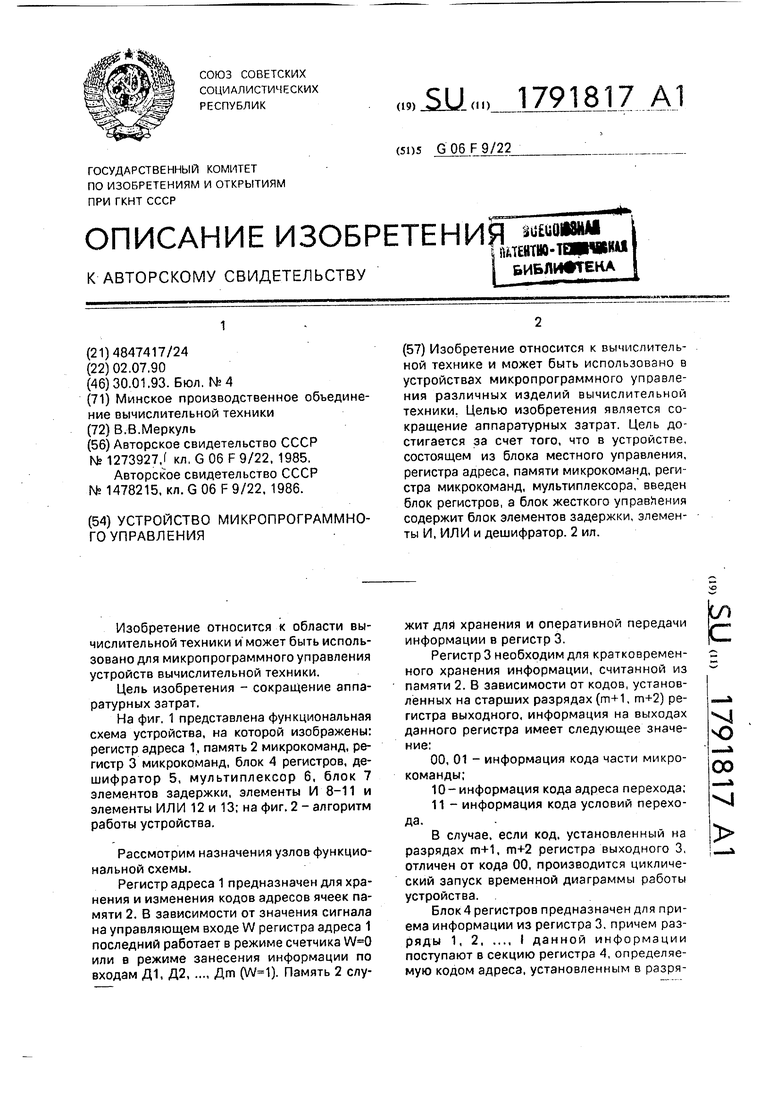

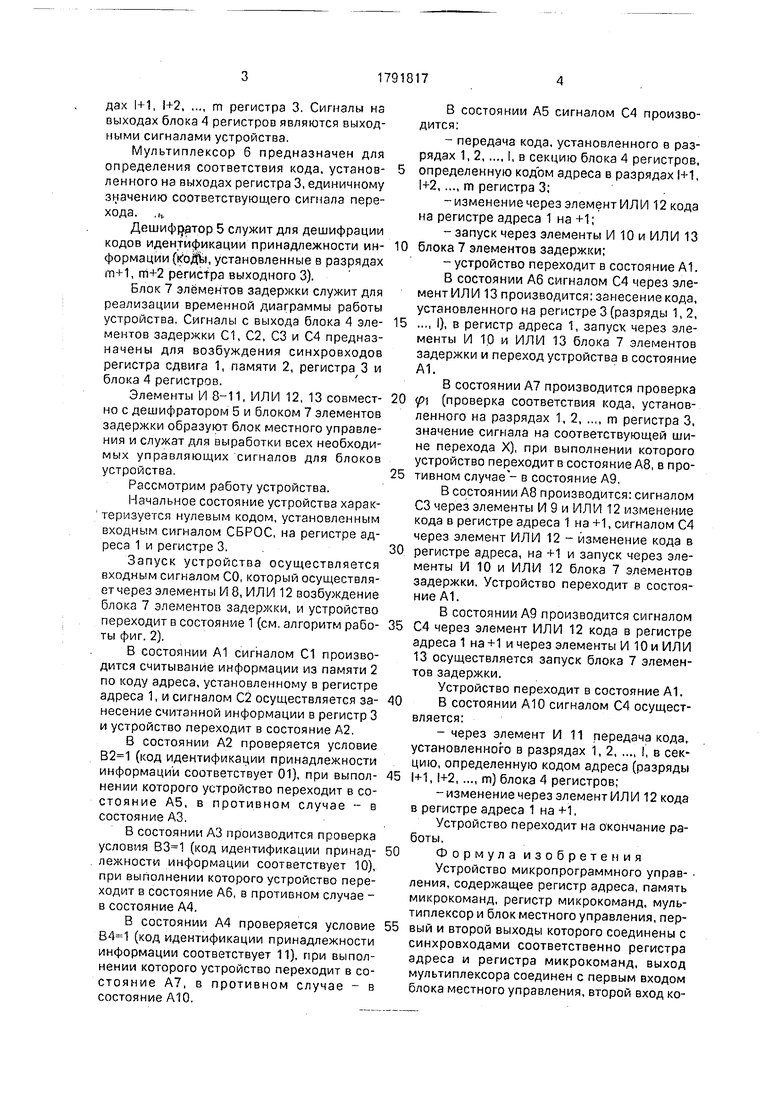

На фиг. 1 представлена функциональная схема устройства, на которой изображены: регистр адреса 1, память 2 микрокоманд, регистр 3 микрокоманд, блок 4 регистров, дешифратор 5, мультиплексор 6, блок 7 элементов задержки, элементы И 8-11 и элементы ИЛИ 12 и 13; на фиг. 2 - алгоритм работы устройства.

Рассмотрим назначения узлов функциональной схемы.

Регистр адреса 1 предназначен для хранения и изменения кодов адресов ячеек памяти 2. В зависимости от значения сигнала на управляющем входе W регистра адреса 1 последний работает в режиме счетчика или в режиме занесения информации по входам Д1, Д2Дт (). Память 2 служит дли хранения и оперативной передачи информации в регистр 3.

Регистр 3 необходим для кратковременного хранения информации, считанной из памяти 2. В зависимости от кодов, установленных на старших разрядах (m+1, m+2) регистра выходного, информация на выходах данного регистра имеет следующее значение:

00, 01 - информация кода части микрокоманды;

10- информация кода адреса перехода;

11 - информация кода условий перехода.

В случае, если код. установленный на разрядах m+1, m+2 регистра выходного 3. отличен от кода 00, производится циклический запуск временной диаграммы работы устройства.

Блок4 регистров предназначен для приема информации из регистра 3, причем разряды 1, 2 I данной информации

поступают в секцию регистра 4, определяемую кодом адреса, установленным в разрясл С

ю

00

дах 1+1, I+2 m регистра 3. Сигналы нз

выходах блока 4 регистров являются выходными сигналами устройства.

Мультиплексор б предназначен для определения соответствия кода, установленного на выходах регистра 3, единичному значению соответствующего сигнала перехода. ,fl.

Дешифратор 5 служит для дешифрации кодов идентификации принадлежности информации (Кода, установленные в разрядах m+1, rri+2 регистра выходного 3).

Блок 7 элементов задержки служит для реализации временной диаграммы работы устройства. Сигналы с выхода блока 4 элементов задержки С1, С2, СЗ и С4 предназначены для возбуждения синхровходов регистра сдвига 1, памяти 2, регистра 3 и блока 4 регистров.

Элементы И 8-11, ИЛИ 12, 13 совместно с дешифратором 5 и блоком 7 элементов задержки образуют блок местного управления и служат для выработки всех необходимых управляющих сигналов для блоков устройства.

Рассмотрим работу устройства.

Начальное состояние устройства характеризуется нулевым кодом, установленным входным сигналом СБРОС, на регистре адреса 1 и регистре 3.

Запуск устройства осуществляется входным сигналом СО, который осуществля- етчерез элементы I/I 8, ИЛИ 12 возбуждение блока 7 элементов задержки, и устройство переходит в состояние 1 (см, алгоритм работы фиг. 2),

В состоянии А1 сигналом С1 производится считывание информации из памяти 2 по коду адреса, установленному в регистре адреса 1, и сигналом С2 осуществляется занесение считанной информации в регистр 3 и устройство переходит в состояние А2.

В состоянии А2 проверяется условие (код идентификации принадлежности информации соответствует 01), при выполнении которого устройство переходит в состояние А5, в противном случае - в состояние A3.

В состоянии A3 производится проверка условия (код идентификации принад- . лежности информации соответствует 10), при выполнении которого устройство переходит в состояние А6, в противном случае - в состояние А4.

В состоянии А4 проверяется условие (код идентификации принадлежности информации соответствует 11), при выполнении которого устройство переходит в со- стояние А7, в противном случае - в состояние А10.

В состоянии А5 сигналом С4 производится:

-передача кода, установленного в разрядах 1, 2,.... , в секцию блока 4 регистров,

определенную кодом адреса в разрядах 1+1,

I+2m регистра 3:

-изменение через элемент ИЛ И 12 кода на регистре адреса 1 на +1;

-запуск через элементы И 10 и ИЛИ 13 блока 7 элементов задержки;

-устройство переходит в состояние А1. В состоянии А6 сигналом С4 через элементИЛИ 13 производится: занесение кода, установленного на регистре 3 (разряды 1, 2,

.,., I), в регистр адреса 1, запуск через элементы И 10 и ИЛИ 13 блока 7 элементов задержки и переход устройства в состояние А1.

В состоянии А7 производится проверка

f (проверка соответствия кода, установленного на разрядах 1, 2m регистра 3,

значение сигнала на соответствующей шине перехода X), при выполнении которого устройство переходит в состояние А8, в противном случае -в состояние А9.

В состоянии А8 производится: сигналом СЗ через элементы И 9 и ИЛИ 12 изменение кода в регистре адреса 1 на +1, сигналом С4 через элемент ИЛИ 12 - изменение кода в

регистре адреса, на +1 и запуск через элементы И 10 и ИЛИ 12 блока 7 элементов задержки. Устройство переходит в состояние А1.

В состоянии А9 производится сигналом

С4 через элемент ИЛИ 12 кода в регистре адреса 1 на +1 и через элементы И 10 и ИЛИ 13 осуществляется запуск блока 7 элементов задержки.

Устройство переходит в состояние А1.

В состоянии А10 сигналом С4 осуществляется:

-через элемент И 11 передача кода, установленного в разрядах 1, 2, в секцию, определенную кодом адреса(разряды

1+1, I+2,..., т) блока 4 регистров;

-изменение через элемент ИЛ И 12 кода в регистре адреса 1 на +1,

Устройство переходит на окончание работы.

Формула изобретения

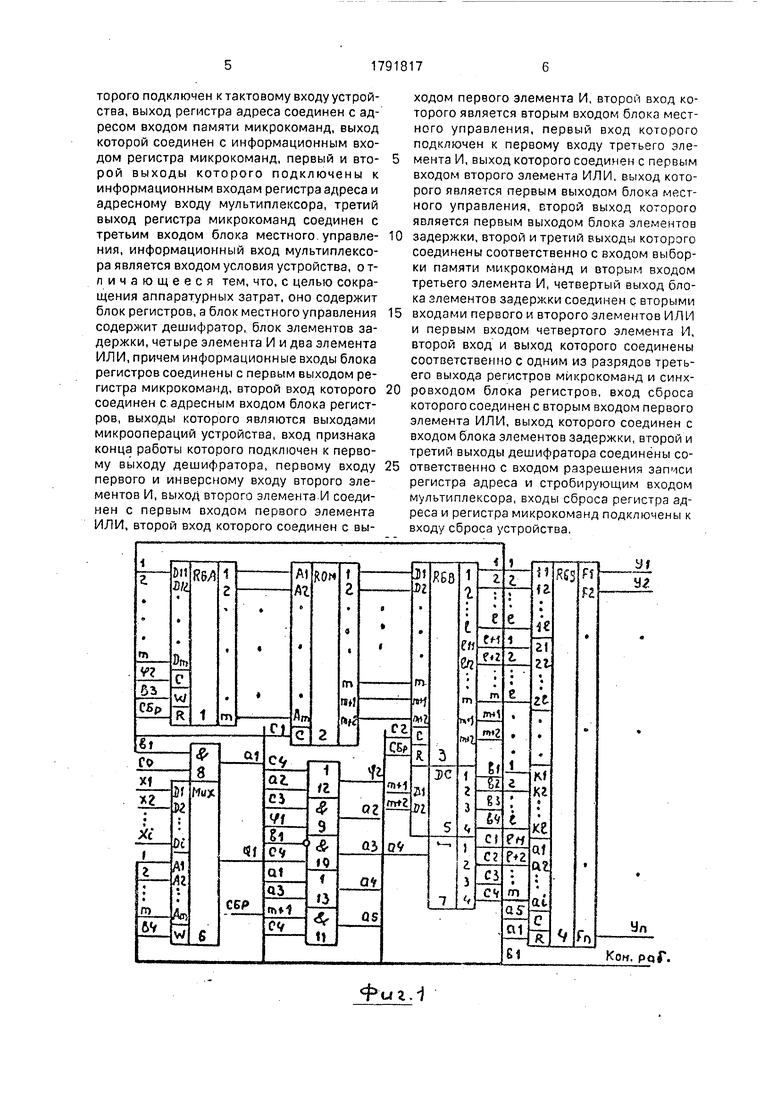

Устройство микропрограммного управления, содержащее регистр адреса, память микрокоманд, регистр микрокоманд, мультиплексор и блок местного управления, первый и второй выходы которого соединены с синхровходами соответственно регистра адреса и регистра микрокоманд, выход мультиплексора соединен с первым входом блока местного управления, второй вход которого подключен к тактовому входу устройства, выход регистра адреса соединен с адресом входом памяти микрокоманд, выход которой соединен с информационным входом регистра микрокоманд, первый и вто- рой выходы которого подключены к информационным входам регистра адреса и адресному входу мультиплексора, третий выход регистра микрокоманд соединен с третьим входом блока местного.управле- ния, информационный вход мультиплексора является входом условия устройства, о т- пичающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит блок регистров, а блок местного управления содержит дешифратор, блок элементов задержки, четыре элемента И и два элемента ИЛИ, причем информационные входы блока регистров соединены с первым выходом регистра микрокоманд, второй вход которого соединен с адресным входом блока регистров, выходы которого являются выходами микроопераций устройства, вход признака конца работы которого подключен к первому выходу дешифратора, первому входу первого и инверсному входу второго элементов И, выход второго элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, второй вход которого является вторым входом блока местного управления, первый вход которого подключен к первому входу третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ. выход которого является первым выходом блока местного управления, второй выход которого является первым выходом блока элементов задержки, второй и третий выходы которого соединены соответственно с входом выборки памяти микрокоманд и вторым входом третьего элемента И, четвертый выход блока элементов задержки соединен с вторыми входами первого и второго элементов ИЛИ и первым входом четвертого элемента И, второй вход и выход которого соединены соответственно с одним из разрядов третьего выхода регистров микрокоманд и синх- ровходом блока регистров, вход сброса которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом блока элементов задержки, второй и третий выходы дешифратора соединены соответственно с входом разрешения записи регистра адреса и стробирующим входом мультиплексора, входы сброса регистра адреса и регистра микрокоманд подключены к входу сброса устройства,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

Ф u г. }

СнАЧД/Чр

ЯОН .:ЯСЛ R.GBUPOH

ясл|

:РОИ|

фиг-i

| Устройство микропрограммного управления | 1985 |

|

SU1273927A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1478215A1 |

Авторы

Даты

1993-01-30—Публикация

1990-07-02—Подача