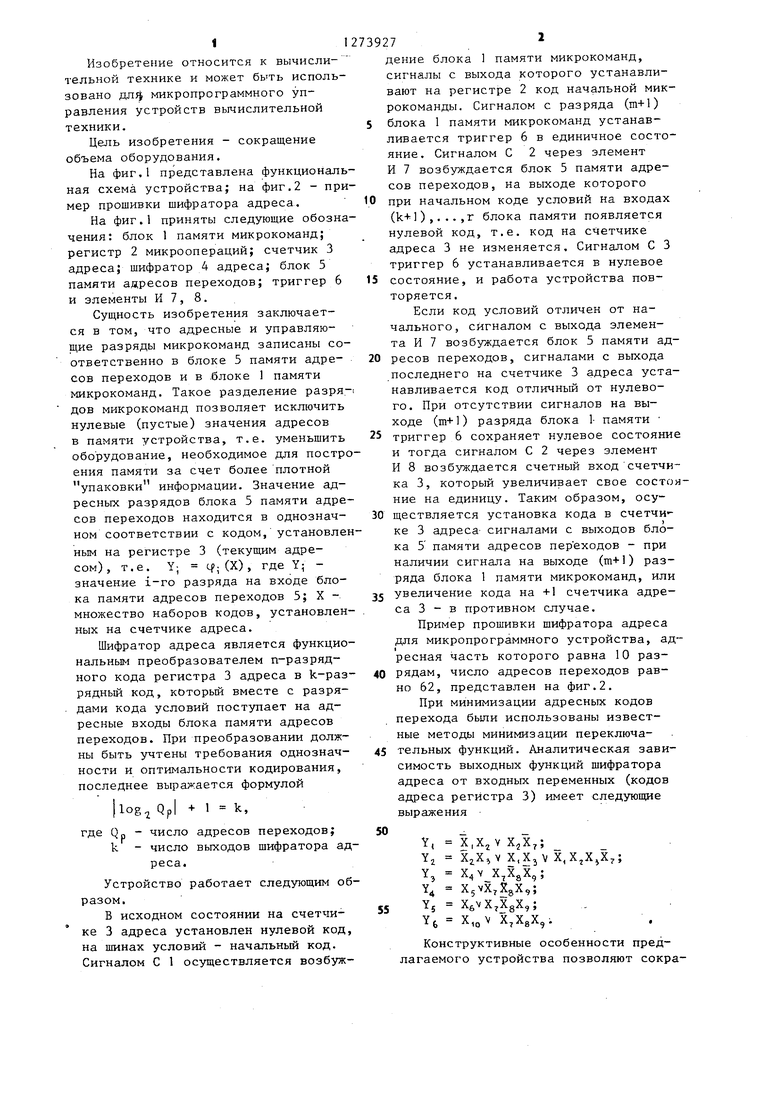

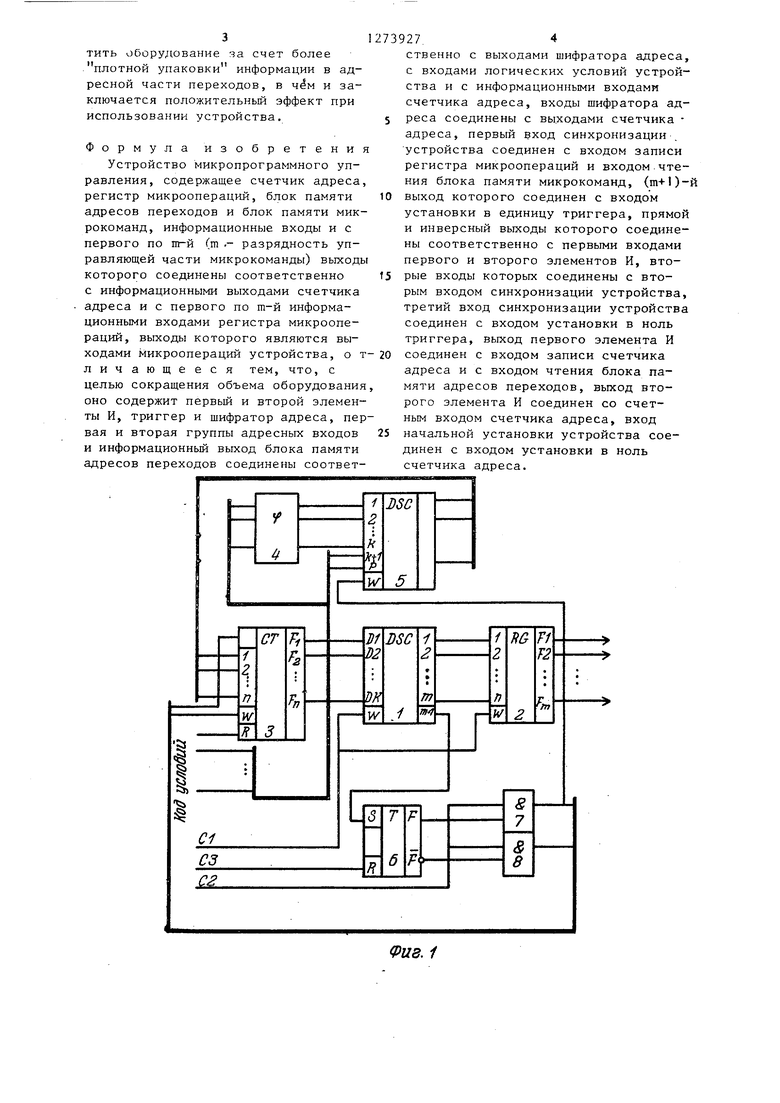

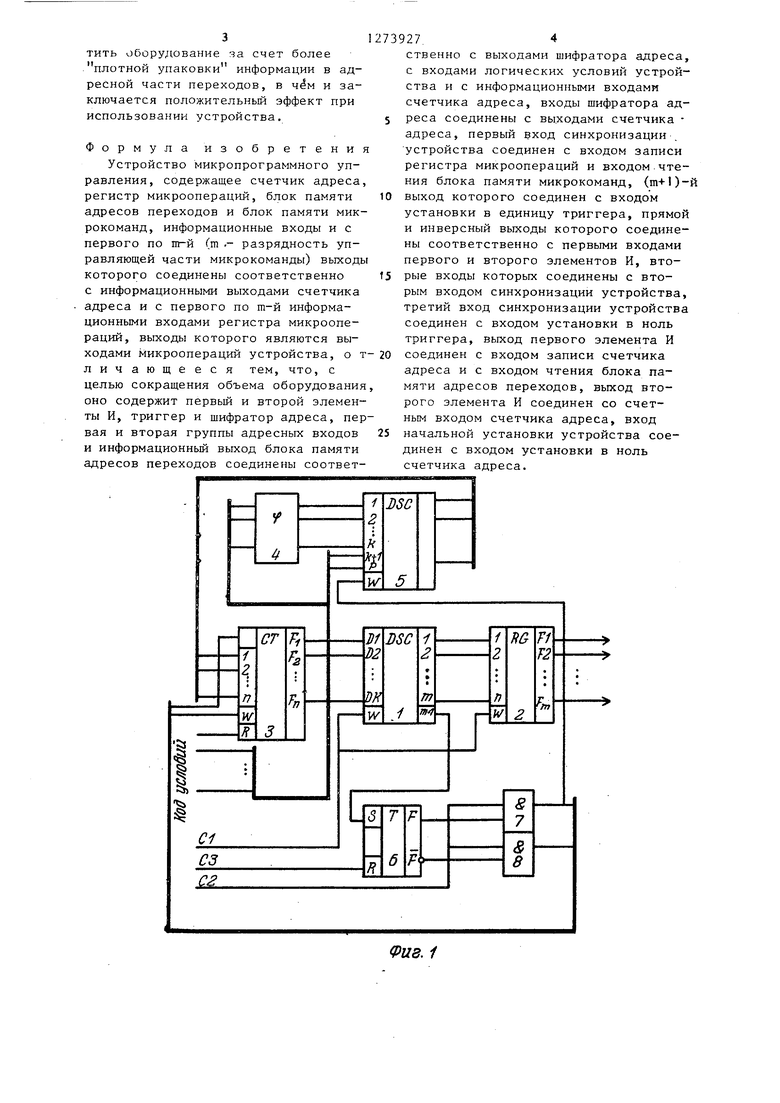

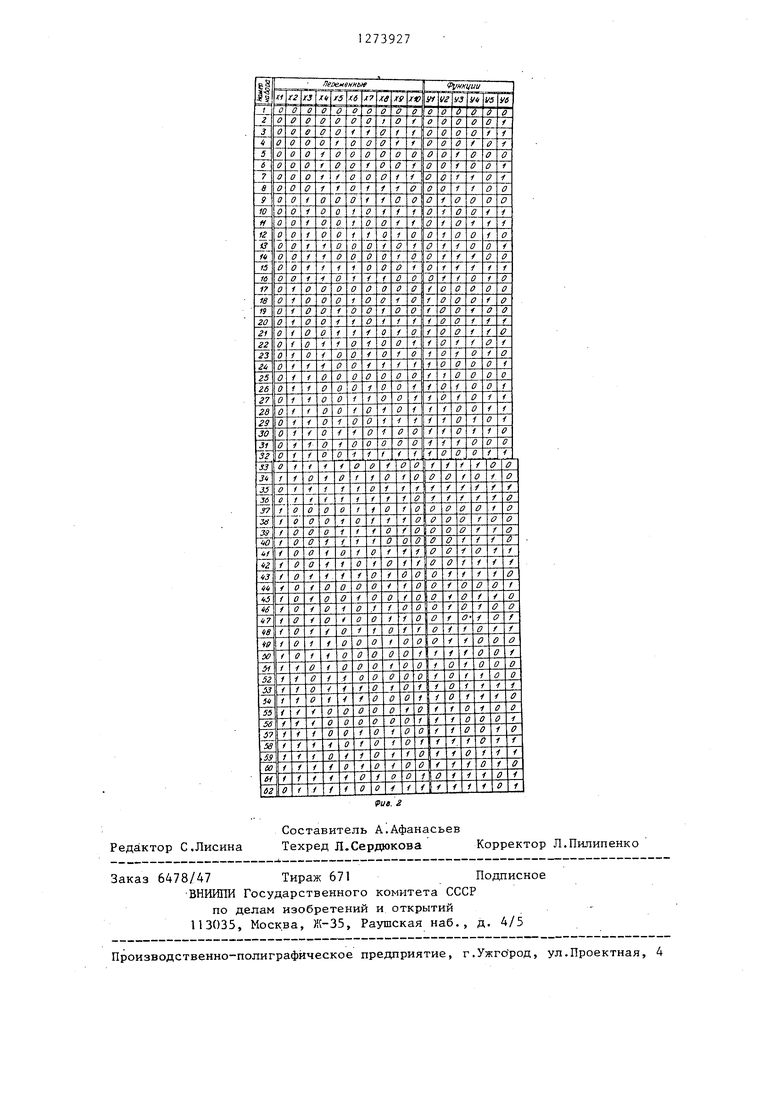

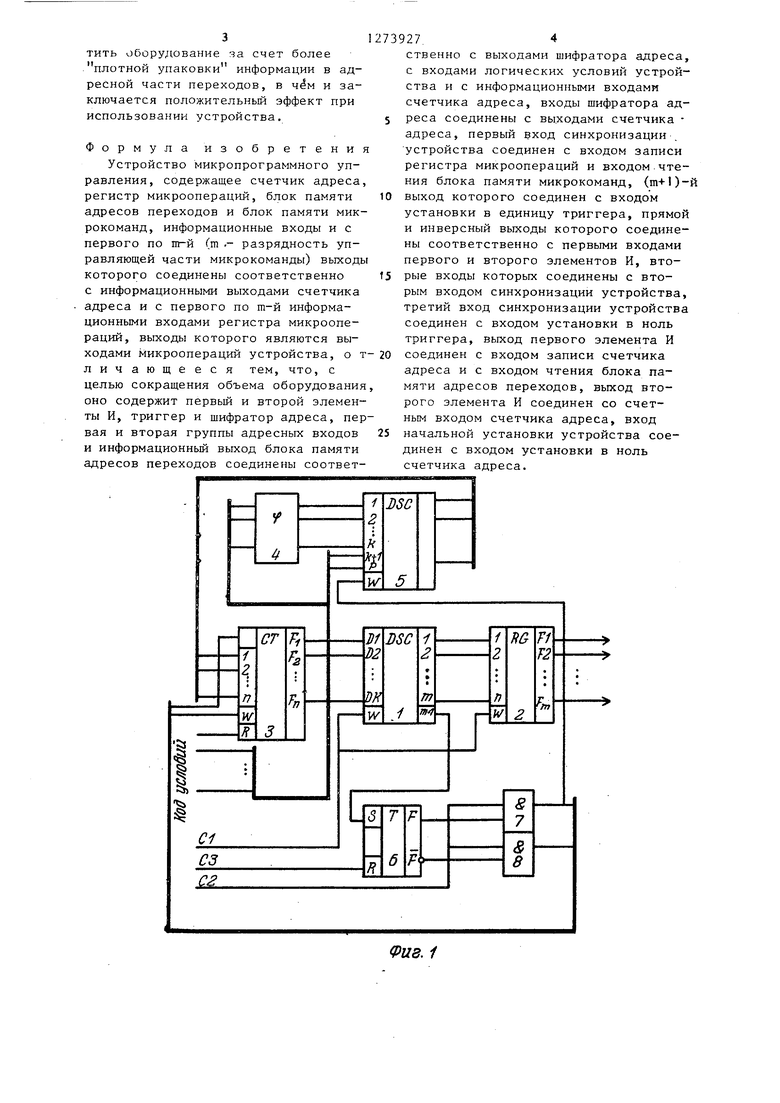

Изобретение относится к вычислительной технике и может быть исполь зовано дл5| микропрограммного управления устройств вычислительной техники. Цель изобретения - сокращение объема оборудования. На фиг.1 представлена функционал ная схема устройства; на фиг.2 - пр мер прошивки шифратора адреса. На фиг.1 приняты следующие обозн чения: блок 1 памяти микрокоманд; регистр 2 микроопераций; счетчик 3 адреса; шифратор 4 адреса; блок 5 памяти адресов переходов; триггер 6 и элементы И 7, 8. Сущность изобретения заключается в том, что адресные и управляющие разряды микрокоманд записаны со ответственно в блоке 5 памяти адресов переходов и в .блоке 1 памяти микрокоманд. Такое разделение разря ДОН микрокоманд позволяет исключить нулевые (пустые) значения адресов в памяти устройства, т.е. уменьшить оборудование, необходимое для постр ения памяти за счет более плотной упаковки информации. Значение адресных разрядов блока 5 памяти адре сов переходов находится в однозначном соответствии с кодом, установле ным на регистре 3 (текущим адресом) , т.е. Y; cf; (X), где Y; значение i-ro разряда на входе блока памяти адресов переходов 5; X множество наборов кодов, установлен ных на счетчике адреса. Шифратор адреса является функцио нальным преобразователем п-разрядного кода регистра 3 адреса в k-раз рядный код, которьм вместе с разрядами кода условий поступает на адресные входы блока памяти адресов переходов. При преобразовании должны быть учтены требования однозначности и оптимальности кодирования, последнее выражается формулой log Qpl где Qp - число адресов переходов; k - число выходов шифратора ад реса. Устройство работает следующим об разом. В исходном состоянии на счетчике 3 адреса установлен нулевой код на шинах условий - начальный код. Сигналом С 1 осуществляется возбуж7дение блока 1 памяти микрокоманд, сигналы с выхода которого устанавливают на регистре 2 код начальной микрокоманды. Сигналом с разряда (т+1) блока 1 памяти микрокоманд устанавливается триггер 6 в единичное состояние. Сигналом С 2 через элемент И 7 возбуждается блок 5 памяти адресов переходов, на выходе которого при начальном коде условий на входах (k-b 1)г блока памяти появляется нулевой код, т.е. код на счетчике адреса 3 не изменяется. Сигналом С 3 триггер 6 устанавливается в нулевое состояние, и работа устройства повторяется. Если код условий отличен от начального , сигналом с выхода элемента И 7 возбуждается блок 5 памяти адресов переходов, сигналами с выхода последнего на счетчике 3 адреса устанавливается код отличный от нулевого. При отсутствии сигналов на выходе (m-t-1) разряда блока 1- памяти триггер 6 сохраняет нулевое состояние и тогда сигналом С 2 через элемент И 8 возбуждается счетный вход счетчика 3, который увеличивает свое состояние на единицу. Таким образом, осуществляется установка кода в счетчике 3 адреса- сигналами с выходов блока 5 памяти адресов переходов - при наличии сигнала на выходе (m-t-1) разряда блока 1 памяти микрокоманд, или увеличение кода на +1 счетчика адреса 3 - в противном случае. Пример прошивки шифратора адреса для микропрограммного устройства, адресная часть которого равна 10 разрядам, число адресов переходов равно 62, представлен на фиг.2. При минимизации адресных кодов перехода были использованы известные методы минимизации переключательных функций. Аналитическая зависимость выходных функций шифратора адреса от входных переменных (кодов адреса регистра 3) имеет следующие выражения 6 10 , ; Конструктивные особенности предлагаемого устройства позволяют сократить vj6opy;iOBaHHe за счет более плотной упаковки информации в адресной части переходов, в и заключается положительньш эффект при использовании устройства. Формула изобретени Устройство микропрограммного управления, содержащее счетчик адреса регистр микроопераций, блок памяти адресов переходов и блок памяти мик рокоманд, информационные входы и с первого по т-й (т .- разрядность управляющей части микрокоманды) выходы которого соединены соответственно с информационными выходами счетчика адреса и с первого по т-й информационными входами регистра микроопераций, выходы которого являются выходами Микроопераций устройства, о т личающееся тем, что, с целью сокращения объема оборудования оно содержит первый и второй элементы И, триггер и щифратор адреса, пер вая и вторая группы адресных входов и информационный выход блока памяти адресов переходов соединены соответ27.4 ственно с выходами шифратора адреса, с входами логических условий устройства и с информационными входами счетчика адреса, входы щифратора адреса соединены с выходами счетчика адреса, первый вход синхронизации . устройства соединен с входом записи регистра микроопераций и входом.чтения блока памяти микрокоманд, (т+1)-й выход которого соединен с входом установки в единицу триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с вторым входом синхронизации устройства, третий вход синхронизации устройства соединен с входом установки в ноль триггера, выход первого элемента И соединен с входом записи счетчика адреса и с входом чтения блока памяти адресов переходов, выход второго элемента И соединен со счетным входом счетчика адреса, вход начальной установки устройства соединен с входом установки в ноль счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Микропрограммное устройство управления | 1980 |

|

SU920726A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

Устройство относится к области вычислительной техники и может быть использовано для реализации микропрограммного управления устройствами вычислительной техники. Целью предлагаемого изобретения является уменьшения оборудования за счет со- кращения избыточности в адресной части памяти микропрограмм. Устройство содержит блок памяти микрокоманд блок памяти адресов переходов, счетчик адреса, регистр микроопераций, шифратор адреса, триггер, два элемента И, Введение шифратора адреса, триггера и двух элементов И приводит ifi к достижению цели. 3 ил.

Фиа. 1

| Микропрограммное устройство управления | 1975 |

|

SU561964A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Хассон | |||

| Микропрограмное управление | |||

| М.: Мир, 1974 | |||

| Глушков В.М | |||

| Синтез цифровых автоматов | |||

| И.: Фиэматгиз, 1962. | |||

Авторы

Даты

1986-11-30—Публикация

1985-06-18—Подача