00

g

миро вате л ей соединены с выходами преобразователей б, 7 кодов и дешифратора 8 и входом задания К. Выходы блока 15связаны с управляющими входами силовых элементов, например транзисторов инвертора 16. На выходных шинах инвертора 16 при любом изменении входной частоты формируются регулируемые от внешнего цифрового сигнала напряжения по трапецеидальному закону широтно-импульсного модулирования. В каждой полуволне выходного напряжения содержатся импульсы одной полярности при полнойсимметрии этого напряжения. 4 табл., 4 ил.

Изобретение относится к электротехнике, в частности к преобразовательной технике, и предназначено преимущественно для управления инверторами в системах электропитания и электропривода для преобразования постоянного напряжения в многофазное переменное напряжение с широтио-импульеной модуляцией по закону, близкому к синусоидальному. Цепь изобретения - расширение функциональных возможностей за счет формирования сигнала, близкого к синусоидальному. Устройство для управления инвертором с широтно-им- пульсной модуляцией содержит многоразрядный делитель 1, подсоединенный последовательно к многофазному счетчику 5. Выходы разрядов 2, 3,4 делителя 1 соединены с входами преобразователей 6, 7 кодов и дешифратора 8. 8 устройстве -два формирователя импульсов. Первый формирователь линейно нарастающих импульсов состоит из двух логических преобразователей 9 и 10. Их выходу соединены с входами логического элемента ИЛИ 11. Второй формирователь линейно спадающих импульсов состоит из двух логических преобразователей 12 и 13, выходы которых соединены с входами элемента ИЛИ 14, Выходы элементов ИЛИ 11 и 14 соединены соответственно с входом логического блока 15, соединенного также с выходом счетчика 5. Входы фор

Изобретение относится к электротехнике, в частности к преобразовательной технике, и предназначено преимущественно для управления инверторами в системах электропитания и электропривода для преобразования постоянного напряжения в многофазное переменное напряжение с ширртногймпульсной модуляцией по закону, близкому к синусоидальному.,

Цель изобретения - расширение функциональных возможностей за счет формирования сигнала, близкого к синусоидальному.

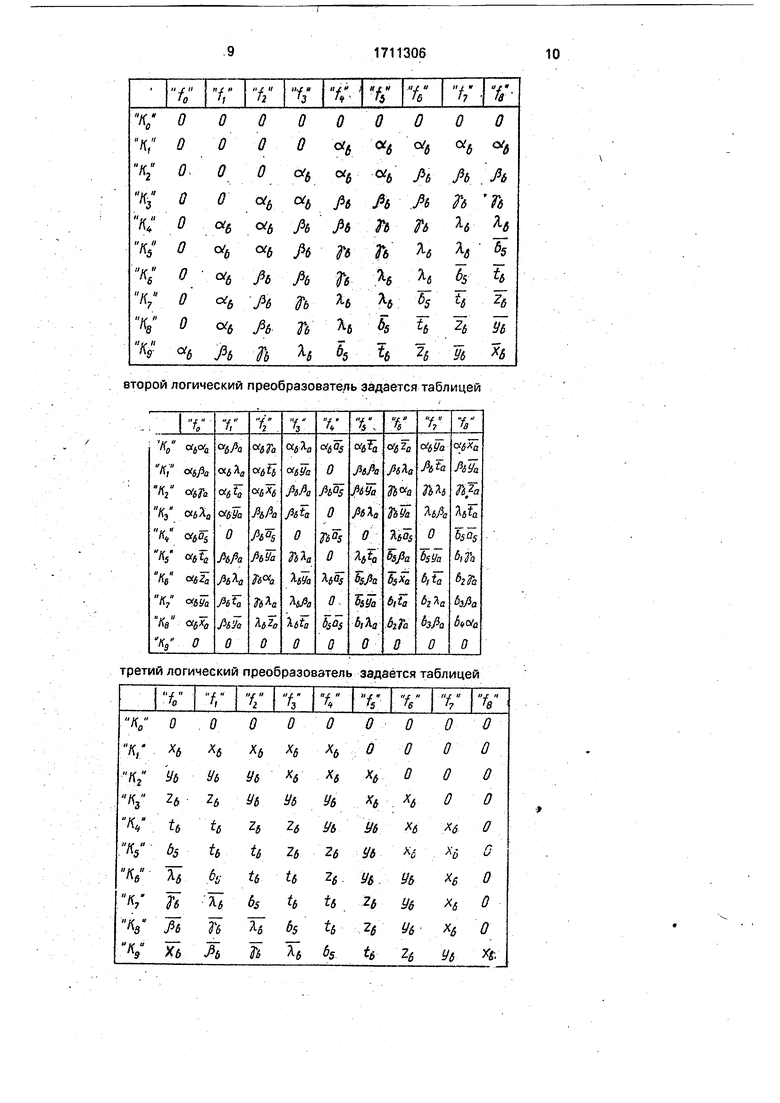

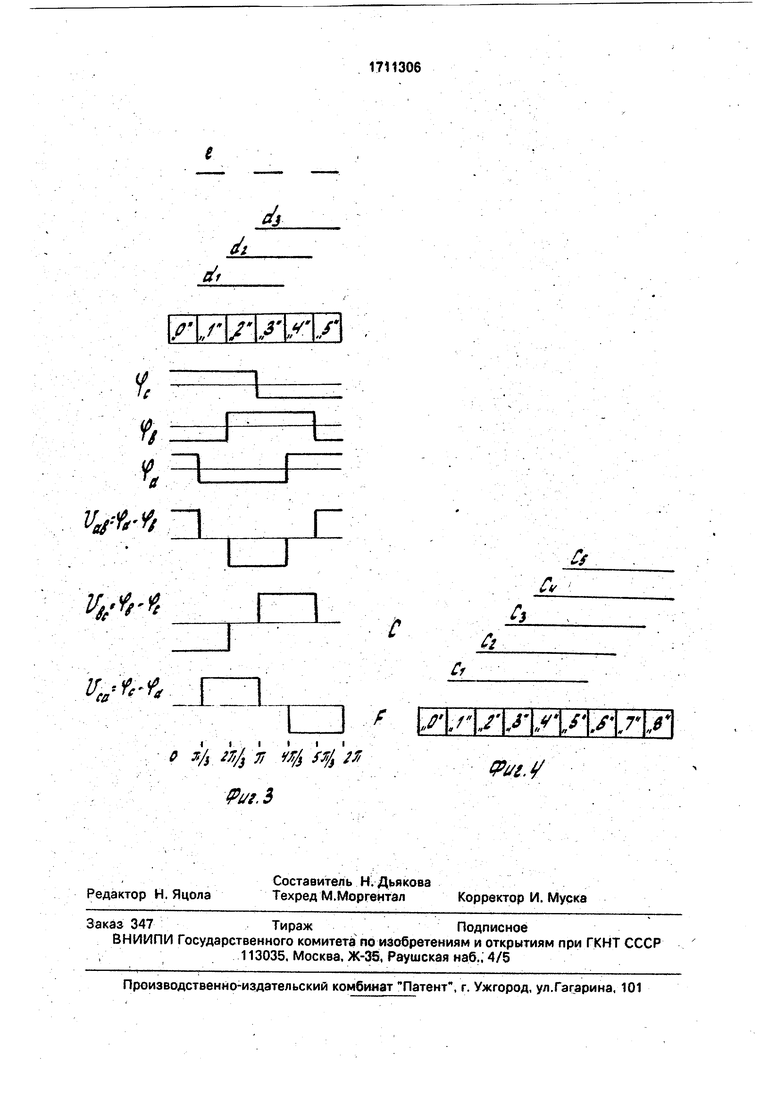

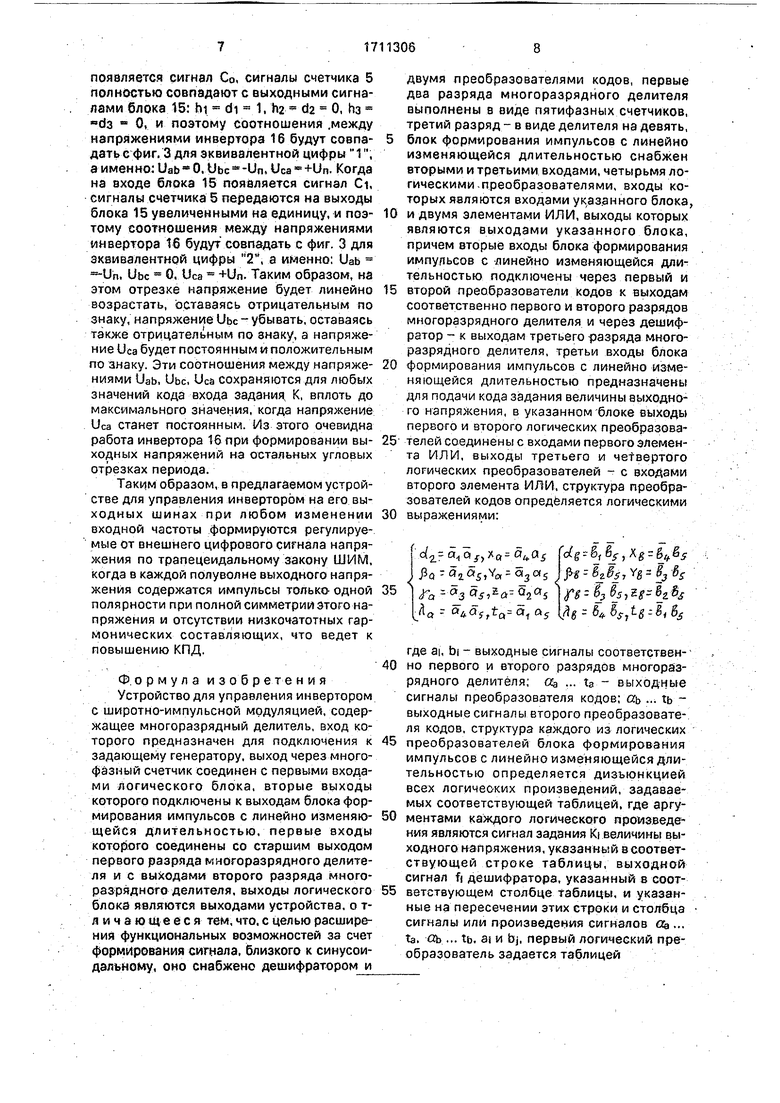

На фиг. 1 приведена структурная схема устройства для управления инвертором; на фиг. 2 - диаграммы пятифазных сигналов первого разряда A (ai-as) многоразрядного делителя, эквивалентных им цифр обычного цифрового кода О - 9 и сигналов Of, fity. А, х, у, z, t на выходах преобразователя кодов, подключенного к выходным шинам этого разряда; на фиг. 3 - сигналы D (dt-da) на выходах многофазного счетчика, дополнительного сигнала е и потенциалов ра,рь,рс средних точек стоек мостового инвертора, а также его выходных

напряжений УаЬ - фа - ft, Ubc ( Јfc.

Uea РЬ - ра если бы управление силовыми ключами осуществлялось непосредственно трехфазными сигналами делителя D (di-da); на фиг. 4 - пятифазные сигналы С (ci-сз) третьего разряда многоразрядного делителя, выходные сигналы F (О - 8) дешифратора.

Функциональная схема устройства следующая.

Вход внешней частоты ft соединен с входом многаразрядног&деяителя t, который состоит из трех последовательно соединенных разрядов . Последовательно с делителем 1 соединен многофазный счетчик 5. Выходы разрядов 2-4 делителя 1 соединены с входами преобразователей 6 и 7 кодов и дешифратора 8. В устройстве имеется первый формирователь линейно нарастающих импульсов, который состоит из двух логических преобразователей 9 и 10, выходы которых соединены с

входами логического элемента ИЛИ 11, и второй формирователь линейно спадающих импульсов, который состоит из двух логических преобразователей 12 и 13, выходы которых соединены с входами элемента ИЛИ 14. Выходы элементов ИЛИ 11 и 14 соединены соответственное входами логического блока 15, второй вход которого соединен с выходами счётчика 5.

Входы формирователей линейно нарастающих и линейно спадающих импульсов соединены с выходами преобразователей 6 и 7 кодов и дешифратора 8 и входом задания К. Выходы блока 15 связаны с управк

ляющими входами силовых элементов, например, транзисторов инвертора 16. Выполнение первого и второго разрядов 2 и 3 делителя 1 осуществляется в пятифаз- ном коде. Третий разряд 4 делителя 1 также

выполняется по этим же принципам в многофазном коде; в пятифазном коде с основанием счисления Р 9.

. Преобразователи 6,7 кодов выполняются одинаковыми в соответствии со еледующими логическими зависимостями (на примере преобразователя 6):

a О - alas; x 9 a4as; /3 О V... V 1 3235; у ... aaas; у- О V ...V 2 aba s; г ... aias: А- О V ...V 3. 4a5;t .., iias;

где ai - выходные сигналы разрядов делителя t.

Блок 15 для трехфазного инвертора 16 выполняется по следующим логическим зависимостям; h CoVeJj C,VC0Cie ,

I- ,

где Ci, Co - соответственно сигналы на выходах.

Преобразователи узлов формирования линейно изменяющихся импульсов имеют для каждого варианта выполнения устройства различное исполнение.

Построение преобразователя 9 полностью определяется таблицей (таблица для первого логического преобразователя в формуле изобретения), где на пересечении значений входа задания. К строк и цифр F столбцов записаны логические зависимости, определяющие первое слагаемое сумм. Построение преобразователя 10 полностью определяется таблицей, заданной для второго логического преобразователя в форму- ле изобретения.

Построение преобразователей 12 и 13 полностью совпадает с рассмотренными, а сигналы на входных шинах этих блоков определяются таблицами для третьего и чет- вертого логических преобразователей в формуле изобретения.,

Устройство для управления инвертором работает следующим образом.

Делитель 1 непрерывно подсчитывает поступающие импульсы входной частоты fi. G приходом каждого импульса его цифровое значение увеличивается на единицу. При полном заполнении делителя 1 и возвращении в исходное состояние на его вы- ходе каждый раз формируется импульс частоты f2, который изменяет состояние счетчика 5. Последний проходит последовательно шесть устойчивых состояний, характеризующихся различными значениями выходных трехфазных сигналов D (drda), эквивалентных цифрам обычного кода О - 5. При четных цифрах в блоке 15 формируется сигнал ёГ а при нечетных е. Если при этом на выходы задания К не подано какого-либо цифрового сигнала, то на выходе элементов ИЛИ 11 и 14 и соответственно на входных шинах (Ci, С0) блока 15 также будет нулевой сигнал. При чётных состояниях счетчика 5 (е 1) на выходных шинах блока 15 будут выдаваться сигналы hi 0, П2 1,пз 0. При этом средние точки стоекмостового инвертора 16 будут иметь положительный потенциал источника тания, а выходные напряжения инвертора 16 значения нуля (Uab 0, Ubc 0, ). При нечетных состояниях счетчика 5 (е 1) выходные сигналы блока 15 будут обратными hi 1, ha 0, пз 1 и, следовательно, средние точки стоек инвертора 16 будут со единены с отрицательным потенциалом напряжения источника питания Un. что также соответствует нулевым значениям выходного напряжения инвертора 16.

В дальнейшем всякий раз, когда будут отсутствовать сигналы на выходах элементов ИЛИ 11 и .14, выходные напряжения инвертора 16 будут равны нулю.

При подаче на вход задания К устройства цифрового сигнала, например К0, которое соответствует минимальному значению выходных напряжений инвертора 16, на выходе элемента ИЛИ 11 будет формироваться за цикл переключения делителя 1 серия линейно нарастающих импульсов. Эти импульсы будут располагаться в начале (конце) цикла переключения первых двух разрядов 2 и 3 делителя 1. С увеличением цифрового значения входа задания К будет пропорционально увеличиваться длительность этих импульсов. Аналогичным образом происходит формирование линейно спадающих импульсов на выходе элемента ИЛИ 14. При любых промежуточных значениях кода входа задания К между импульсом из линейно нарастающей серии и импульсом из линейно спадающей серии имеется пауза, в момент которой сигналы на выходах элементов ИЛИ 11 и 14 равны нулю. При максимальном значении кода на входе задания К эта пауза между указанными импульсами отсутствует.

При соотношении сигналов счетчика 5 di 0, d2 0, da 0, что соответствует эквивалентной цифре О (фиг. 3), на выходных шинах инвертора 16 формируются напряжения на угловом отрезке от 0 до яг/3. При этом, когда на входе блока 15 появляется сигнал Со. сигналы счетчика 5 полностью совпадают с выходными сигналами блока 15:vhi dt 0, ha d2 О, пз da 0, и поэтому соотношения между напряжениями инвертора 16 будут полностью совпадать с фиг. 3 для эквивалентной цифры О,, а именно: Uab +Un. Ubc -Un, Uca 0. Когда на выходе блока 15 появляется сигнал Ci, сигналы счетчика 5 передаются на выходы блока 15 увеличенными на единицу и поэтому соотношения между напряжениями инвертора 16 будут полностью совпадать с фиг. 3 для эквивалентной цифры 1, а именно: Оаь 0, Ubc Un, Uca + Un. Таким образом, на этом отрезке напряжение Uab будет линейно убывать, оставаясь положительным по знаку, напряжение Ubc будет постоянным и отрицательным по знаку, а напряжение Uca будет возрастать, оставаясь положительным по знаку. Эти соотношения между напряжениями Uab, Ubc, Uca сохраняются для любых значений входного сигнала, вплоть до максимального значения, когда напряжение Ubc станет постоянным.

При соотношении сигналов счетчика 5 di - 1, d2 0, da 1, что соответствует эквивалентной цифре .1 (фиг, 3), на выходных шинах инвертора 16 формируются напряжения на угяоврм отрезке от я/3 до 2яг/3. При этом, когда на входе блока 15

появляется сигнал Со, сигналы счетчика 5 полностью совпадают с выходными сигналами блока 15: hi di 1, h2« d2 0, пз «da О, и поэтому соотношения .между напряжениями инвертора 16 будут совпадать с фиг. 3 для эквивалентной цифры 1, aMMeHHo:Uab 0,. . Когда на входе блока 15 появляется сигнал Ci, сигналы счетчика 5 передаются на выходы блока 15 увеличенными на единицу, и поэтому соотношений между напряжениями инвертора 16 будут совпадать с фиг. 3 для эквивалентной цифры 2, а именно: Uab - -Un, Ubc 0, Uca +Un. Таким образом, на этом отрезке напряжение будет линейно возрастать, оставаясь отрицательным по знаку, напряжение Ubc - убывать, оставаясь также отрицательным по знаку, а напряжение Uca будет постоянным и положительным по знаку. Эти соотношения между напряжениями Uab, Ubc, Uca сохраняются для любых значений кода входа задания К, вплоть до максимального значения, когда напряжение Uca станет постоянным. Из этого очевидна работа инвертора 16 при формировании выходных напряжений на остальных угловых отрезках периода.

Таким образом, в предлагаемом устройстве для управления инвертором на его выходных шинах при любом изменении входной частоты формируются регулируемые от внешнего цифрового сигнала напряжения по трапецеидальному закону ШИМ, когда в каждой полуволне выходного напряжения содержатся импульсы только одной полярности при полной симметрии этого напряжения и отсутствии низкочатотных гармонических составляющих, что ведет к повышению КПД.

Ф.ормула изобретения Устройство для управления инвертором с широтно-импульсной модуляцией, содержащее многоразрядный делитель, вход которого предназначен для подключения к задающему генератору, выход через многофазный счетчик соединен с первыми входами логического блока, вторые выходы которого подключены к выходам блока формирования импульсов с линейно изменяющейся длительностью, первые входы которого соединены со старшим выходом первого разряда многоразрядного делителя и с выходами второго разряда многоразрядного делителя, выходы логического блока являются выходами устройства, о т- л и ч а ю щ е е с я тем, что. с целью расширения функциональных возможностей за счет формирования сигнала, близкого к синусоидальному, оно снабжено дешифратором и

двумя преобразователями кодов, первые два разряда многоразрядного делителя выполнены в виде пятифазных счетчиков, третий разряд- в виде делителя на девять,

блок формирования импульсов с линейно изменяющейся длительностью снабжен вторыми и третьими входами, четырьмя логическими.преобразователями, входы которых являются входами указанного блока,

и двумя элементами ИЛИ, выходы которых являются выходами указанного блока, причем вторые входы блока формирования импульсов с линейно изменяющейся длительностью подключены через первый и

второй преобразователи кодов к выходам соответственно первого и второго разрядов многоразрядного делителя и через дешифратор - к выходам третьего разряда многоразрядного делителя, третьи входы блока

формирования импульсов с линейно изменяющейся длительностью предназначены для подачи кода задания величины выходного напряжения, в указанном блоке выходы первого и второго логических лреобразователей соединены с входами первого элемента ИЛИ, выходы третьего и четвертого логических преобразователей - с входами второго элемента ИЛИ, структура преобразователей кодов определяется логическими

выражениями:

i. QI+QS

, U - «4%,, Q5

,X M

,Yg 5

fg-fb$5-,.$S Й #5-7

где а, bi - выходные сигналы соответственно первого и второго разрядов многоразрядного делителя; Оа ... ta - выходные сигналы преобразователя кодов; «ь tb - выходные сигналы второго преобразователя кодов, структура каждого из логических

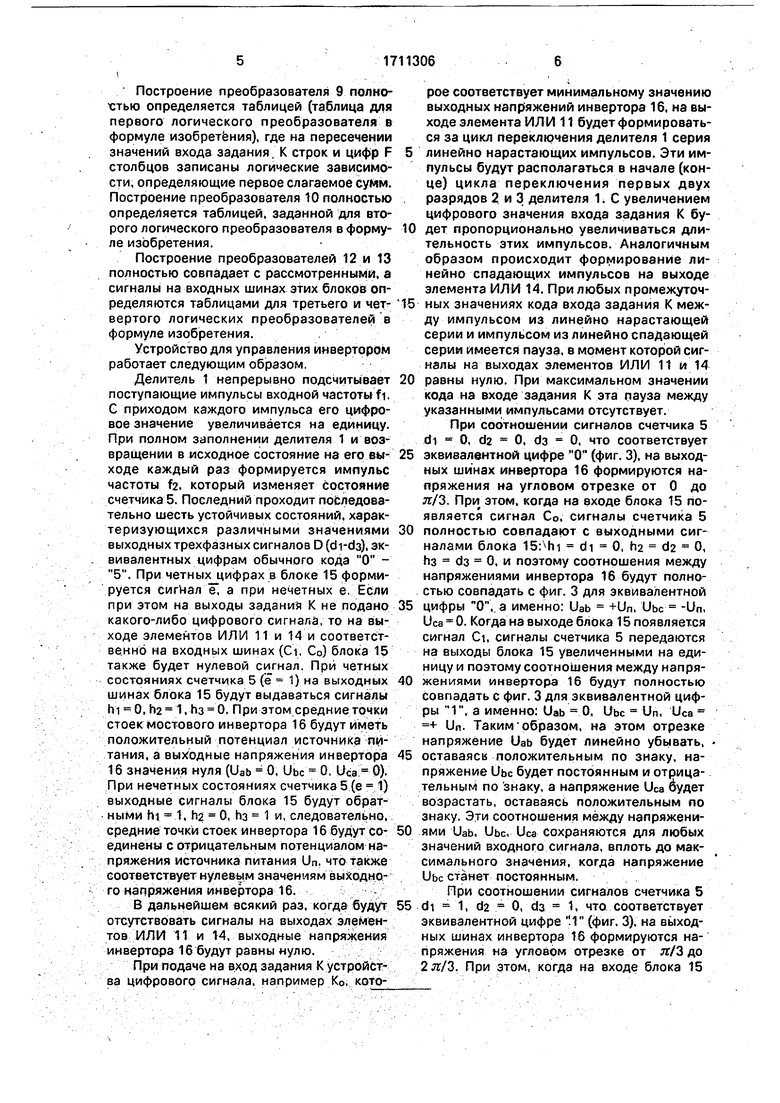

преобразователей блока формирования импульсов с линейно изменяющейся длительностью определяется дизъюнкцией всех логических произведений, задаваемых соответствующей таблицей, где аргументами каждого логического произведения являются сигнал задания Ki величины выходного напряжения, указанный в соответствующей строке таблицы, выходной сигнал fi дешифратора, указанный в соответствующем столбце таблицы, и указанные на пересечении этих строки и столбца сигналы или произведения сигналов Оа ... ta. «ь ... tb, as и bj. первый логический преобразователь задается таблицей

второй логический преобразователь задается таблицей

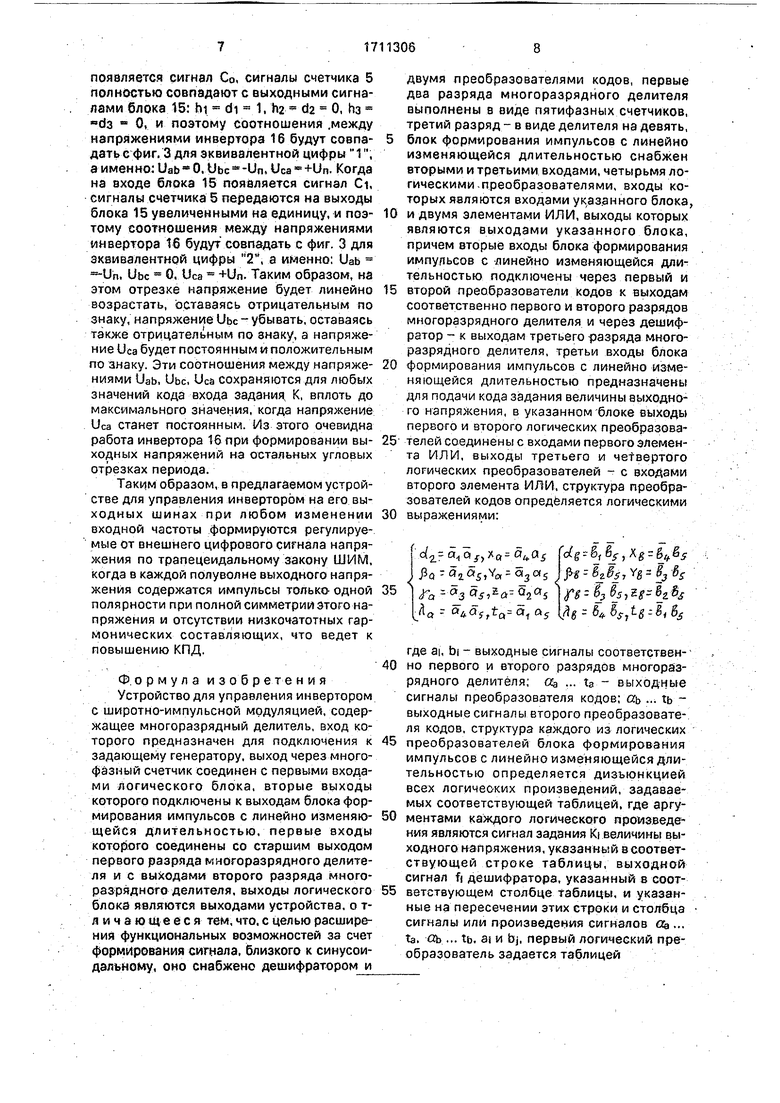

третий логический преобразователь задаётся таблицей

четвертый логический преобразователь задаётся таблицей

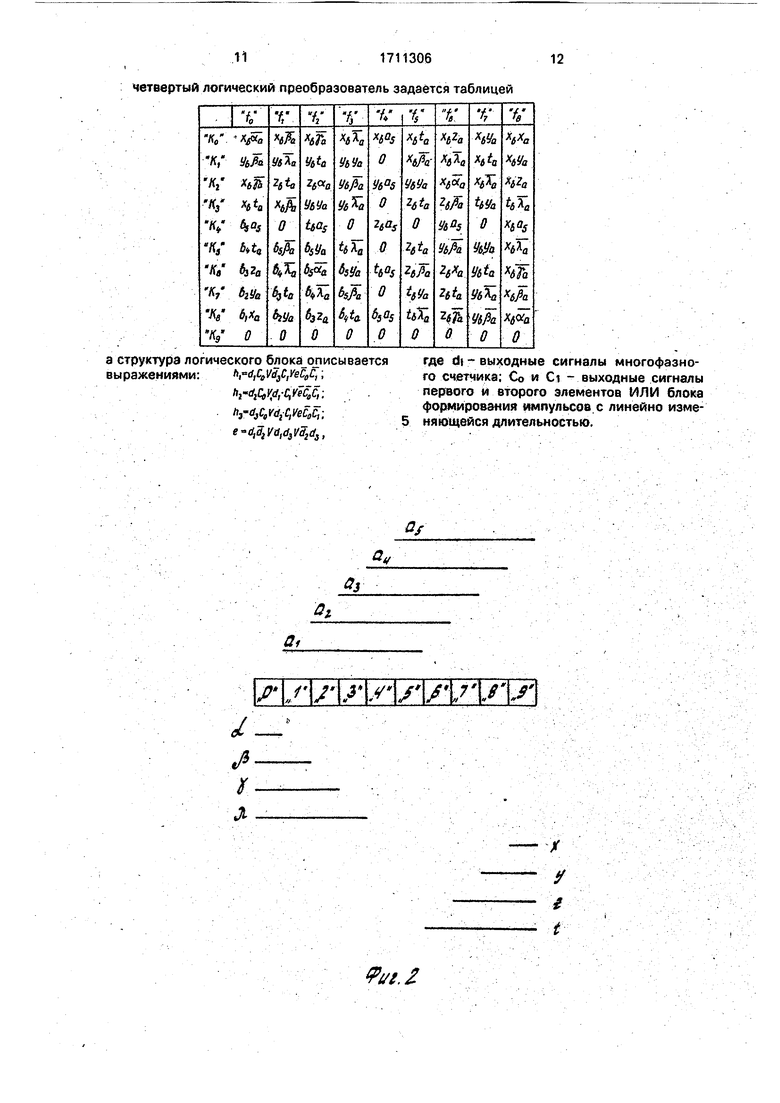

а структура логического блока о исывается выражениями: ,;

ftrWrWЈ: :

,;

,d3v32d3

/

Ј /

Д

где di - выходные сигналы многофазного счетчика; Со и Ci - выходные сигналы первого и второго элементов ИЛИ блока формирования импульсов с линейно изме- няющвйся длительностью.

/

У /

t

Рм./

i

ъ - -,t

t

1Г

I I

Vf/frt

ицМ

L

4I

I I

0 x/i. Wfcii Щ /$ /J

. Рм.З

ft

fr

Ci

fyt.#

| Устройство для управления многофазным инвертором | 1978 |

|

SU955837A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-02-07—Публикация

1984-04-25—Подача