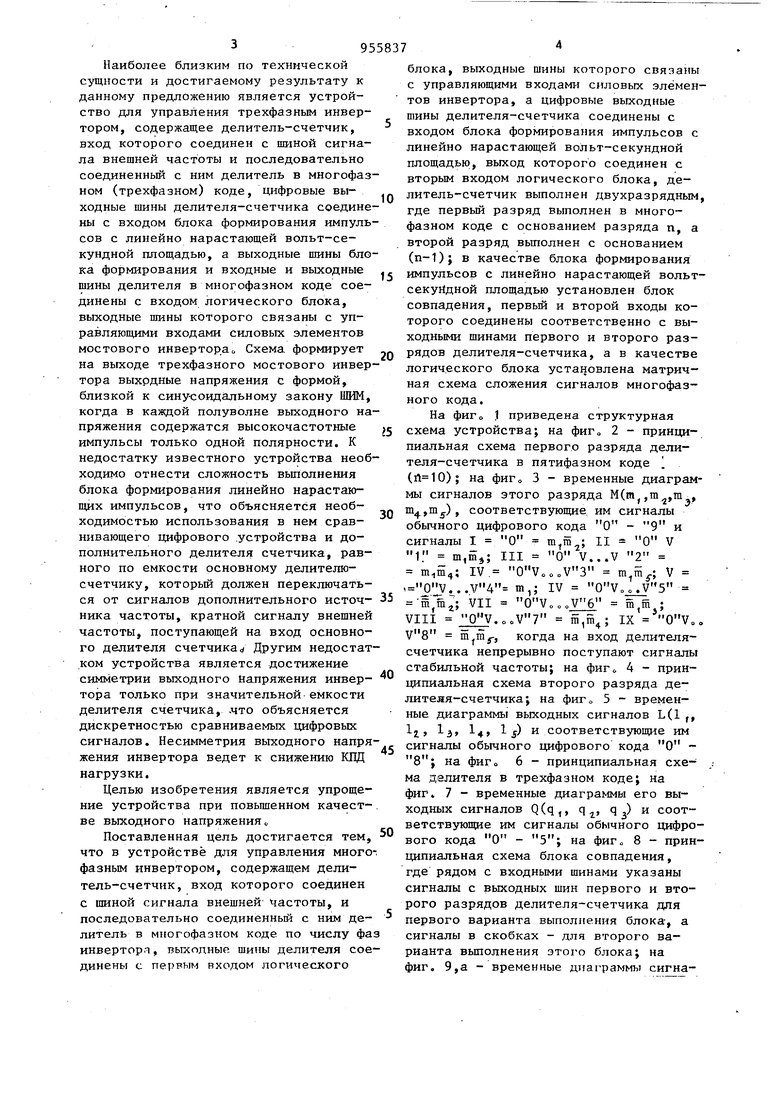

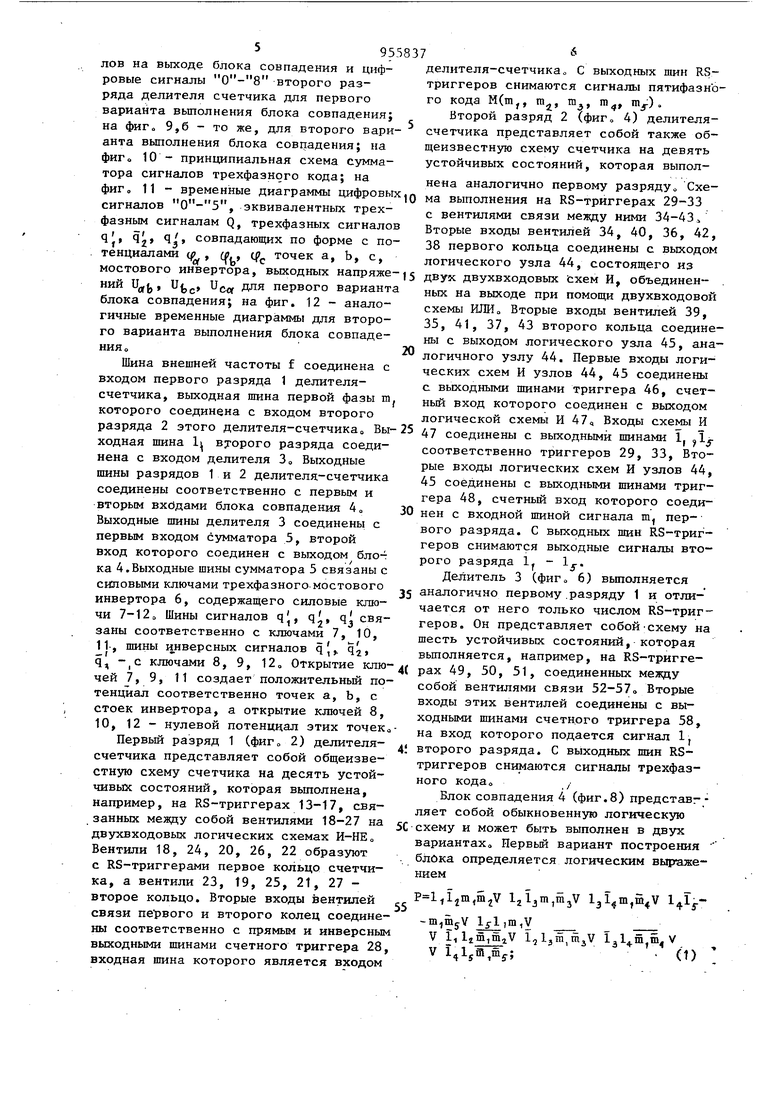

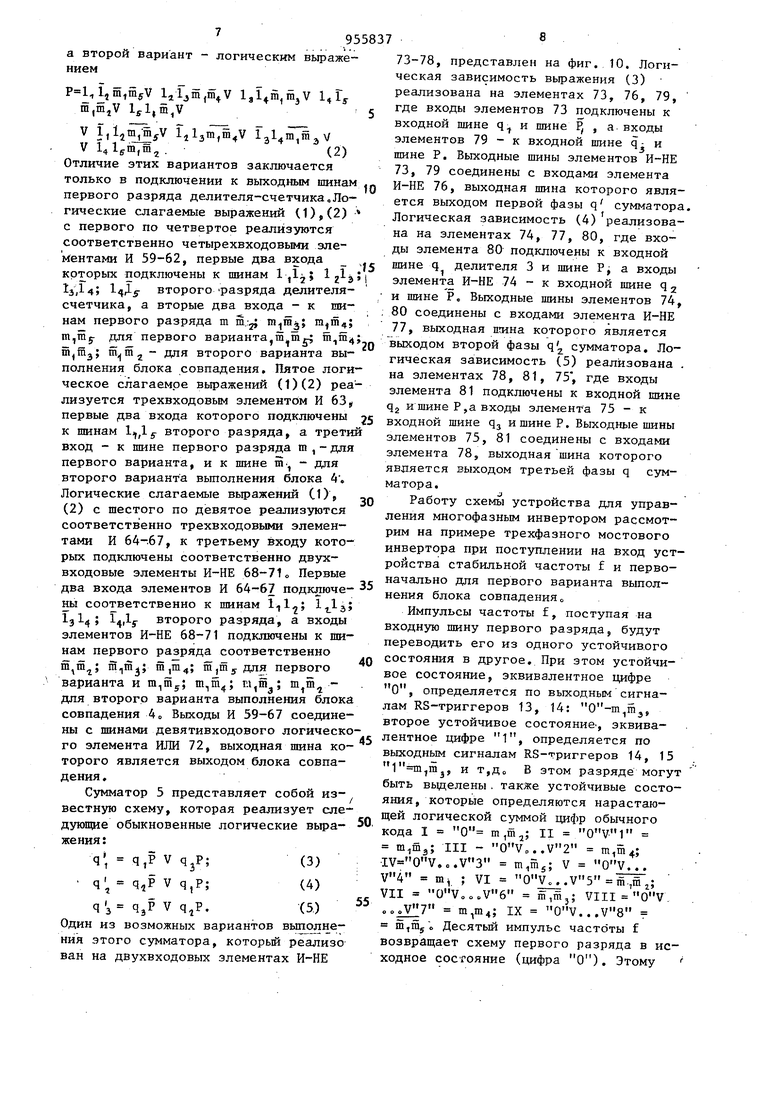

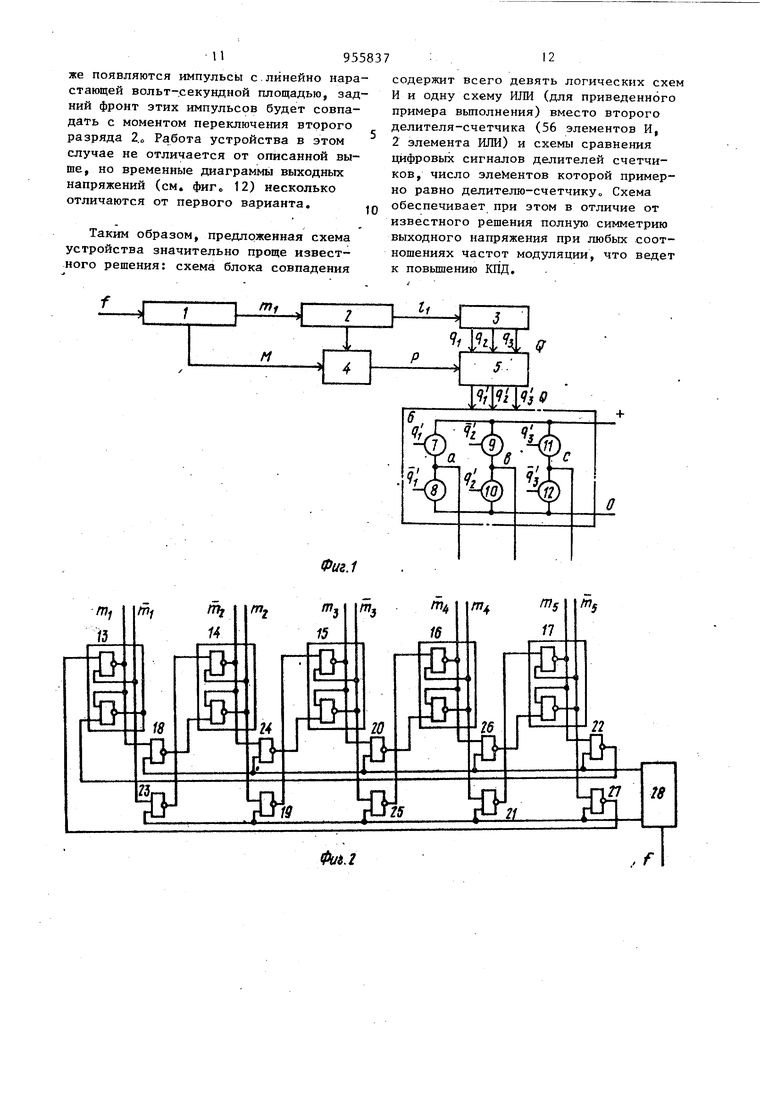

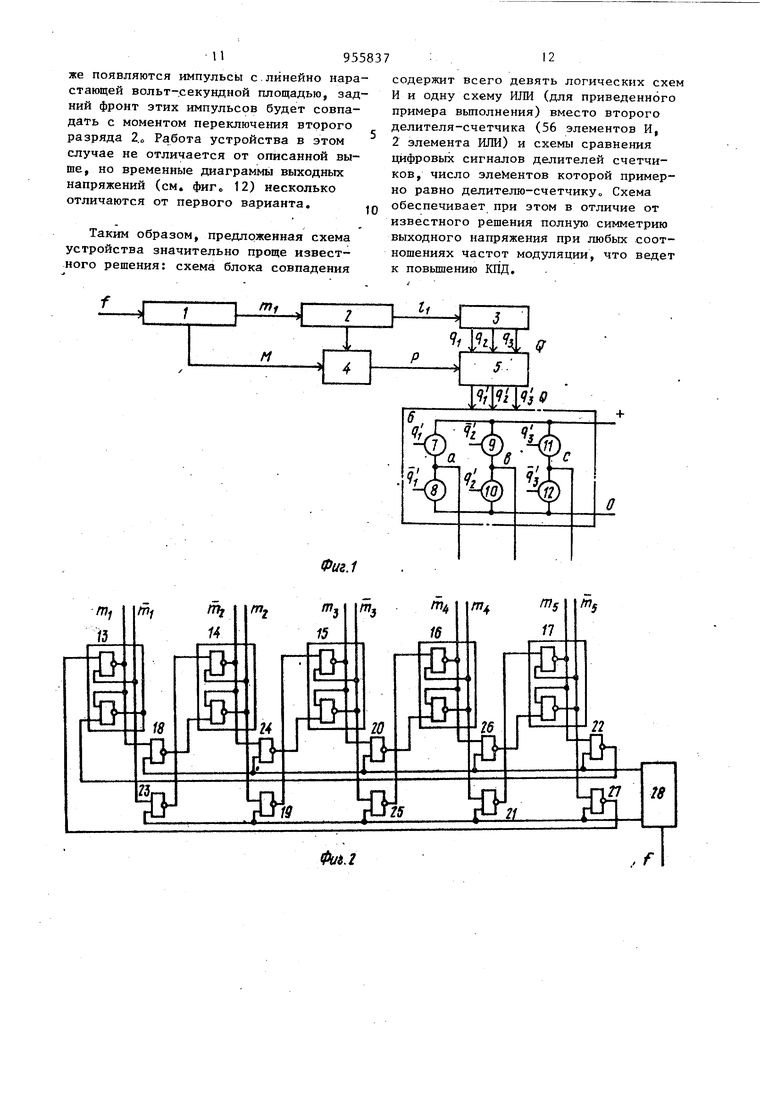

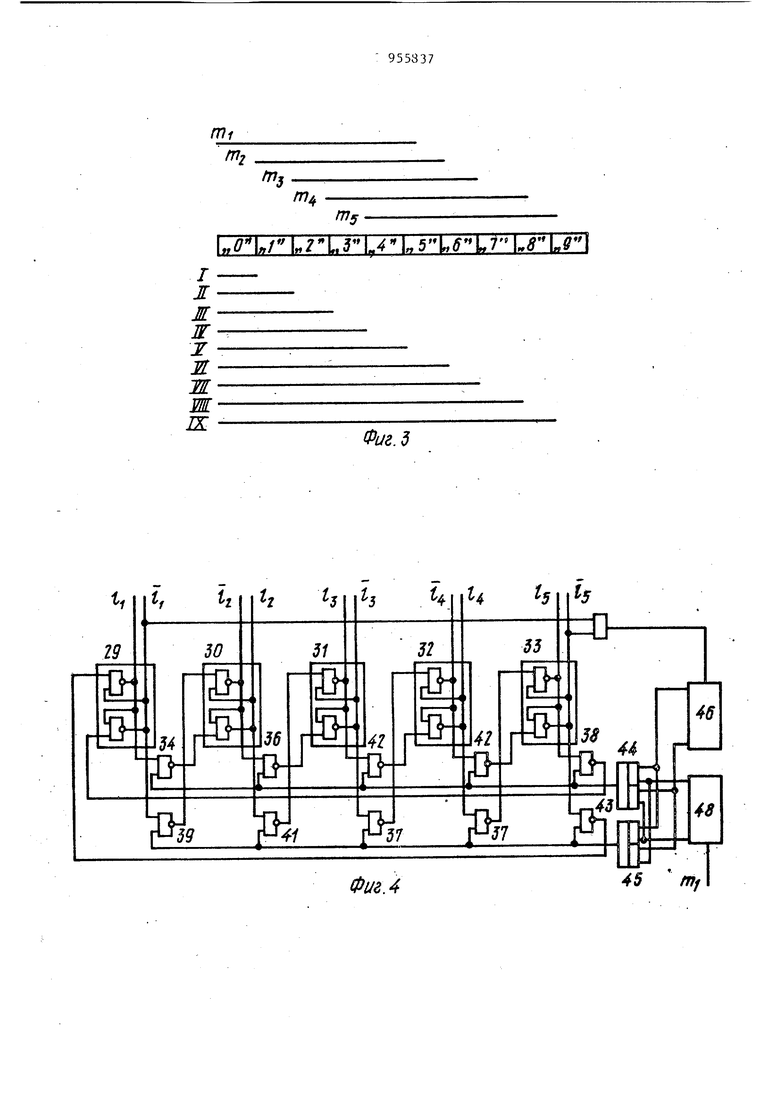

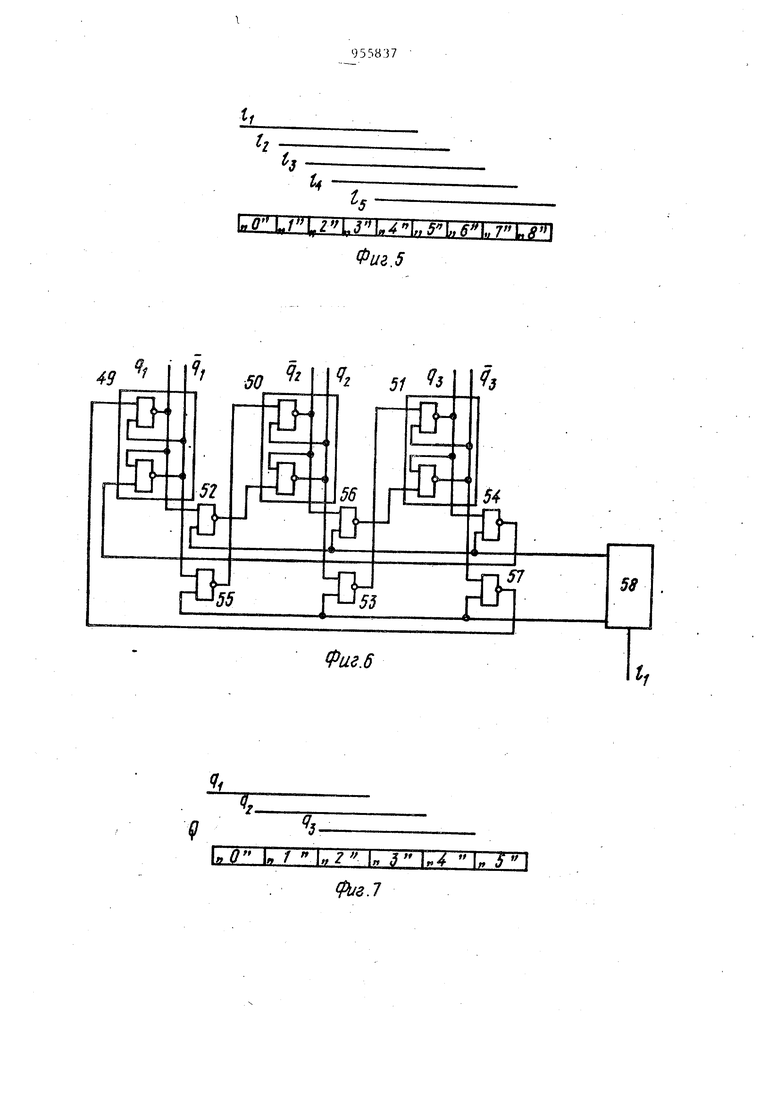

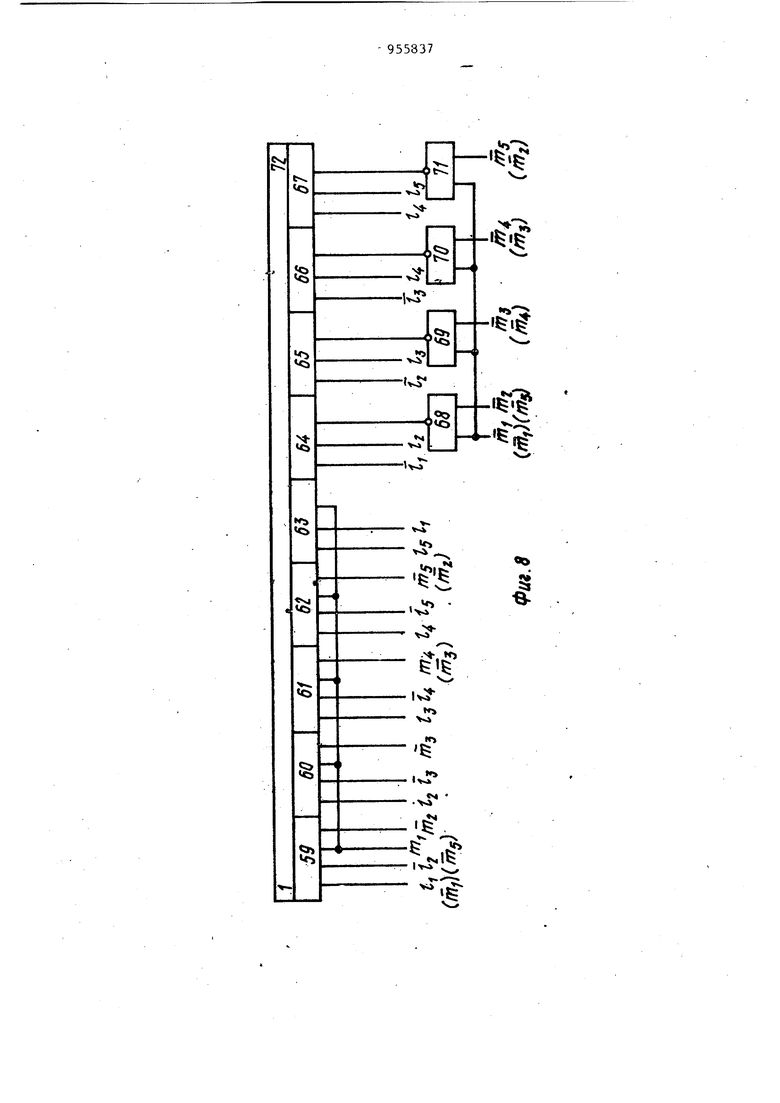

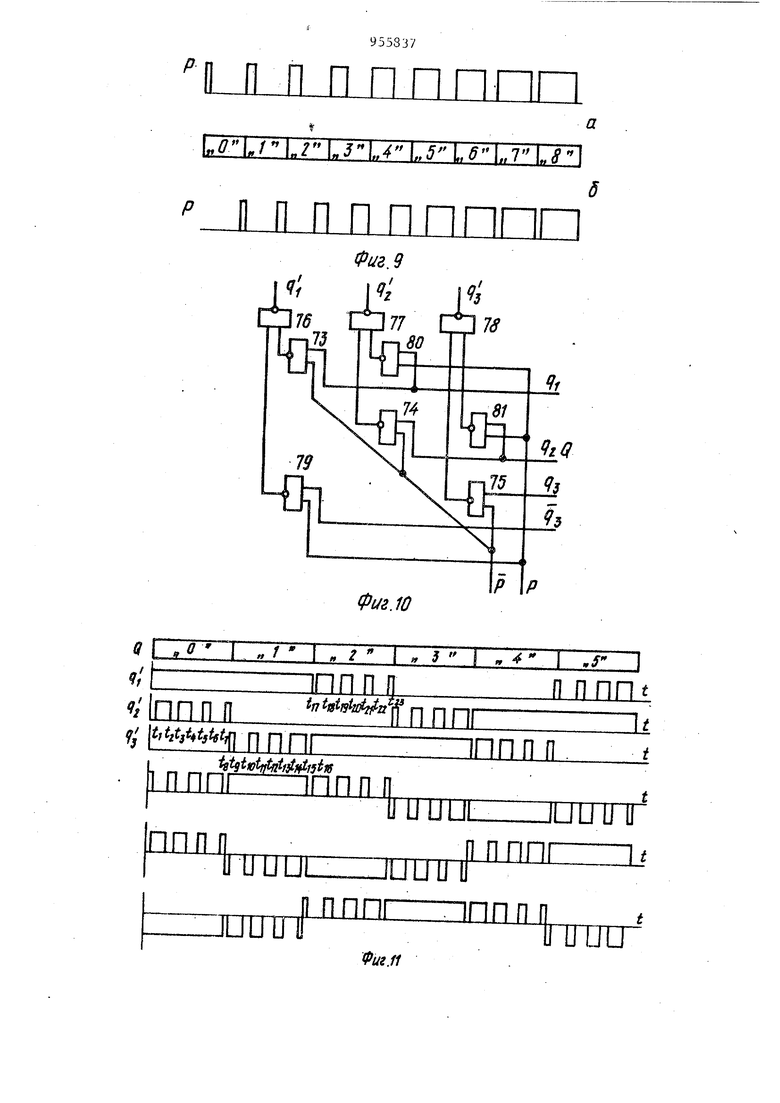

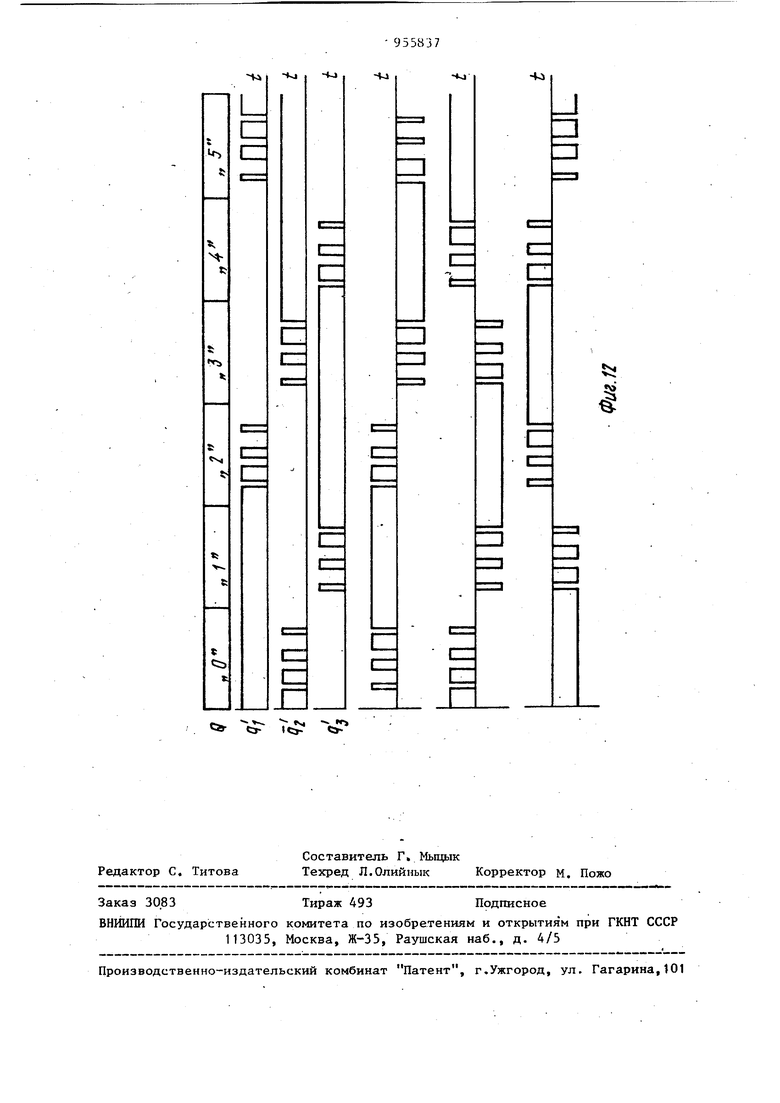

395 Наиболее близким по технической сущности и достигаемому результату к данному предложению является устройство для управления трехфазным инвертором, содержащее делитель-счетчик, вход которого соединен с шиной сигнала внешней частоты и последовательно соединенный с ним делитель в многофаз ном (трехфазном) коде, цифровые выходные шины делителя-счетчика соедине ны с входом блока формирования импуль сов с линейно нарастающей вольт-секундной площадью, а выходные шины бло ка формирования и входные и выходные шины делителя в многофазном коде соединены с входом логического блока, выходные шины которого связаны с управляющими входами силовых элементов мостового инверторао Схема формирует на выходе трехфазного мостового инвер тора выхрдные напряжения с формой, близкой к синусоидальному закону ШИМ, когда в каждой полуволне выходного на пряжения содержатся высокочастотные импульсы только одной полярности, к недостатку известного устройства необ ходимо отнести слож«ость выполнения блока формирования линейно нарастающих импульсов, что объясняется необходимостью использования в нем сравнивающего цифрового .устройства и дополнительного делителя счетчика, равного по емкости основному делителюсчетчику, который должен переключаться от сигналов дополнительного источника частоты, кратной сигналу внешней частоты, поступающей на вход основного делителя счетчика . Другим недостат ком устройства является достижение симметрии выходного йапряжения инвертора только при значительной-емкости делителя счетчика, -что объясняется дискретностью сравниваемых цифровых сигналов. Несимметрия выходного напря жения инвертора ведет к снижению КПД нагрузки. Целью изобретения является упрощение устройства при повьшенном качестве выходного напряжения Поставленная цель достигается тем, что в устройстве для управления много фазным инвертором, содержащем делитель-счетчик, вход которого соединен с щиной сигнала внешней частоты, и последовательно соединенный с ним делитель в многофазном коде по числу фа инвертора, выходные шины делителя сое динены с первым входом логического блока, выходные шины которого связаны с управляющими входами силовых элементов инвертора, а цифровые выходные шины делителя-счетчика соединены с входом блока формирования импульсов с линейно нарастающей вольт-секундной площадью, выход которого соединен с вторым входом логического блока, делитель-счетчик выполнен двухразрядным, где первый разряд выполнен в многофазном коде с основанием разряда п, а второй разряд выполнен с основанием (п-1); в качестве блока формирования импульсов с линейно нарастающей вольтсекуИдной площадью установлен блок совпадения, первый и второй входы которого соединены соответственно с выходными щинами первого и второго разрядов делителя-счетчика, а в качестве логического блока установлена матричная схема сложения сигналов многофазного кода. На фиг о J приведена структурная схема устройства; на фиг„ 2 - принципиальная схема первого разряда делителя-счетчика в пятифазном коде , (); на фиго 3 - временные диаграммы сигналов этого разряда M(m,m,m.. m,) , соответствующие им сигналы обычного цифрового кода О - 9 и сигналы I О m,in ; II О V 1. т, III О V...V 2 ,; IV. .;.; V ... m,; IV . 1 m.m VII VIII . . m.ffi. IX . 1 Ч т.Й когда на вход делителясчетчика непрерывно поступают сигналы стабильной частоты; на фиг о 4 - принципиальная схема второго разряда делитеяя-счетчика; на фиг 5 - временные диаграммы выходных сигналов L(l ,, И соответствующие им сигналы обычного цифрового кода О на фиг о 6 - принципиальная схема делителя в трехфазном коде; на фиг. 7 - временные диаграммы его выходных сигналов Q(q,, q,, q j) и соответствующие им сигналы обычного цифрового кода О - на фиг 8 - принципиальная схема блока совпадения, где рядом с входными шинами указаны сигналы с выходных шин первого и второго разрядов делителя-счетчика для первого варианта выполнения блока, а сигналы в скобках - для второго варианта вьшолнения этого блока; на фиг, 9,а - временные диаграммы сигналов на выходе блока совпадения и ровые сигналы U- второго разряда делителя счетчика для первого варианта вьшолнения блока совпадения; на фиг« 9,6 - то же, для второго варианта выполнения блока совцадения; на фиго 10 - принципиальная схема сумматора сигналов трехфазного кода; на фиг. 11 - временные диаграммы дифровых сигналов О -5 , эквивалентных трехфазным сигналам Q, трехфазных сигналов qj, q совпадающих по форме с потенциалами ( , qi, (f точек а, b, с, мостового инвертора, выходных напряженой ,, , Ucof для первого варианта блока совпадения; на фиг. 12 - аналогичные временные диаграммы для второго варианта выполнения блока совпадения о Шина внешней частоты f соединена с входом первого разряда 1 делителясчетчика, выходная шина первой фазы т которого соединена с входом второго разряда 2 этого делителя-счетчика. Выходная шина 1 второго разряда соединена с входом делителя 3 Выходные шины разрядов 1 и 2 делителя-счетчика соединены соответственно с первым и вторым вхйдами блока совпадения 4 Выходные шины делителя 3 соединены с первым входом сумматора 5, второй вход которого соединен с выходом бло-т ка 4.Выходные шины сумматора 5 связаны с силовыми ключами трехфазного мостового инвертора 6, содержащего силовые ключи 7-12о Шины сигналов qj, q, q связаны соответственно с ключами 7, 10, 11, шины инверсных сигналов q (,. qj, J «.--.-.- q, -,с ключами 8, 9, 12„ Открытие ключек 7, 9, 11 создает положительный потенциал соответственно точек а, Ь, с стоек инвертора, а открытие ключей 8, 10, 12 - нулевой потенциал этих точек Первый разряд 1 (фиг„ 2) делителясчетчика представляет собой общеизвестную схему счетчика на десять устойчивых состояний, которая вьшолнена, например, на RS-триггерах 13-17, связанных мевду собой вентилями 18-27 на двухвходовых логических схемах И-НЕ Вентили 18, 24, 20, 26, 22 образуют с RS-триггерами первое кольцо счетчика, а вентили 23, t9, 25, 21, 27 второе кольцо. Вторые входы вентилей связи первого и второго колец соединены соответственно с прямым и инверсным выходными шинами счетного триггера 28 входная шина которого является входом 95 ,, , делителя-счетчикао С выходных шин RSтриггеров снимаются сигналы пятифазного кода М(т,, га, т, т, т,,:), Второй разряд 2 (фиг, 4) делителясчетчика представляет собой также общеизвестную схему счетчика на девять устойчивых состояний, которая выполнена аналогично первому разрядуо Схе„ выполнения на RS-триггерах 29-33 вентилями связи между ними 34-43. Вторые входы вентилей 34, 40, 36, 42, з8 первого кольца соединены с выходом логического узла 44, состоящего из двух двухвходовых ьхем И, объединен„ых на выходе при помощи двухвходовой схемы ИЛИо Вторые входы вентилей 39, 35, 41, 37, 43 второго кольца соединены с выходом логического узла 45, аналогичного узлу 44. Первые входы логических схем И узлов 44, 45 соединены с выходными шинами триггера 46, счетный вход которого соединен с выходом логической схемы И 47, Входы схемы И 47 соединены с выходными шинами 1, Л,ГППТВРТРТВРННП Т-ПИГГРППИ 9q ТЧ. RT Oсоответственно триггеров 29, 33, Вторые входы логических схем И узлов 44, 45 соединены с выходными шинами триггера 48, счетный вход которого соединен с входной шиной сигнала т первого разряда. С выходных шин RS-триггеров снимаются выходные сигналы второго разряда Ij - Ij. Делитель 3 (фиг о 6) выполняется аналогично первому.разряду 1 и отличается от него только числом RS-триггеров. Он представляет собойсхему на шесть устойчивых состояний, которая вьшолняется, например, на RS-триггеJDOUH-Jin lCi 1 71 у na.lli./jrnnti т ПО. . 1 J/JTll , pax 49, 50, 51, соединенных между обой вентилями связи 52-57, Вторые входы этих вентилей соединены с выходными шинами счетного триггера 58, на вход которого подается сигнал 1. второго разряда. С выходных шин RSтриггеров снимаются сигналы трехфазного кода / Блок совпадения 4 (фиг.8) представь ляет собой обыкновенную логическую схему и может быть выполнен в двух вариантах Первьш вариант построения блока определяется логическим выражениемP l|ljm,m2V l ljmjinjV Ifl ;Ш,У V 1, IzfiTujV V i ljffi,m,p; (t) 95 а второй вариант - логическим вьфажеР 1Д,,т,т5У liljmjm V l,,rajV 1415m,miV ,m,V V l,l2m,m.V l,jl3m, ,-(2) Отличие этих вариантов заключается только в подключении к выходным пшнам первого разряда делителя-счетчика,Логические слагаемые выражений П),(2) с первого по четвертое реализуются соответственно четырехвходовыми элеИ 59-62, первые два входа ментами подключены к шинам 1,12 z э которых 1з,14; второго разряда делителясчетчика, а вторые два входа - к шинам первого разряда m т- m,m5- для первого варианта, in,m4 m ffij; для второго варианта выполнения блока совпадения. Пятое логи ческое слагаемое вьфажений (1)(2) реа лизуется трехвходовым элементом И 63, первые два входа которого подключены к шинам l),, второго разряда, а трети вход - к шине первого разряда m , - для первого варианта, и к шине т., - для второго варианта вьтолнения блока 4. Логические слагаемые выражений СО (2) с шестого по девятое реализуются соответственно трехвходовыми элементами И 64-.67, к третьему входу которых подключены соответственно двухвходовые элементы И-НЕ 68-71 Первые два входа элементов И 64-67 подключены соответственно к шинам второго разряда, а входы элементов И-НЕ 68-71 подключены к шинам первого разряда соответственно m,m4; т,тудля первого варианта и m, , m,m для второго варианта выполнения блока совпадения 4 о Выходы И 59-67 соединес шинами девятивходового логическо ны го элемента ИЛИ 72, выходная шина которого является выходом блока совпадения , Сумматор 5 представляет собой известную схему, которая реализует следующие обыкновенные логические выражения:q,P V q,P. Один из возможных вариантов выполнения этого сумматора, которьш реализо ван на двухвходовых элементах И-НЕ 73-78, представлен на фиг. 10. Логическая зависимость выражения (3) реализована на элементах 73, 76, 79, где входы элементов 73 подключены к входной шине q:, и шине , а входы элементов 79 - к входной шине q- и шине Р. Выходные шины элементов И-НЕ 73, 79 соединены с входами элемента И-НЕ 76, выходная шина которого является вьгходом первой фазы q сумматора. Логическая зависимость (4) реализована на элементах 74, 77, 80, где входы элемента 80 подключены к входной делителя 3 и шине Р. а входы элементна И-НЕ 74 - к входной шине q и шине Р. Выходные шины элементов 74, 80 соединены с входами элемента И-НЕ 77, выходная пгина которого является выходом второй фазы q сумматора. Логическая зависимость (5) реализована . на элементах 78, 81, 75, где входы элемента 81 подключены к входной шине q и шинеР,а входы элемента 75 - к входной шине qj и шине Р. Выходнь1е шины элементов 75, 81 соединены с входами элемента 78, выходная шина которого является выходом третьей фазы q сумматора. Работу схемы устройства для управления многофазным инвертором рассмотрим на примере трехфазного мостового инвертора при поступлении на вход устройства стабильной частоты f и первоначально для первого варианта выполнения блока совпадения Импульсы частоты f, поступая на входную шину первого разряда, будут переводить его из одного устойчив.ого состояния в другое. При этом устойчивое состояние, эквивалентное цифре О, определяется по выходным сигналам RS-триггеров 13, 14: ,j, второе устойчивое состояние , эквива ентное дифре 1, определяется по выходным сигналам RS-триггеров 14, 15 ,m, и т,До В этом разряде могут быть выделены . также устойчивые состояния, которые определяются нарастающей логической суммой цифр обычного кода I 0 m,m.j; II HI - ,. .o. V .., m ; VI ., . m.,m ,; VII m, VIII . ..7 m,m4; IX .., m,m5c Десятый импульс частоты f возвращает схему первого разряда в исходное состояние (цифра О), Этому 995 моменту соответствует появление сигиа ла m. Сигнал m , поступая каящьм раз на входную шину второго разряда 2, вызывает его переключение из одного устойчивого состояния в другое„ Это переключение происходит аналогично работе первого разряда до состояния, определяемого цифрой 8. Девятый импульс Ш) переводит второй разряд 2 в состояние для цифры 9, когда на выходе .элемента И 47 появляется сигнал 9 l,lj и тем самым переключается счетный триггер 46. Его переключение вызывает изменение сигналов на выходе узлов 44, 45 и переключение второго разряда в исходное нулевое состояние„ Таким образом, в схеме исключается устойчивое состояние, определяемое цифрой Определение сигналов обыч ного цифрового кода здесь производится аналогично первому разряду: О 1 1 . 1 1 1 . II он 1 1 1Д,: 2 1.L : 3 lii . - зч l4l5; 4 14-1,; 5 1.1,; 6 7 2 Ы,.: 8 bi; 213; . И При каждом возвращении второго раз ряда 2 в исходное состояние появляется импульс 1 , который вызывает переключение в делителе 3. Его работа полностью аналогична работе разряда 1 с той лишь разницей, что он имеет шесть устойчивых состояний (см.фиГо) О q q., 1 . ,; 4 , 5 qjq, 3 q.q.; 4 При цифре О в разряде 2 логический элемент И 59 фиксирует совпадение этого сигнала с сигналом 1 О в разряде 1. Поэтому на выходной шине Р элемента 72 за период изменения сигна лов в разряде 1 будет выдан импульс длительностью 0,1 этого периода и сто ящий в начале появления цифры О в разряде 2 (фиг. 9а)о При цифре 1 в разряде 2 логический элемент И 60 фиксирует совпадение этого сигнала с сигналом II в разряде 1, Поэтому на выходной шине элемента ИЛИ 72 за период изменения сигналов в разряде 1 будет вбщан импульс длительностью 0,2 этого периода и стоящий в начале появления цифры 1 в разряд 2 и т„д. Следовательно, за период изменения цифровых сигналов в разряде 2 на выходной шине блока совпадения 4 появляются импульсы с линейно нарастающей вольт-секундной площадью, передний фронт которых совпадает с моментом переключения разряда 2„ Число этих импульсов для рассмотренното варианта выполнения делителя-счетчика равно 9, С целью более наглядного представления работы устройства на фиг,, 11 приведены временные диаграммы, когда число этих импульсов уменьшено, например до четырех На отрезках времени О t t, t f,- tj, когда делитель 3 находится в положении для цифры О , а с выходной шины блока совпадения 4 вьщается сигнал Р 1, сумматор 5 вьщает на вьпсодных шинах кодовую комбинацию сигналов q, 1, q 1 (qL 0) q 0, соответствующую цифре 1 (фиго 7)о При сигнале Р О, что t,-tz соответствует отрезкам времени -2 , .. ,., i. uj сигналы делителя 3 передаются на выходные шины сумматора 5 без изменения q 1; q, OCqC, ь 1). q Оо На отрезках времени t - tg , t t j 1 t - t, когда делитель 3 находится в положении для цифры 1, а с выходной шины блока совпадения 4 выдается сигнал Р 1, сумматор 5 выдает на выходных шинах кодовую комбинацию сигналов q, 1; Ч±- Kq 0); q 1, соответствующую цифре 2 „11ри сигнале Р О, что соответствует отрезкам времени tg- . f2 1Ь , сигналы делителя 3 передаются навыходные 1шны сумлатрра., без изменения q; 1, q; Uqj 0), q 0. - На отрезках времени, t - t, когда делитель 3 находится в положении для цифры 2, а с выходной шины блока совпадения 4 вьщается сигнал Р 1, сумматор 5 вьщает на выходных шинах кодовую комбинацию сигналов q 0 q - 1 (q 2 0) ; q 3 1 соответствующую цифре При сигнале Р О, что соответствует отрезкам времени п If - 7(1 4 сигналы делителя 3 передаются.на выходные шины сумматора без изменения q, 1 q2 i(qt 0); q 1 и т.д. Выходные напряжения инвертора 6 Uo,b Yc,-lt; ut,c /fo- с Uc., при этом изменяются по трапецендальному закону ШИМ, когда в каждой полуволне выходного напряжения содержатся высокочастотные импульсы одной полярности. При выполнении блока совпадения по второму варианту, когда за период изменения сигналов на втором разряде на выходной шине блока 4 так95же появляются импульсы с.линейно нара стающей вольт-секундной площадью, зад ний фронт этих импульсов будет совпадать с моментом переключения второго разряда 2.0 Работа устройства в этом случае не отличается от описанной вынапряжений (см, фиго 12) несколько отличаются от первого варианта. Таким образом, предложенная схема устройства значительно проще известного решения: схема блока совпадения :12 содержит всего девять логических схем И и одну схему ИЛИ (для приведенного примера вьшолнения) вместо второго делителя-счетчика (56 элементов И, 2 элемента ИЛИ) и схемы сравнения цифровых сигналов делителей счетчиков, число элементов которой примерно равно делителю-счетчикуо Схема обеспечивает при этом в отличие от известного решения полную симметрию выходного напряжения при любых .соотношениях частот модуляции, что ведет к повьппению КПД,

tn

ITJy

и,иЧн7Ч..5 и игиЧ.И

Т Ж

Ж

ж т ж ж ж ж

Фиг.Ь

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод переменного тока | 1979 |

|

SU961087A1 |

| Вентильный двигатель | 1980 |

|

SU944472A2 |

| Цифроаналоговый преобразователь с многофазным выходом | 1987 |

|

SU1476611A1 |

| Устройство для управления инвертором с широтно-импульсной модуляцией | 1984 |

|

SU1711306A1 |

| Способ управления вентильным двигателем и устройство для его осуществления | 1979 |

|

SU807973A1 |

| Устройство для управления трехфазным инвертором | 1986 |

|

SU1791939A1 |

| Устройство для управления @ -фазным инвертором | 1983 |

|

SU1252883A1 |

| Цифроаналоговый преобразователь с многофазным выходом | 1985 |

|

SU1356225A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для управления 3-фазным инвертором | 1979 |

|

SU1039014A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ МНОГОФАЗНЫМ ИНВЕРТОРОМ, содержащее делитель-счетчик, вход которого соединен с шиной сигнала внешней частоты, и последовательно соединенный с ним делитель в многофазном коде по числу фаз инвертора, выходные шины делителя соединены с первым входом логического блока, выходные шины которого связаны с управляющими входами силовых элементов инвертора, а цифровые выходные шины делителя-сметчиИзобретение относится к преобразовательной технике и может быть исполь зовано в системах электропитания и электропривода для преобразования постоянного напряжения в многофазное переменное напряжение,модулированное по синусоидальному закону широтно-импульсной модуляции (ШИМ) с жестким алгоритмом переключения силовых элементов инвертора. Известна схема управления многофазным инвертором с жестким алгоритмом ШИМ силовых элементов, где сигналы для их переключения получают в логическом устройстве из цифр делителя-счетчика и последовательно соединенного с ним дека соединены с входом блока формирования импульсов с линейно-нарастающей вольт-секундНой площадью, выход которого соединен с вторым входом логического блока, отличающееся тем, что, с целью упрощения при повышении качества выходного напряжения делитель-счетчик выполнен двухразрядным, где первый разряд выполнен в многофазном коде с основанием разряда п, а второй разряд выполнен с основанием (п-1); причем в качестве блока формирования импульсов с .линейно нарастающей вольт-секундной площадью установлен блок совпадения, первый и второй входы которого соединены соответственно с выходными шинами первого и (Л второго разрядов делителя-счетчика, а в качестве логического блока установлена матричная схема сложения сигналов многофазного кода. UD сл ел лителя в многофазном коде (коде Либау00 00 Крейга, Джонсона и т„До), который может рассматриваться как старший разряд делителя-счетчика, В этой схеме воз- . можно любое оптимальное задание закона приближения переключения силовых элементов, когда в каждой полуволне содержатся высокочастотные импуль гы только одной полярности, что обеспечивает хорошее приближение к синусоиде. Однако задание такой формы выходного напряжения возможно здесь только при использовании в силовой части однофазных мостовых инверторовр что приводит к завышению установленной мощности инвертора

45 Фиг.4

0Lf {,r,3n.4l..ffn.

U 0 . 2 „ „ S4

Фиг.5 (ригЛ

-е

II П П П

ПЛЛ П П

.о п1 . 2 п

ппп д

1

-/-У-./.,

;1пппп w,.|fnnnf

,м пппг

1,

igtgiioij}ttiit ffftjsi

1 ППП11ППП

ппп

тгаиг

Р

Фиг.Ю

4 „S

П nnnt

11

1ППП П

JUUU о

аил.

ппппг

L

ШШ

t bS- Tt -fcP

40

l D Z3

Г

Авторы

Даты

1990-08-15—Публикация

1978-11-10—Подача