I I S)/I

J 4j

xi О

ьо со

00

|ГО

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ЧАСТОТ | 2001 |

|

RU2214043C2 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2416158C1 |

| Синтезатор частот | 1978 |

|

SU794706A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1483632A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

Изобретение относится к радиотехнике и может быть использовано в приемопередающей и контрольно-измерительной аппаратуре Целью изобретения является расширение диапазона выходных частот в сторону частот меньших опорной частоты Синтезатор дискретной сетки частот содержит опорный генератор 1 блок памяти 2 первый контур фазовой автоподстройки частоты (ФАПЧ) 3 который состоит из первого и второго делитепей частоты с переменным коэффициентом деления (ДПКД) 4, 5 первого фазового компаратора (ФК) 6, первого фильтра нижних частот 7 и первого управляемого генератора (УГ) 8 второй контур ФАПЧ 9, который состоит из третьего и четвертого ДПКД 10 11 второго ФК 12 второго фильтра нижних частот 13 и второго УГ 14 счетчик 15 блок сравнения кодов 16 первый мультиплексор 17 первый сумматор вычитатель 18 второй сумматор-вычи- татель 19 и второй мультиплексор 20 Счетчик 15 блок сравнения кодов 16 первый и второй мультиплексоры 17 20 первый и второй сумматоры вычитатели 18 19 производят арифметико-логическую коммутацию, задание и управление коэффициентами деления всех ДПКД 4 5 10 11 таким образом что диапазон выходных частот расширяется в сторону частот мень ших опорной частоты 1 ил

,l ч 1

J ,

Изобретение относится к радиотехнике и может быть использовано в приемопередающей и контрольно-измерительной аппаратуре.

Целью изобретения является расширение диапазона выходных частот в сторону частот, меньших опорной частоты.

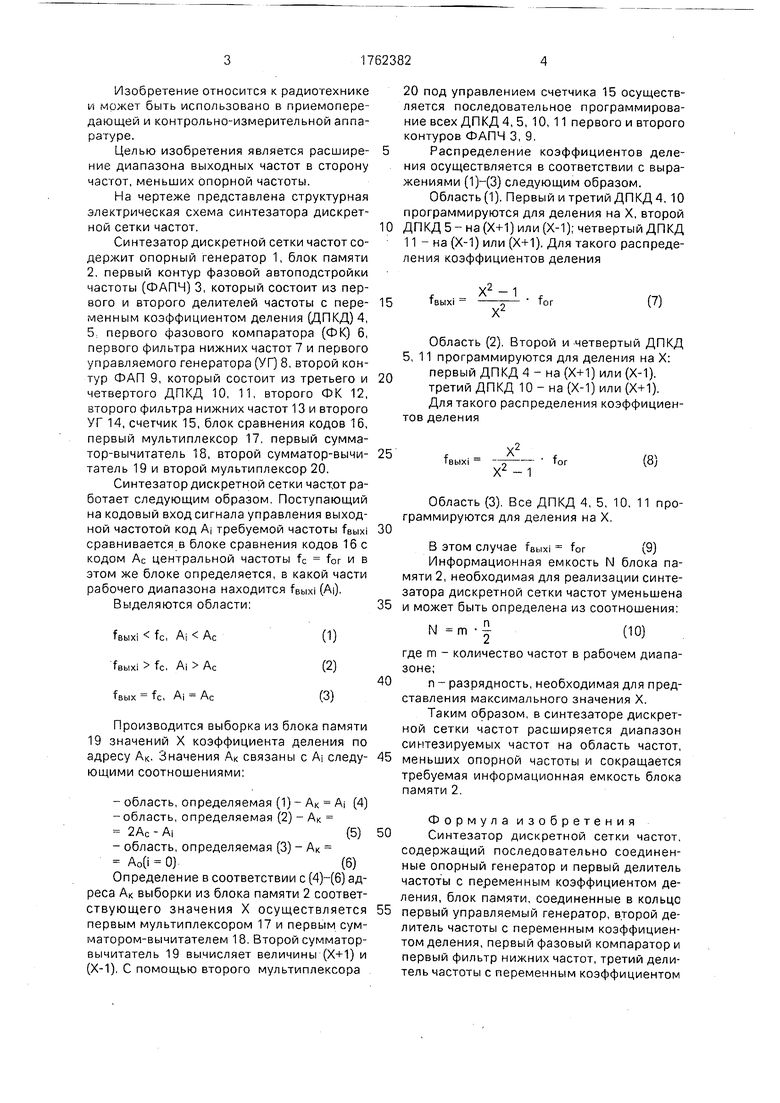

На чертеже представлена структурная электрическая схема синтезатора дискретной сетки частот.

Синтезатор дискретной сетки частот содержит опорный генератор 1, блок памяти 2, первый контур фазовой автоподстройки частоты (ФАПЧ) 3, который состоит из первого и второго делителей частоты с переменным коэффициентом деления (ДПКД) 4, 5 первого фазового компаратора (ФК) 6, первого фильтра нижних частот 7 и первого управляемого генератора (УГ) 8, второй контур ФАП 9, который состоит из третьего и четвертого ДПКД 10, 11, второго ФК 12, второго фильтра нижних частот 13 и второго УГ 14, счетчик 15, блок сравнения кодов 16, первый мультиплексор 17, первый сумма- тор-вычитатель 18, второй сумматор-вычи- татель 19 и второй мультиплексор 20.

Синтезатор дискретной сетки частот работает следующим образом. Поступающий на кодовый вход сигнала управления выходной частотой код А: требуемой частоты fBbixi сравнивается в блоке сравнения кодов 16 с кодом Ас центральной частоты fc for и в этом же блоке определяется, в какой части рабочего диапазона находится fBbixi (Ai).

Выделяются области:

Ai Ac

Ai Ac

Ai Ac

(1)

(2) (3)

Производится выборка из блока памяти 19 значений X коэффициента деления по адресу Ак. Значения Ак связаны с Ai следующими соотношениями:

-область, определяемая (1) - Ак AJ (4)

-область, определяемая (2) - Ак

2Ac-Ai(5)

-область, определяемая (3) - Ак

Ao(i 0)(6)

Определение в соответствии с (4)-(6) адреса Ак выборки из блока памяти 2 соответствующего значения X осуществляется первым мультиплексором 17 и первым сум- матором-вычитателем 18. Второй сумматор- вычитатель 19 вычисляет величины (Х+1) и (Х-1). С помощью второго мультиплексора

0

20 под управлением счетчика 15 осуществляется последовательное программирование всех ДПКД 4, 5, 10, 11 первого и второго контуров ФАПЧ 3, 9.

Распределение коэффициентов деления осуществляется в соответствии с выражениями (1)-(3) следующим образом.

Область (1). Первый и третий ДПКД 4, 10 программируются для деления на X, второй ДПКД 5 - на (Х+1) или (Х-1); четвертый ДПКД 11 - на (Х-1) или (Х+1). Для такого распределения коэффициентов деления

ВЫХ1

X2-1 X2

(7)

Область (2). Второй и четвертый ДПКД 5, 11 программируются для деления на X:

первый ДПКД 4 - на (Х+1) или (Х-1).

третий ДПКД 10 - на (Х-1) или (Х+1).

Для такого распределения коэффициентов деления

25

1

(8)

Область (3). Все ДПКД 4, 5, 10, 11 программируются для деления на X.

В этом случае fBbixi for(9)

Информационная емкость N блока памяти 2, необходимая для реализации синтезатора дискретной сетки частот уменьшена и может быть определена из соотношения:

(Ю)

0

5

0

5

где m - количество частот в рабочем диапазоне;

п - разрядность, необходимая для представления максимального значения X.

Таким образом, в синтезаторе дискретной сетки частот расширяется диапазон синтезируемых частот на область частот, меньших опорной частоты и сокращается требуемая информационная емкость блока памяти 2.

Формула изобретения Синтезатор дискретной сетки частот, содержащий последовательно соединенные опорный генератор и первый делитель частоты с переменным коэффициентом деления, блок памяти, соединенные в кольце первый управляемый генератор, второй делитель частоты с переменным коэффициентом деления, первый фазовый компаратор и первый фильтр нижних частот, третий делитель частоты с переменным коэффициентом

деления, соединенные в кольцо второй управляемый генератор, четвертый делитель частоты с переменным коэффициентом деления, второй фазовый компаратор и второй фильтр нижних частот, при этом выход первого делителя частоты с переменным коэффициентом деления соединен с другим входом первого фазового компаратора, другой вход второго фазового компаратора соединен с выходом третьего делителя с переменным коэффициентом деления, вход которого подключен к выходу первого управляемого генератора, отличающий- с я тем, что, с целью расширения диапазона выходных частот в сторону частот, меньших опорной частоты, введены счетчик, блок сравнения кодов, первый мультиплексор, первый сумматор-вычитатель, второй сум- матор-вычитатель и второй мультиплексор, при этом выходная шина адреса счетчика соединена с управляющими входами блока сравнения кодов, первого и второго мультиплексоров, первого и второго сумма- торов-вычитателей, адресными входами первого, второго, третьего и четвертого де- лителей частоты с переменным коэффициентом деления, первый кодовый вход блока сравнения кодов соединен с первым кодовым входом первого сумматора-вычитателя

и является входом кодового сигнала управления выходной частотой синтезатора дискретной сетки частот, второй кодовый вход блока сравнения кодов является кодовым сигналом задания центральной частоты синтезатора дискретной сетки частот, выход блока сравнения кодов соединен с управляющим входом первого мультиплексора, выход которого соединен с вторым кодовым входом первого сумматора-вычитателя, выход которого соединен с адресным входом блока памяти, первый кодовый информационный вход второго мультиплексора соединен с кодовым информационным входом -второго сумматора-вычитателя и подключен к выходу блока памяти, выходная шина данных второго мультиплексора соединена с установочными входами первого, второго, третьего и четвертого делителей с переменным коэффициентом деления, вход счетчика является входом сигнала тактовой частоты синтезатора дискретной сетки частот, а первый и второй кодовые информационные входы первого мультиплексора являются входами кодовых сигналов задания соответственно нижнего и верхнего поддиапазонов синтезатора дискретной сетки частот.

| Нисневич Д Г Вычислительные алгоритмы синтеза частот Ж Техника средств связи, серия ТРС, вып 3 1981 |

Авторы

Даты

1992-09-15—Публикация

1990-06-28—Подача