Изобретение относится к автоматике и вычислительной технике и может быть ис- . пользовано при создании машин баз данных.

Известен матричный процессор, содержащий 256 процессорных элементов (ПЭ), подразделенный на 4 квадрата по 64 ПЭ каждый квадрат управляется собственным устройством управления, каждая группа ПЭ связана с файловыми дисками (Ф Д), так же с коммутатором ввода-вывода и контроллером ввода-вывода. ФД соединен с буфером ввода-вывода.

Недостаток этого устройства заключается в том, что операции внутри каждого квадрата ПЭ могут работать только параллельно и в режиме пошаговой обработки, что ограничивает его функциональные возможности.

Известен другой матричный процессор под названием массивный параллельный процессор, весь блок массива содержит 128x128 ПЭ с четырьмя избыточными столбцами, переключатели, там же входной и выходной регистры, устройства управления массивом, устройство управления программными данными.

Недостаток этого устройства заключается в том, что оно имеет.ограниченные функциональные возможности и большие аппаратурные затраты.

Наиболее близким к предлагаемому процессору является ассоциативный матричный процессор, содержащий память (ПОБ)операционногочлена с произвольным доступом, операционные блоки (ОБ), (матричный процессор разделен на 32 блока, каждый из которых содержит 32 ОБ, блок управления и канал ввода-вывода, причем 1-й ОБ соединен с первыми в/в ПОБ, i-й ПЭ соединен с j-й ПЭ с помощью линии связи (мультиплексор) xiyi и zizj - переключает i-ю ячейку с ячейками под номерами (i-8)-(i+7), yi - соединяет i-ю ячейку с мультиплексором Zj, zi+16, zi+32 мультиплексор xj соединяет i-ю ячейку с мультиплексорами yi, yi+i28 и т.д.,

С

х| Ю СЛ

4Ь О

VI

устройство управления подключенные к каждому ОБ, вторые входы-выходы (в/в) 1-й ПОБ соединены с шиной ввода-вывода.

Основным недостатком известного устройства является сравнительно невысокие быстродействия, связанное с ограниченно-, стью связей как между ОБ, так и между ПОБ.

Наиболее близким к предлагаемому процессору является ассоциативный матричный процессор, содержащий матрицы размером НхН операционных блоков, где Н - линейный размер обрабатываемых данных, матрицу размером НхН блоков памяти, блок управления, первую группу узлов коммутации, узел коммутации, причем первый выход блока управления подключен куправ- ляющим входам узлов коммутации первой группы, второй и третий выходы блока управления подключены соответственно ко входам режима блоков памяти матрицы блоков памяти и ко входам кода операции ОБ, четвертый выход блока управления подключен к управляющему входу узла коммутации.

Основным недостатком известного устройства, также, является сравнительно невысокое быстродействие, связанное с ограниченностью связей как между операционными блоками и памятью, так и между блоками памяти.

Цель изобретения - повышение быстродействия и расширение функциональных возможностей.

Поставленная цель достигается тем, что в устройство, содержащее матрицу операционных блоков, матрицу блоков памяти, блок управления, первую группу узлов коммутации, узел коммутации, дополнительно введены: вторая группа узлов коммутации и блок ввода-вывода, первый вход-выход бло- .ка управления подключен к первым информационным входам-выходам блоков памяти матрицы блоков памяти, второй информационный вход-выход блока управления под- ключен к первым информационным входам-выходам операционных блоков, первый выход блока управления подключен к управляющим входам узлов коммутации второй группы, второй информационный вход-выход операционного блока а-й строки b-го столбца матрицы операционных блоков (где а, .,.,.,Н) подключен ко второму информационному входу-выходу блока памяти а-й строки b-го столбца матрицы блоков памяти, с-й выход d-ro узла коммутации первой группы (где с, d-1,...,H) подключен к информационному входу блока памяти с-го столбца d-й строки матрицы блоков памяти, с-й выход d-ro узла коммутации второй группы подключен к информационному вх(

ду операционного блока с-го столбца d-й строки матрицы операционных блоков, выход блока памяти с-го столбца d-й строки матрицы блоков памяти подключен к с-му

информационному входу d-ro узла коммутации первой группы, выход операционного блока с-го столбца d-й строки матрицы операционных блоков подключен к с-му информационному входу d-ro узла коммутации

0 второй группы, первый информационный вход-выход с-го узла коммутации первой группы (где ,...,Н-1) подключен к первому информационному входу-выходу (е+1)-го узла коммутации первой группы, первый ин5 формационный вход-выход е-го узла

коммутации второй группы подключен к

первому информационному входу-выходу

. (е+1)-го узла коммутации второй группы, второй информационный вход-выход а-го

0 узла коммутации первой группы подключен к а-у информационному входу-выходу группы блока ввода-вывода и а-у информационному входу-выходу второй группы узла коммутации, пятый выход блока управления

5 подключен к управляющему входу блока ввода-вывода, информационный вход-выход которого подключен к информационному входу-выходу ассоциативного матричного процессора, вход кода опера0 ции которого подключен ко входу режима блока управления.

Отсутствие в аналогичных технических решениях перечисленных признаков, отличающих заявляемое техническое решение

5 от прототипа, обуславливает соответствие заявляемого устройства ассоциативного матричного процессора критерию существенные отличия. Наличие новых связей по- зволяет повысить быстродействие

0 устройства. Организация связей между i-й и j-й памятью, позволяют осуществить передачу данных за более короткий промежуток времени, так же наличие связей между ПСОБ и ЦСП позволяет увеличить быстро5 действие за счет подключения п-операцион- ных блоков к одной ПОБ.

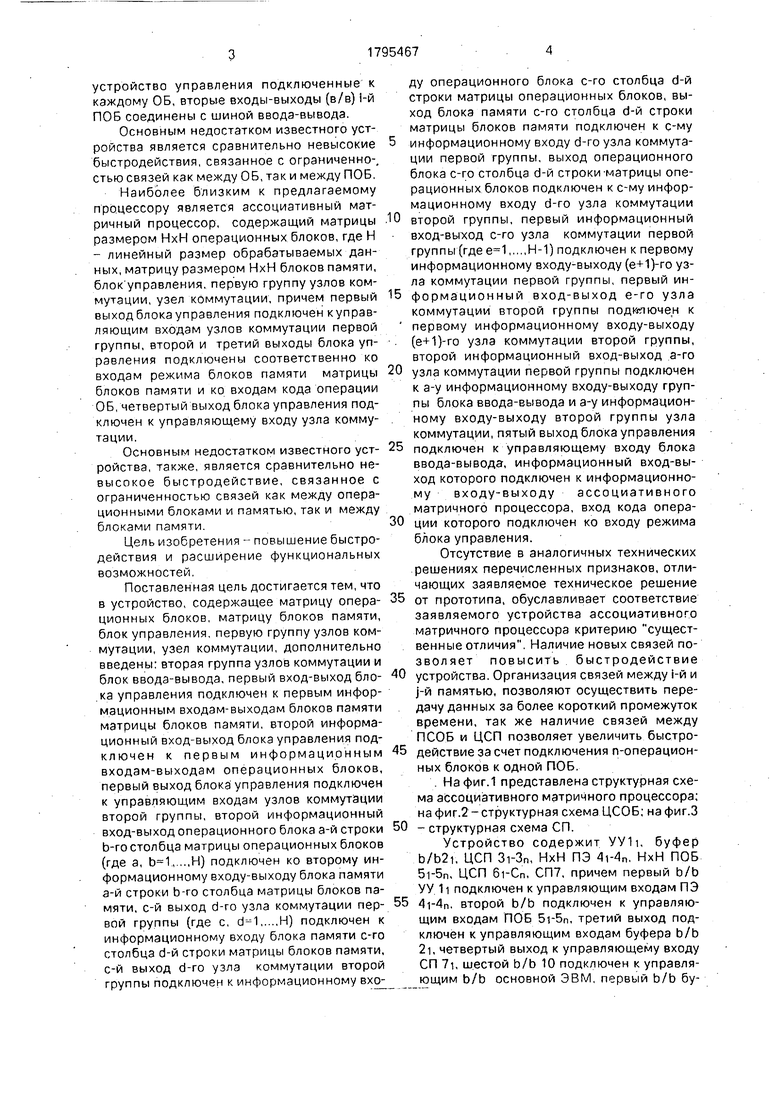

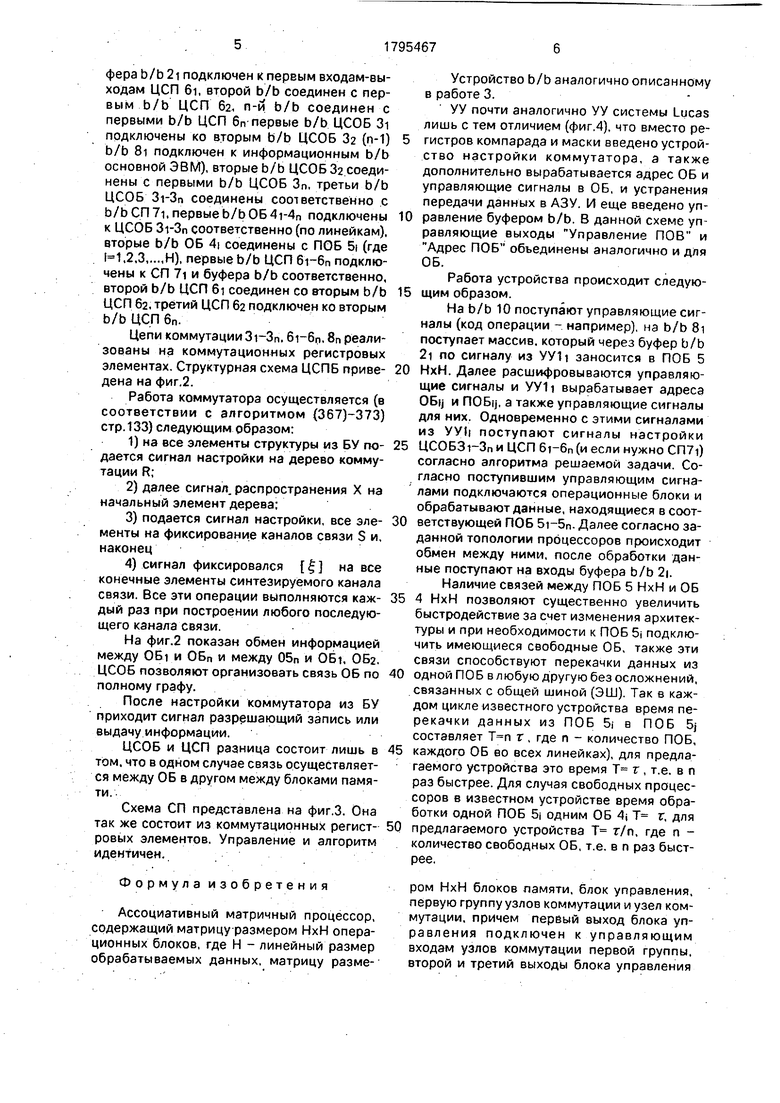

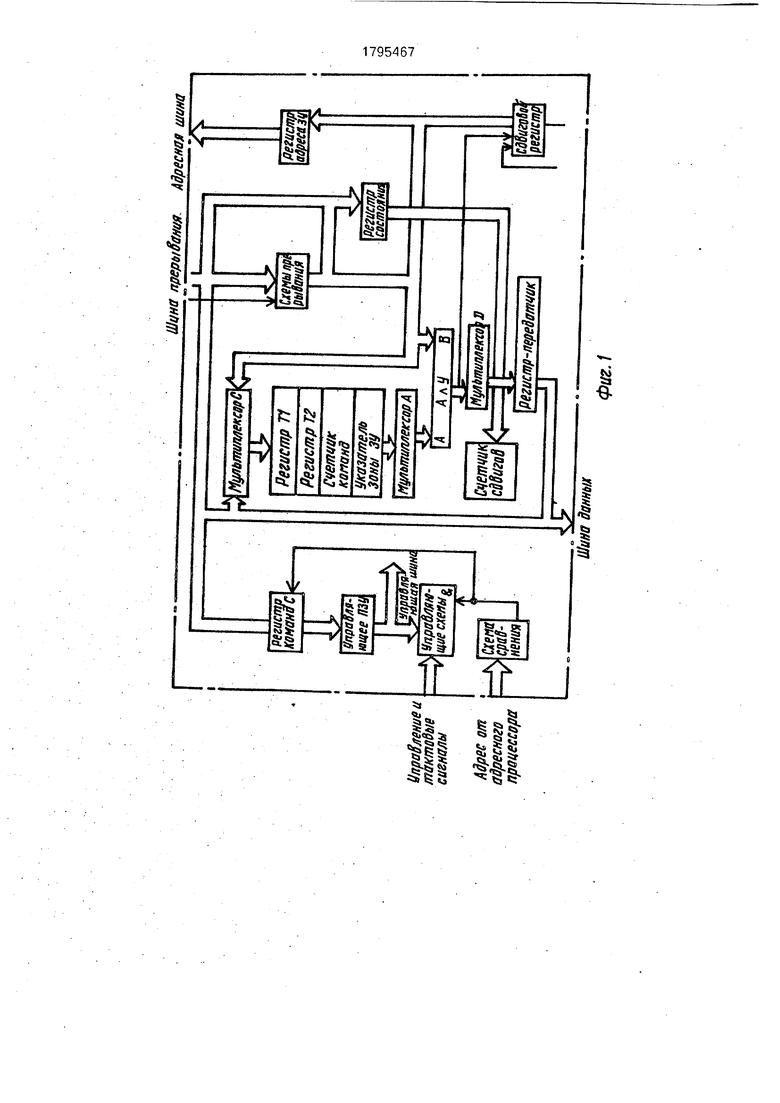

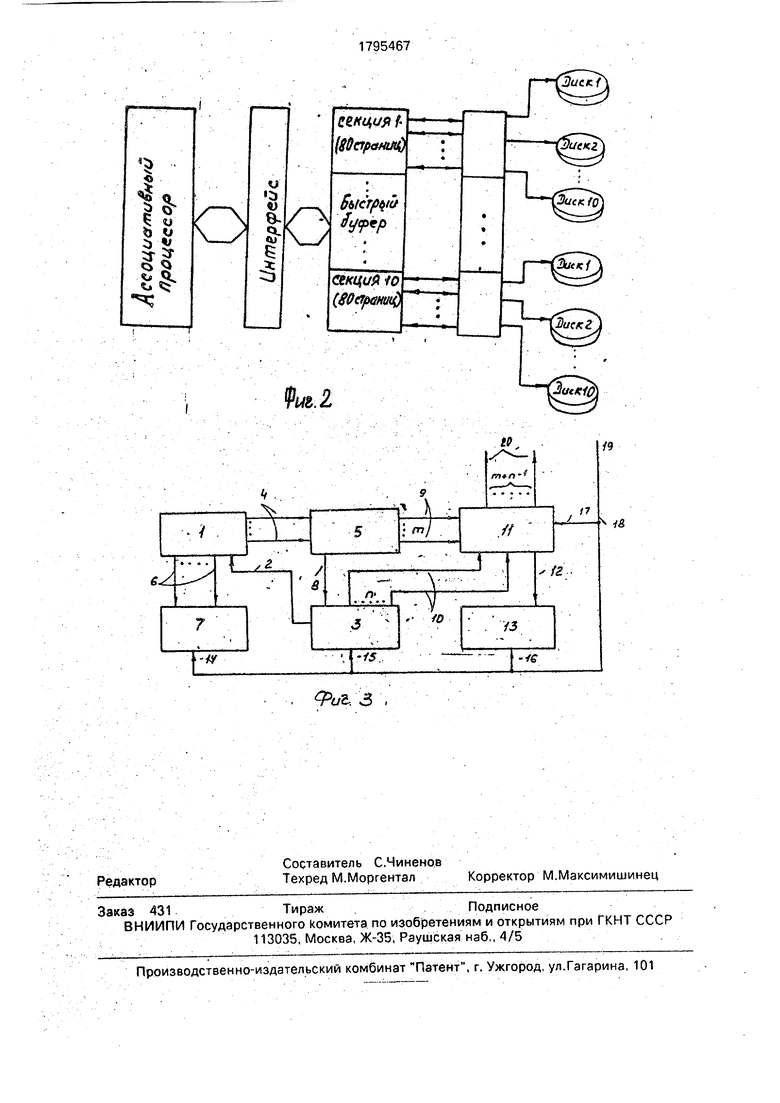

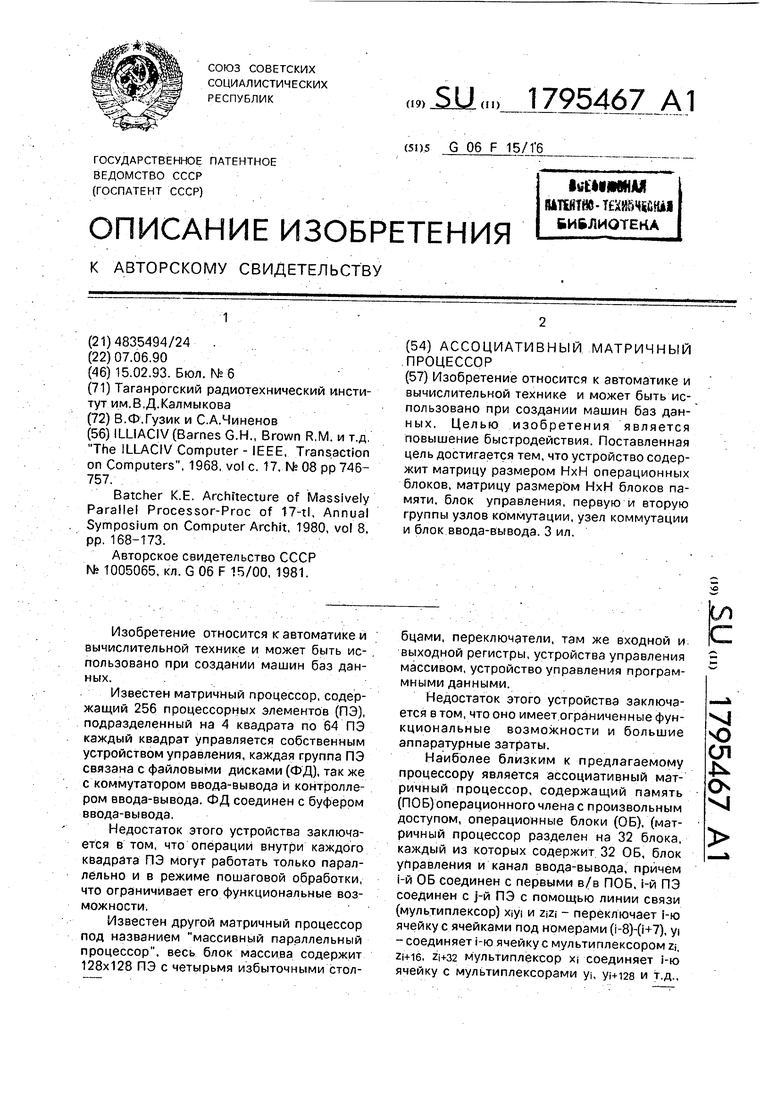

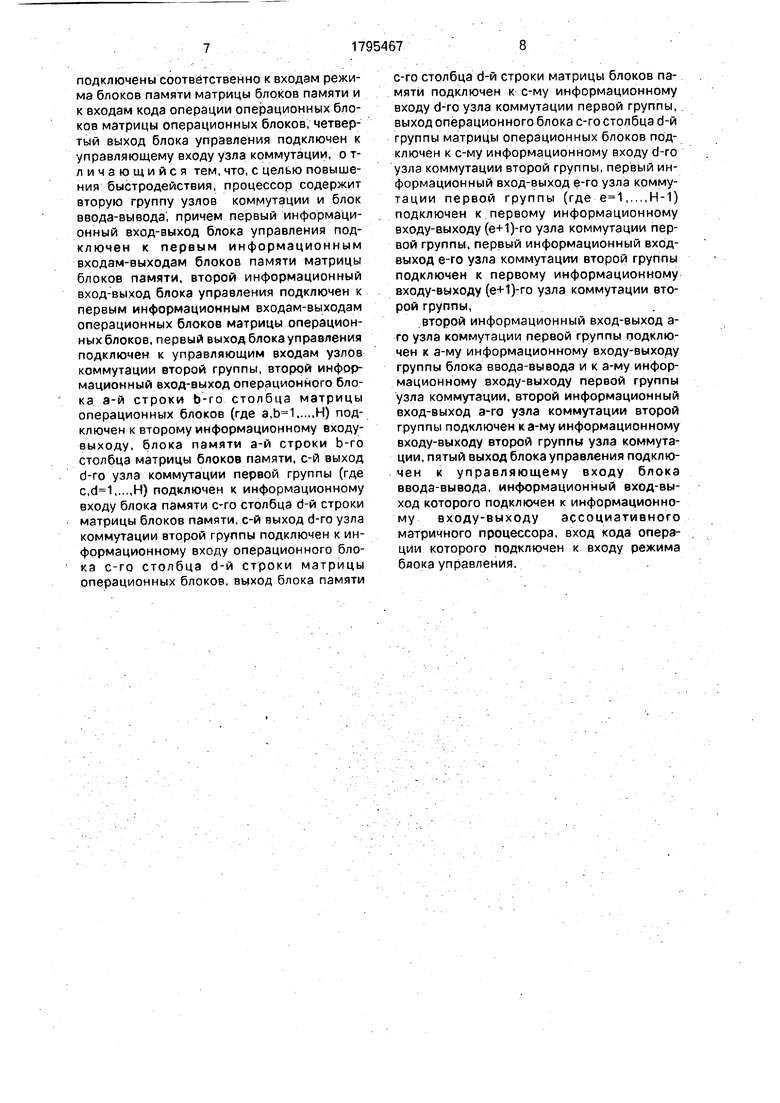

. На фиг.1 представлена структурная схема ассоциативного матричного процессора; нафиг.2-структурная схема ЦСОБ; нафиг.З

0 - структурная схема СП.

Устройство содержит УУИ, буфер b/b2v, ЦСП 3i-3n, НхН ПЭ 4Нп, НхН ПОБ 5i-5n, ЦСП 6i-Cn, СП7, причем первый b/b УУ 11 подключен к управляющим входам ПЭ

5 4i-4n. второй b/b подключен к управляющим входам ПОБ 5г5п, третий выход подключен к управляющим входам буфера b/b 2i, четвертый выход к управляющему входу СП 7т, шестой b/b 10 подключен к управля- ющим b/b основной ЭВМ, первый b/b буфера b/b 21 подключен к первым входам-выходам ЦСП 6i, второй b/b соединен с первым b/b ЦСП 62, п-и fa/b соединен с первыми b/b ЦСП бп первые b/b ЦСОБ 3i подключены ко вторым b/b ЦСОБ 32 (п-1) b/b 81 подключен к информационным b/b основной ЭВМ), вторые b/b ЦСОБ 32 соединены с первыми b/b ЦСОБ Зп, третьи b/b ЦСОБ 3i-3n соединены соответственно с b/b СП 7i. первые b/b ОБ 4i-4n подключены к ЦСОБ 3t-3n соответственно (по линейкам), вторые b/b ОБ 4| соединены с ПОБ 5i (где .2,3,...,Н), первые b/b ЦСП подключены к СП 7i и буфера b/b соответственно, второй b/b ЦСП 6т соединен со вторым b/b ЦСП 62, третий ЦСП 6а подключен ко вторым b/b ЦСП 6П.

Цепи коммутации 3i-3n. 61-60.8П реализованы на коммутационных регистровых элементах. Структурная схема ЦСПБ приве- дена на фиг.2.

Работа коммутатора осуществляется (в соответствии с алгоритмом (367)-373) стр. 133) следующим образом:

1) на все элементы структуры из БУ по- дается сигнал настройки на дерево коммутации R;

2) далее сигнал, распространения X на начальный элемент дерева:

3) подается сигнал настройки, все эле- менты на фиксирование каналов связи S и, наконец

4) сигнал фиксировался {Ј на все конечные элементы синтезируемого канала связи. Все эти операции выполняются каж- дый раз при построении любого последующего канала связи.

На фиг.2 показан обмен информацией между ОБ.1.И ОБП и между 05п и OBi, ОБ2. ЦСОБ позволяют организовать связь ОБ по полному графу.

После настройки коммутатора из БУ приходит сигнал разрешающий запись или выдачу информации.

ЦСОБ и ЦСП разница состоит лишь в том. что в одном случае связь осуществляется между ОБ в другом между блоками памяти.

Схема СП представлена на фиг.З. Она так же состоит из коммутационных регист- ровых элементов. Управление и алгоритм идентичен.

Формула изобретения

Ассоциативный матричный процессор, содержащий матрицу размером НхН операционных блоков, где Н - линейный размер обрабатываемых данных, матрицу размеУстройство b/b аналогично описанному в работе 3.

УУ почти аналогично УУ системы Lucas лишь с тем отличием (фиг.4), что вместо регистров компарада и маски введено устройство настройки коммутатора, а также дополнительно вырабатывается адрес ОБ и управляющие сигналы в ОБ, и устранения передачи данных в АЗУ. И еще введено управление буфером b/b. В данной схеме управляющие выходы Управление ПОВ и Адрес ПОБ объединены аналогично и для ОБ.

Работа устройства происходит следующим образом.

На b/b 10 поступают управляющие сигналы (код операции - например), на b/b 81 поступает массив, который через буфер b/b 2i по сигналу из УУ11 заносится в ПОБ 5 НхН. Далее расшифровываются управляющие сигналы и УУ11 вырабатывает адреса ОБц и nOBij, а также управляющие сигналы для них. Одновременно с этими сигналами из УУ1| поступают сигналы настройки ЦСОБЗг-Зп и ЦСП 6i-6n (и если нужно CR7i) согласно алгоритма решаемой задачи. Согласно поступившим управляющим сигналами подключаются операционные блоки и обрабатывают данные, находящиеся в соответствующей ПОБ 5i-5n. Далее согласно заданной топологии процессоров происходит обмен между ними, после обработки данные поступают на входы буфера b/b 2i.

Наличие связей между ПОБ 5 НхН и ОБ 4 НхН позволяют существенно увеличить быстродействие за счет изменения архитектуры и при необходимости к ПОБ 5i подключить имеющиеся свободные ОБ, также эти связи способствуют перекачки данных из одной ПОБ в любую другую без осложнений, связанных с общей шиной (ЭШ). Так в каждом цикле известного устройства время перекачки данных из ПОБ 5; в ПОБ 5j составляет т, где п - количество ПОБ, каждого ОБ во всех линейках), для предлагаемого устройства это время Т т, т.е. в п раз быстрее. Для случая свободных процессоров в известном устройстве время обработки одной ПОБ 5| одним ОБ 4j T г, для предлагаемого устройства Т г/п, где п - количество свободных ОБ, т.е. в п раз быстрее.

ром НхН блоков памяти, блок управления, первую группу узлов коммутации и узел коммутации, причем первый выход блока управления подключен к управляющим входам узлов коммутации первой группы, второй и третий выходы блока управления

подключены соответственно к входам режима блоков памяти матрицы блоков памяти и к входам кода операции операционных блоков матрицы операционных блоков, четвертый выход блока управления подключен к управляющему входу узла коммутации, о т- личающийся тем, что, с целью повышения быстродействия, процессор содержит вторую труппу узлов коммутации и блок ввода-вывода, причем первый информационный вход-выход блока управления подключен к первым информационным входам-выходам блоков памяти матрицы блоков памяти, второй информационный вход:выход блока управления подключен к первым информационным входам-выходам операционных блоков матрицы операционных блоков, первый выход блока управления подключен к управляющим входам узлов коммутации второй группы, второй информационный вход-выход операционного блока а-й строки b-го столбца матрицы операционных блоков (где а,.....Н) подключен к второму информационному входу- выходу, блока памяти а-й строки Ь-го столбца матрицы блоков памяти, с-й выход d-ro узла коммутации первой группы (где c,,...-,H) подключен к информационному входу блока памяти с-го столбца d-й строки матрицы блоков памяти, с-й выход d-ro узла коммутации второй группы подключен к информационному входу операционного блока с-го столбца d-й строки матрицы операционных блоков, выход блока памяти

с-го столбца d-й строки матрицы блоков памяти подключен к с-му информационному входу d-ro узла коммутации первой группы, выход операционного блока с-го столбца d-й группы матрицы операционных блоков подключен к с-му информационному входу d-ro узла коммутации второй группы, первый информационный вход-выход е-ro узла коммутации первой группы (где ,..,,Н-1) подключен к.первому информационному входу-выходу (е+1)-го узла коммутации первой группы, первый информационный вход- выход е-ro узла коммутации второй группы подключен к первому информационному входу-выходу (е+1)-го узла коммутации второй группы,

второй информационный вход-выход а- го узла коммутации первой группы подключен к а-му информационному входу-выходу группы блока ввода-вывода и к а-му информационному входу-выходу первой группы узла коммутации, второй информационный вход-выход а-ro узла коммутации второй группы подключен к а-му информационному входу-выходу второй группы узла коммутации, пятый выход блока управления подклю- чен к управляющему входу блока ввода-вывода, информационный вход-выход которого подключен к информационному входу-выходу ассоциативного матричного процессора, вход кода операции которого подключен к входу режима блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный процессор | 1985 |

|

SU1354204A1 |

| Матричный процессор | 1987 |

|

SU1534466A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1269151A1 |

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1501081A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Устройство умножения булевых матриц | 1980 |

|

SU959063A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании машин баз данных, Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что устройство содержит матрицу размером НхН операционных блоков, матрицу размером НхН блоков памяти, блок управления, первую и вторую группы узлов коммутации, узел коммутации и блок ввода-вывода. 3 ил.

| ILLIACIV(Barnes G.H., Brown R,M | |||

| и т.д | |||

| The ILLACIV Computer - IEEE, Transaction on Computers, 1968, vole | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Batcher K.E | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-15—Публикация

1990-06-07—Подача