Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения быстродействующих арифметических устройств.

Цель изобретения - повышение быстродействия одноразрядного четверичного сумматора

Одноразрядный четверичный сумматор содержит два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, мажоритарный элемент с порогом четыре и мажоритарный элемент с поргом два. Причем 1-й ) вход первого элемента СЛОЖЕНИЕ ПО МОДУЛЮДВА соединен с входом старшего разряда 1-й четверичной цифры, а выход соединен с выходом старшего разряда суммы, выход младшего разряда которой соединен с выходом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА. Далее i-й вход второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединен с входом младшего разряда 1-й четверичной цифры, третий вход соединен с входом переноса сумматора. Выход мажоритарного элемента с порогом два соединен с третьим входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, а 1-й вход соединен с входом младшего разряда 1-й четверичной цифры и i-м входом мажоритарного элемента с порогом четыре, третий вход соединен с входом переноса сумматора и третьим входом мажоритарного элемента с порогом четыре. Причем (1+3) и вход мажоритарного элемента с порогом четыре соединен с входом старшего разряда пер00 КЭ VI О XI Ю

вой четверичной цифры. 0+5)-й вход соединен с входом старшего разряда второй четверичной цифры, а выход соединен с выходом переноса сумматора.

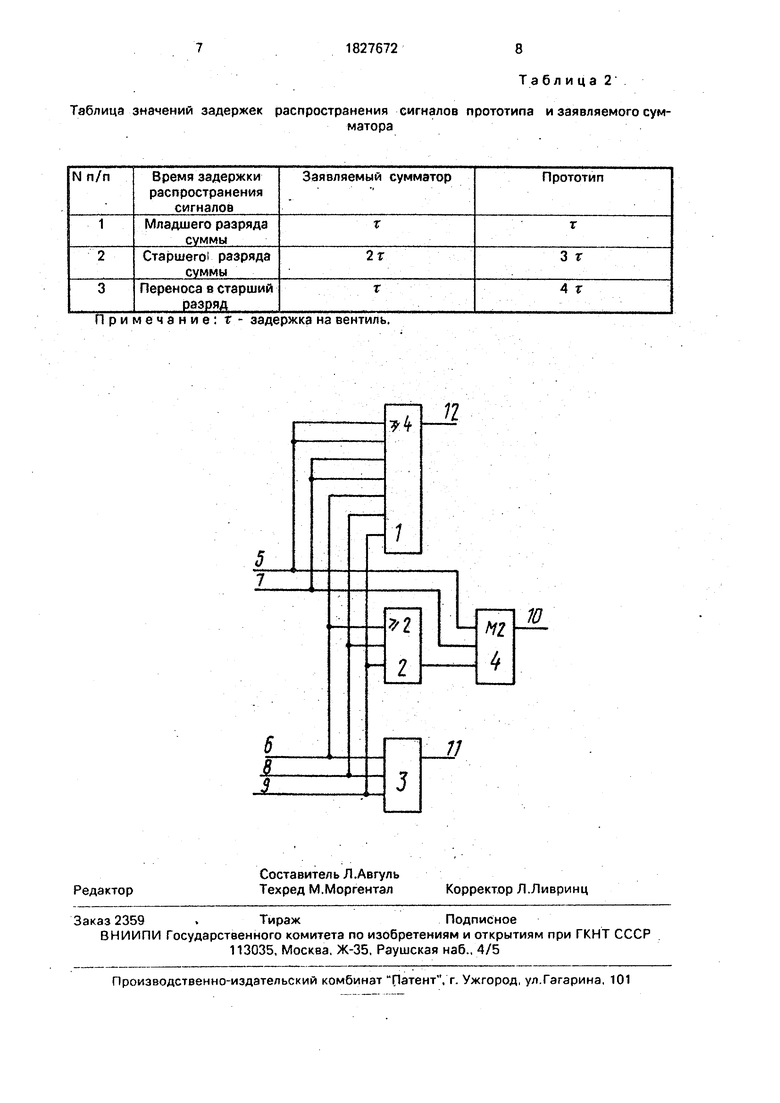

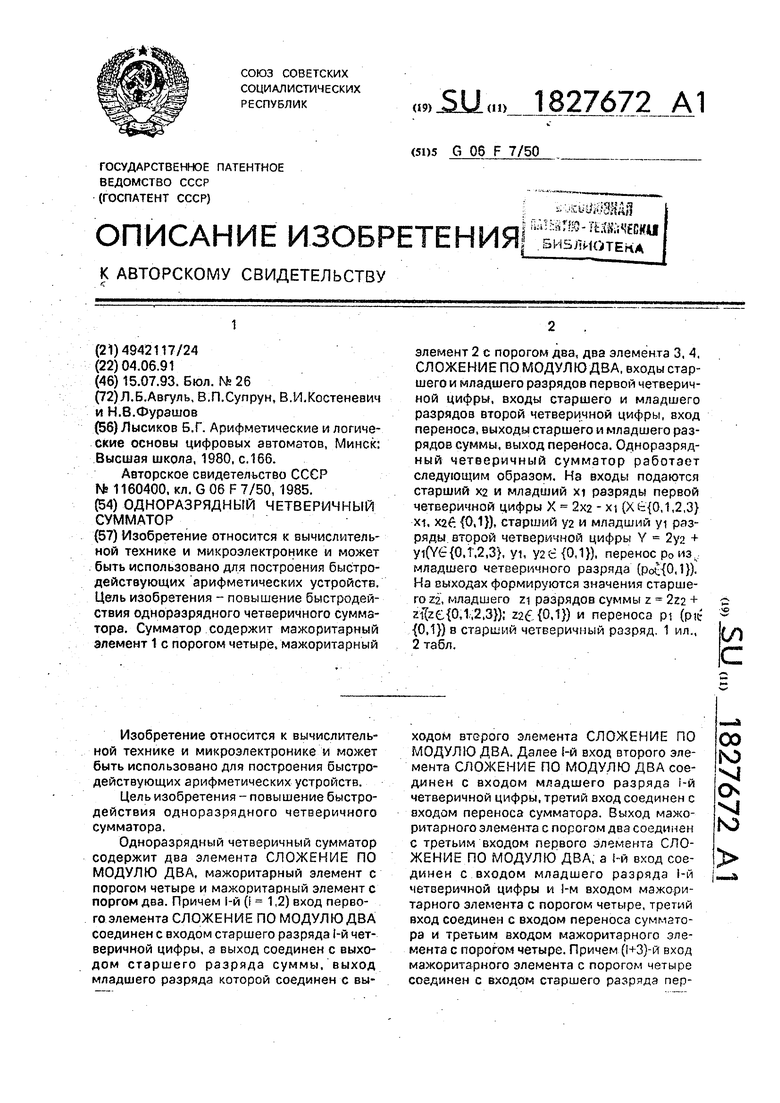

На чертеже представлена функциональ- мая схема одноразрядного четверичного сумматора.

Сумматор содержит мажоритарный эле- мент с порогом четыре 1, мажоритарный элементе порогом два 2, два элемента СЛО- ЖЕНИЕ ПО МОДУЛЮ ДВА 3 и 4, входы старшего 5 и младщего б разрядов первой четверичной цифры, входы старшего 7 и младшего 8 разрядов второй четверичной цифры, вход переноса 9, выходы старшего 10 и младшего 11 разрядов суммы, выход переноса 12.

Одноразрядный четверичный сумматор работает следующим образом. На входы 5 и 6 подаются соответственно старший ха и младший xi разряды первой четверичной цифры Х 2x2 + xi (Х€{0,1,2,3}; XL Х2Ј{0,1{), на входы 7 и 8 подаются соответственно старший у 2 и младший yi разряды второй четверичной цифры Y 2у2 + yi (YЈ{0,1,2,3}, У1/У2С{0, 1 }), на вход 9 - перенос ро из младшего четверичного разряда (роЈ {0,1}JT На выходах 10,11 и 12 формируются значения старшего гг, младшего г разрядов суммы Z 2z2 + 21 (ZC{ 0,1,2,3}; zi, Z2Ј{0,1}) и переноса pi {pi(Ј{0,1}} в старший четверичный разряд.

При этом имеет место

Ро -1- X + Y 4pi + Z 2{х2 + уз) + xi + yi + +Ро 4pt + 2z2 +zi(1)

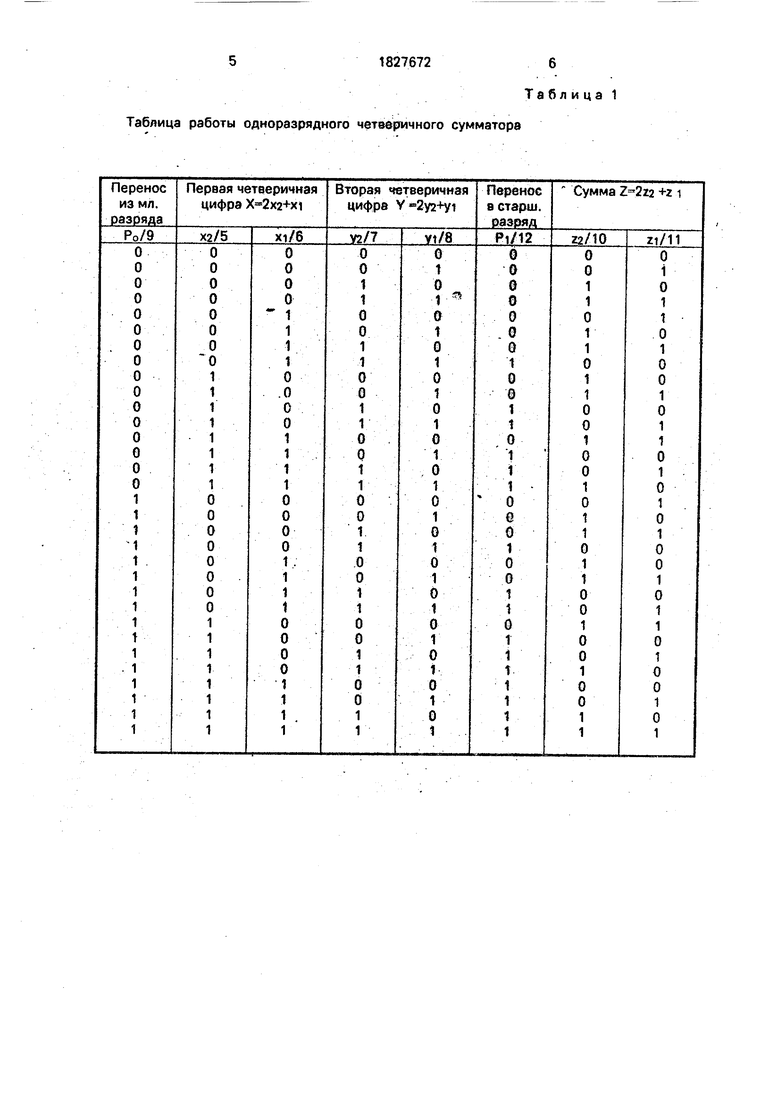

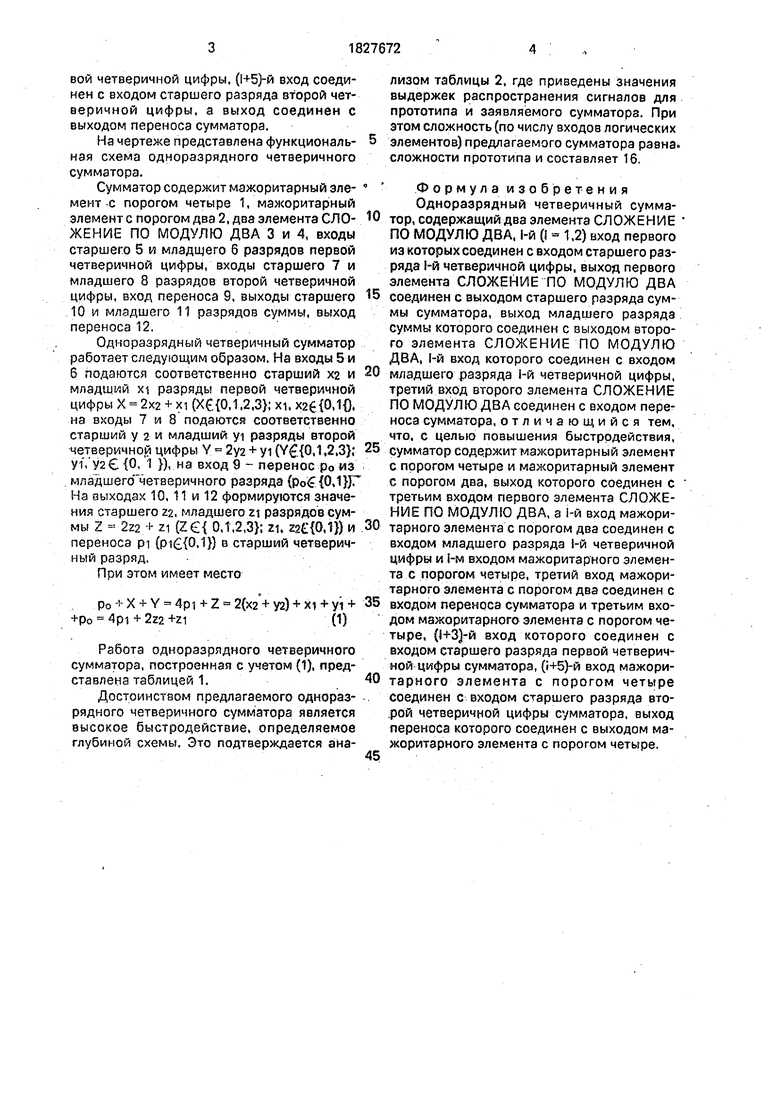

Работа одноразрядного четверичного сумматора, построенная с учетом (1), представлена таблицей 1.

Достоинством предлагаемого одноразрядного четверичного сумматора является высокое быстродействие, определяемое глубиной схемы. Это подтверждается ана

лизом таблицы 2, где приведены значения выдержек распространения сигналов для прототипа и заявляемого сумматора. При этом сложность (по числу входов логических элементов) предлагаемого сумматора равна сложности прототипа и составляет 16.

Формула изобретения Одноразрядный четверичный сумматор, содержащий два элемента СЛ ОЖ Е Н И Е ПО МОДУЛЮ ДВА, 1-й (I - 1,2) вход первого из которых соединен с входом старшего разряда 1-й четверичной цифры, выход первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединен с выходом старшего разряда суммы сумматора, выход младшего разряда суммы которого соединен с выходом второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, 1-й вход которого соединен с входом младшего разряда 1-й четверичной цифры, третий вход второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединен с входом переноса сумматора, отличающийся тем, что, с целью повышения быстродействия, сумматор содержит мажоритарный элемент с порогом четыре и мажоритарный элемент с порогом два, выход которого соединен с третьим входом первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, а i-й вход мажоритарного элемента с порогом два соединен с входом младшего разряда 1-й четверичной цифры и J-м входом мажоритарного элемента с порогом четыре, третий вход мажоритарного элемента с порогом два соединен с входом переноса сумматора и третьим входом мажоритарного элемента с порогом четыре, {И-3)-й вход которого соединен с входом старшего разряда первой четверичной цифры сумматора, 0+5}-й вход мажоритарного элемента с порогом четыре соединен с входом старшего разряда второй четверичной цифры сумматора, выход переноса которого соединен с выходом мажоритарного элемента с порогом четыре.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1991 |

|

SU1800453A1 |

| Одноразрядный четверичный сумматор-вычитатель | 1984 |

|

SU1229756A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1658145A1 |

| Сумматор по модулю три | 1991 |

|

SU1830528A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Сумматор по модулю три | 1991 |

|

SU1797109A1 |

| Сумматор по модулю три | 1991 |

|

SU1798777A1 |

| Одноразрядный четверичный сумматор | 1983 |

|

SU1160400A1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ШЕСТНАДЦАТИ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2050584C1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения быстродействующих арифметических устройств. Цель изобретения - повышение быстродействия одноразрядного четверичного сумматора. Сумматор содержит мажоритарный элемент 1 с порогом четыре, мажоритарный элемент 2 с порогом два, два элемента 3, 4. СЛОЖЕНИЕ ПО МОДУЛ Ю ДВА, входы старшего и младшего разрядов первой четверичной цифры, входы старшего и младшего разрядов второй четверичной цифры, вход переноса, выходы старшего и младшего разрядов суммы, выход переноса. Одноразрядный четверичный сумматор работает следующим образом. На входы подаются старший Х2 и младший xi разряды первой четверичной цифры X 2x2 - xi {Xfc{0,1,2,3} XL X2f. {0,1}), старший у2 и младший yi разряды второй четверичной цифры Y 2у2 + yi(Ye{0,r,2,3}, yi, У2б{0,1}), перенос ро из младшего четверичного разряда (роС{0,1}). На выходах формируются значения старшего Z2, младшего zi разрядов суммы z 2г2 + ziTzt{0,1(2,3}); Z2f {0,1}) и переноса pi (pit {0,1}) в старший четверичный разряд 1 ил., 2 табл. сл с

Таблица работы одноразрядного четверичного сумматора

Та бл и ц а 2

Таблица значений задержек распространения сигналов прототипа и заявляемого сумматора

Примечание: г - задержка на вентиль.

В

ь

п

т

4

ю

п

Авторы

Даты

1993-07-15—Публикация

1991-06-04—Подача