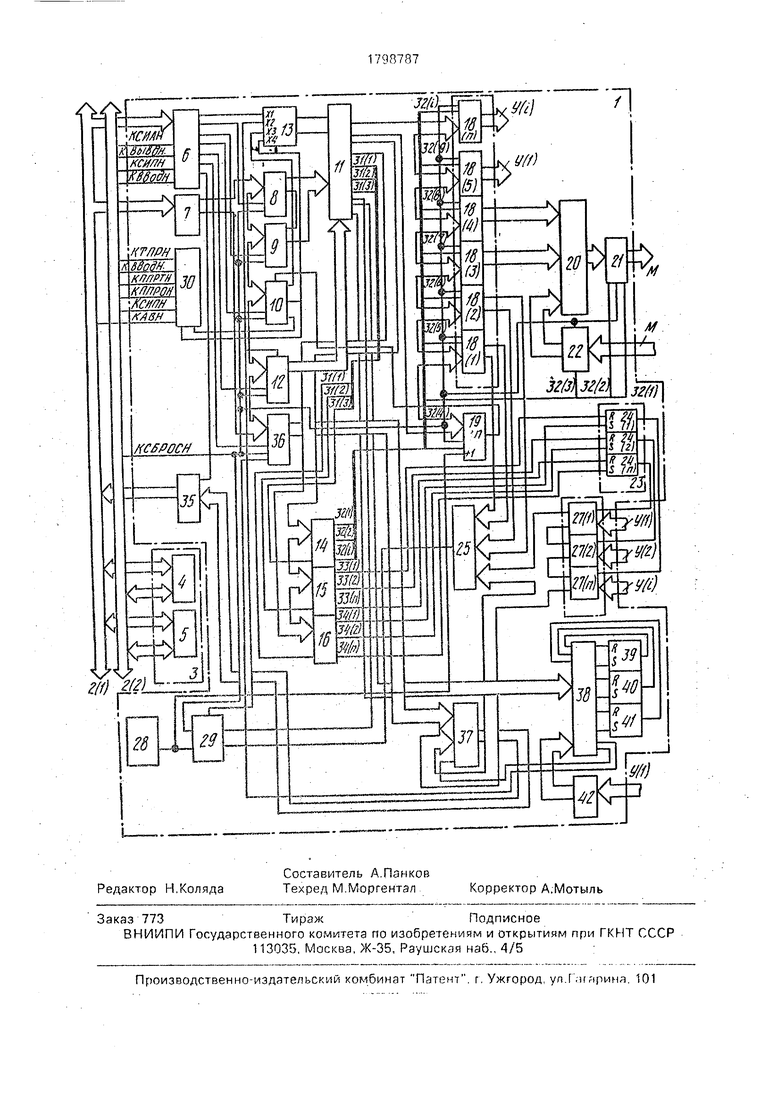

управления обменом, блок 17изп выходных регистров, включающий регистр РВ 18 (1.) - 18 (п), счетчик 19 времени, мультиплексор 20 искажения, регистр 21 искаженных данных, входной регистр 22 данных, блок 23 из п триггеров обмена, включающий триггеры 24 (1) - 24 (п), схему 25 сравнения, блок 26 из шинных формирователей, содержащий шинные формирователи ШФ 27 (1) - 27 (п), генератор 28 тактовых импульсов, триггер 29 приращения, схему 30 требования прерывания, блок 35 магистральных передатчиков, счетчик 36. еосто янийу блок оперативной памяти 37, шифратор 38, триггеры управления 39, 40, 41.

Блок 35 предназначен для подключения к.магистрали 2 ЭВМ. ....--Л

Блок 37 служит для записи; слов - состояний шин управляющего выхода объекта контроля - адресных информационных уп- равляющих, контрольных и других шин.

;vШифратор 38 и триггеры Т39, Т40, Т41 представляют собой микропрограммный автомат с обратной связью, выполняют функцию синхронизации запири состояний шин управляющего выхода объекта контроля с появлением определенных комбинаций сигналов на шине управления У (1) управляющего выхода объекта контроля. Содержимое блока ПЛМ 38 (микропрограм- :мы автомата) определяется логикой работы управляющего выхода объекта контроля. Если в качестве управляющего выхода объекта контроля может быть использован ий- терфейс ИУС, то и микропрограммы автомата, содержимое блока ПЛМ 38, могут иметь следующий вид (см. таблицу). Входы Т1, Т2, ТЗ - выходы триггеров Г39, Т40, Т41 соответственно. Входы 51, Б2, БЗ являются седьмым выходом первого блока оператив- ной памяти. Входы ШПРА, ШППА, ШППР, ШЗД, ШНД- шины управления интерфейса ИУС (1).; Выход 7 блока ПЛМ (см. табд.1) соединен со счетным входом счетчика состояний 35, выход 8 блока ПЛМ соединен со входом записи второго блока оперативной памяти. Вход X не анализируется и равен О или 1, Каждая микропрограмма начинается с нулевой микрокоманды, которая задается кодом ТТ1 с блока 11 на вход разрядов 3, 4, 5. При этом триггеры Т39...Т40 сброшены в сигналы С О, ЗП 1: входные сигналы на разряды 0, 1,2, 6...10 могут принимать любые значения, .После введения неисправности устрой- . ством для контроля неисправностей с седьмого выхода блока 11 на четвертый вход блока 38 подается код микропрограммы, . при работе которой будут зафиксированы состояния информационных (или других)

шин управляющего выхода объекта контроля в блоке 37. В ходе выполнения микропрограмм анализируются шины управления управляющего выхода объекта контроля, выдается сигнал записи на блок 37 и сигнал на счетный вход блока 36, и блок 36 выдает новый адрес на блок 37.

Содержимое блока оперативной памяти 37 может быть считано в микроЭ ВМ 3. Адрес ячейки памяти блока 37 задается в блоке 36, а информация считывается через блок 35.

Работает устройство следующим образом. После введения неисправности из блока .11 на блок 38 поступает код микропрограммы (например, код 110 для первой микропрограммы в табл.1 - вход 4, разряды 3, 4, 5 соответственно), с поступлением на вход 5 блока 38 группы сигналов 01101 (разряды 6...10 соответственно) состояние выходов блока 38 измнится и произойдет установка триггера Т39 и выдача на блок 37 сигнала . 0, т.е. на информационных шинах интерфейса ИУС находится адрес и сигнал ЗП фиксирует в блоке 37 этот адрес. С приходом на вход 5 (разряд 7) сигнала нулевого уровня изменятся и выходные сигналы ПЛМ 38 - триггер Т 39 сбрасывается .навливается Т40 и снимается сигнал ЗП (ЗП 1). После установления в. разряда 6 на входе ПЛМ 38 триггеры Т39 и Т40 устанавливаются в 1 и, .выдается С 1, что приведет к увеличению содержимого счетчика состояний 36 на 1 и выдаче нового адреса на блок 37. С приходом 1 на разряд 7 входа 5 шифратора произойдет сброс Т39, T4Q, триггер Т41 установится в 1 и сигнал С в О.. Таким образом, адрес с магистрали ИУС зафиксирован и устройство готово к фиксации данных. С приходом 1 на вход 5 разряд 9 установит в 1 триггерТ39 (при этом разряды 6...8 . не анализируются). Приход на вход 5 разряда 10 сигнала нулевого уровня означает, что на информационных шинах интерфейса ИУС находятся данные. Сбрасывается триггер Т39, устанавливается Т40 и выход 8 блока 35 устанавливается в О, После установления на входах разрядов 9 и 10 комбинация 01 соответственно триггер Т39 устанавливается в 1, выдается сигнал С и снимается сигнал записи на Б П 37. С приходом по обратной связи кода 111 на входы 1, 2. 3 от триггеров Т39...Т41 снимается С (С 0) и работа устройства по фиксации состояний управляющего выхода объекта контроля приостанавливается.

Устройство предназначено для имитации неисправностей, формирования управляющих воздействий, анализа ответных

сигналов, с помощью которых осуществляется введение в вычислительную систему различных типов отказов и сбоев, также для фиксации состояния управляющих, адресных, информационных и других шин после введения неисправностей и передачи информации в ЭВМ 3.

Работа устройства, заключается в формировании сигналов неисправности непосредственно в интерфейсе и путем эмуляции различных режимов работы магистрали, а также в фиксировании состояния управляющего выхода объекта контроля. Каждому из возможных состояний соответствует своя микропрограмма в шифратор 38. Коды начала работы микропрограмм хранятся в блоке 11, Возможно применение устройства в любом интерфейсе, при этом изменяются только микропрограммы блока 11, количество используемых регистров и содержимое блока ПЛМ 38... В таблице представлены четыре микропрограммы (содержимое блока 38) работы устройства по фиксации адреса и данных в цикле чтения задатчиком на интерфейсе ИУС (1), адреса и данных в цикле записи адреса в любом цикле и данных в любом цикле. Фор: мул а изобретения Устройство для контроля неисправностей, содержащее блок оперативной памяти, дешифратор управления записью/ мультиплексор искажений, блок задания тестов и анализа реакции, схему сравнения, два дешифратора обмена, выходные регистры с первого по n-й, регистр состояния, дешифратор адресов, п.. шинн ых формирователей, п триггеров обмена, первый -и второй входные буферные регистры, счетчик адреса, счетчик времени, мультиплексор управления записью входной регистр данных, регистр искаженных данных, триггер приращения и генератор тактовых импульсов, причем первый информацион- ный выход блока оперативной памяти соединен, с информационными входами с второго по n-й выходных регистров и счет-; чйка времени, второй информационный выход блока оперативной памяти подключен, к информационным входам дешифратора управления записью, первого и второго де-. шифраторов управления обменом, третий, четвертый и пятый информационные выходы блока оперативной памяти соединены с. входами разрешения соответственно дешифратора управления записью, первого и второго, дешифраторов управления обменом, шестой информационный выход блока оперативной памяти подключен к установочному входу триггеров приращения, вход

сброса которого соединен с выходом схемы сравнения, первый информационный вход которой подключен к информационному выходу первого выходного регистра, второй

5 информационный вход схемы сравнения соединен с информационным выходом второго выходного регистра. третий .информационный вход схемы сравнения .подключен к информационным выходам с

10 первого по n-й шинных формирователей, входы управления которыхсоединеныс информационными выходами с первого по п-й триггеров обмена, входы сброса которых соединены соответственно с первого по п-й

15 выходами первого дешифратора управления обменом, установочные входы с первого по n-й триггеров обмена соединены с первого по n-й выходами второго дешифратора управления обменом, информационные вы2.0 ходы третьего и четвертого выходных регистров соединены соответственно с первым и вторым информационными входами муль- типлексора искажения, управляющий вход которого подключен к информационному

5 выходу входного регистра данных, выход мультиплексора искажения соединен с информационным входом регистра искаженных данных, информационные входы разрядов Разрешение прерывания, На0 чало работы регистра состояния подключены к информационному входу блока .задания тестов и анализа реакций, синхров- ход регистра состояния соединен с первым

.выходом дешифратора адресов, второй и 5 третий выходы которого соединены с входа- мй управления записью первого и второго входных буферных регистров соответственно, четвертый и.пятый выходы дешифратора адресов.подключены к.первому информаци40 онному входу мультиплексора управления записью .и входу управления записью счет- чик.адреса соответственно, счетный вход которого соединен с выходом триггера приращения и вторым информационными вхо5 дом мультиплексора управления записью, первый управляющий вход которого соединен с выходом разряда Начало работы регистра состояния, второй управляющий вход мультиплексора управления записью

0 соединен с выходом разряда Аварийное отключение регистра состояния, выходы разрядов Аварийное состояние и Требование прерывания регистра состояния подключены к входу прерывания блока задания

5 тестов и анализа реакций, информационные выходы первого и второго буферных регистров соединены е:.информационными входами блока оперативной памяти, адресный . вход которого подключен к информационному выходу счетчика адреса, входы управления записью с первого по n-й выходных регистров, счетчика времени, первый и второй входы управления записью регистра ис- кэженных данных и вход управления записью входного регистра данных подключены к выходам с первого по 1-й дешифраторов управления записью (где I n + 4), выход переполнения счетчика времени с входом разряда Аварийное отключение регистра состояния, счетный вход счетчика времени соединен с выходом генератора тактовых импульсов и разрешающим входом триггера приращения, входы начальной установки счетчика адреса, счетчика времени, первого и второго входных буферных регистров, с первого по n-й выходы регистров, регистра входных данных, регистра искаженных данных, установочные входы разрядов Аварийное (отключение , Разрешение прерывания, Начало работы регистра состояния, синхровходы с первого по n-й триггеров обмена, синхровход триггера приращения соединены с выходом сброса блока задания тестов и анализа реакций, информационные входы с первого по п-й триггеров обмена, синхровход и информационный вход разряда Аварийное отключение регистра состояния подключены к шине нулевого потенциала, информационные входы счетчика адреса регистра состояния, а также первого и второго входных буферных регистров подключены к информац ионнЬму выходу блока задания тестов и анализа реакций, информационный вход дешифратора адресов подключен к информационному выходу блока-Задания тестов и .анализа реакций, первый и второй входы разрешения дешифратора адресов соединены с управляющим выходом блока задания тестов и анализа реакций, шестой выход дешифратора адресов подключен к управляющёму входу блока задания тестов и анализа реакций, информационные выходы с пятого по n-й выходных регистров соединены с информационным входом блока задания тестов и анализа реакций, выход регистра искаженных данных является выходом устройства для подключения к информацйонному входу объекта контроля, вход входного регистра данных является входом устройства для подключения к информационному выходу объекта контроля, входы с первого по n-й шинных формирователей являются входами устройства для подключения к управляющему выходу обьекта контроля, первый и второй выходы мультиплексора управления записью соединены с входами Запись-чтение и Выборка кристалла блока оперативной памяти соответственно, выход блока памяти соединен с

информационным.входом первого выходного регистра, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет введения различных типов неисправностей, в него введены блокмагистральных передатчиков, счетчик состояний, второй блок оперативной памяти, шифратор, первый, второй и третий триггеры управления, второй блок

0 магистральных приемников, причем информационный вход блока магистральных передатчиков соединен с выходом второго блока оперативной памяти, адресные входы которого соединены с разрядными выходами

5 счетчика состояний, информационный вход второго блока оперативной памяти соединен с третьим информационным входом схемы сравнения и выходами с первого по n-й шинных формирователей, информаци0 онный вход счетчика состояний подключен к выходу счетчика состояний, соединен с седьмым выходом дешифратора адресов, восьмой выход которого соединен с управляющим входом блока магистральных пере-;

5 датчиков, выход которого соединен с информационным входом блока задания тестов и анализа реакций, управляющий выход которого соединен с третьим информационным входом дешифратор ад0 ресов, вход начальной установки счетчика состояний соединен с входами начальной установки счетчика адресов, счетчика времени, .первого и второго буферных регист- . ров, с первого по n-й выходных регистров,

5 регистра входных данных, регистра иска- женных данных, установочными входами . соответствующих разрядов регистра состояния, синхровходами с первого по n-й триггеров обмена, смнхровходом триггера

0 приращения и выходом признака сброса блока; задания тестов и анализа реакций, выход первого триггера управления соединен с первым информационным входом шифратора, второй информационный вход

5 которого соединен с выходом второго триггера управления, выход триггера управленияподключен к третьему информационному входу шифратора, четвертый информационный вход которого со- 0 единен с седьмым выходом первого блока оперативной памяти, пятый информационный вход шифратора ПО.ЦКПЮЧРЧ к выходу второго блока магистральных приемников., информационный вход которого подключен

5 к управляющему выходу объекта контроля, первый, второй и третий выходы шифратора соединены с входами сброса первого, вто- . рого и третьего триггеров управления соот- бедственно, третий, четвертый и пятый шифраторы соединены с входами установки

первого, второго и третьего триггеров управления соответственно, седьмой выход шифратора подключен к счетному входу

счетчика состояний, вбсьмой выход шифратора соединен с входом записи второго блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

Авторы

Даты

1993-02-28—Публикация

1991-04-01—Подача