Изобретение относится к вычислительной технике, в частности к быстродействующим многопроцессорным системам.

Целью изобретения является повышение производительности многопроцессорной вычислительной системы.

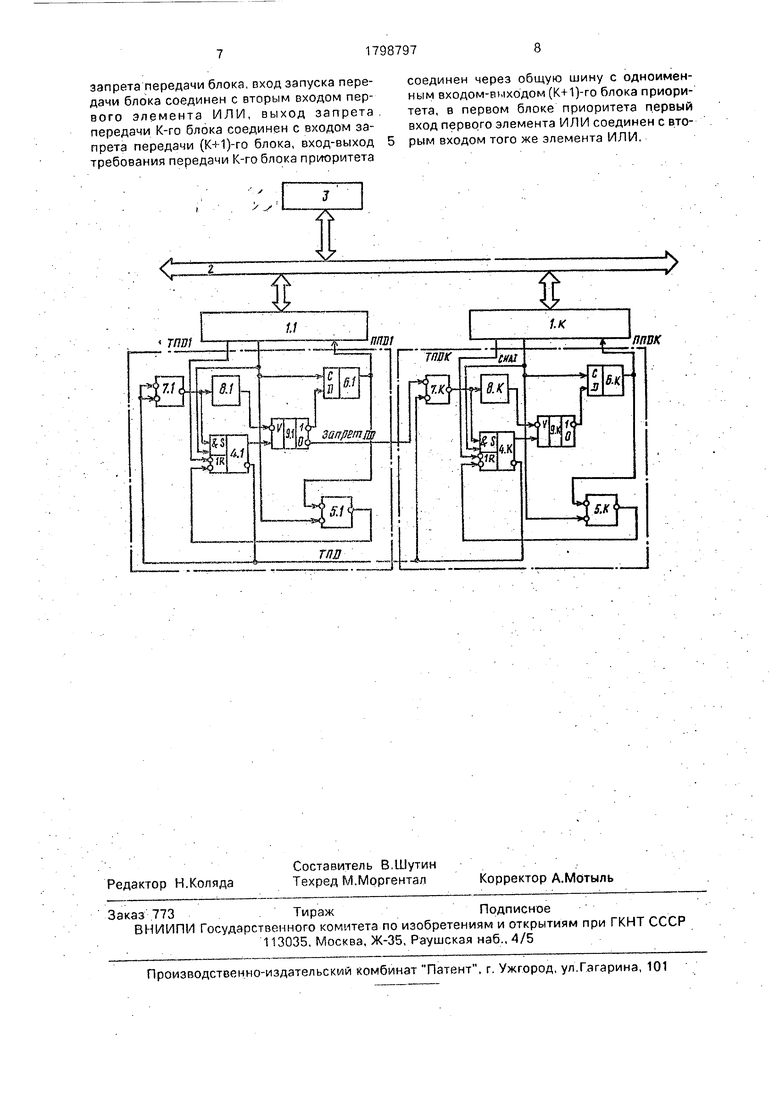

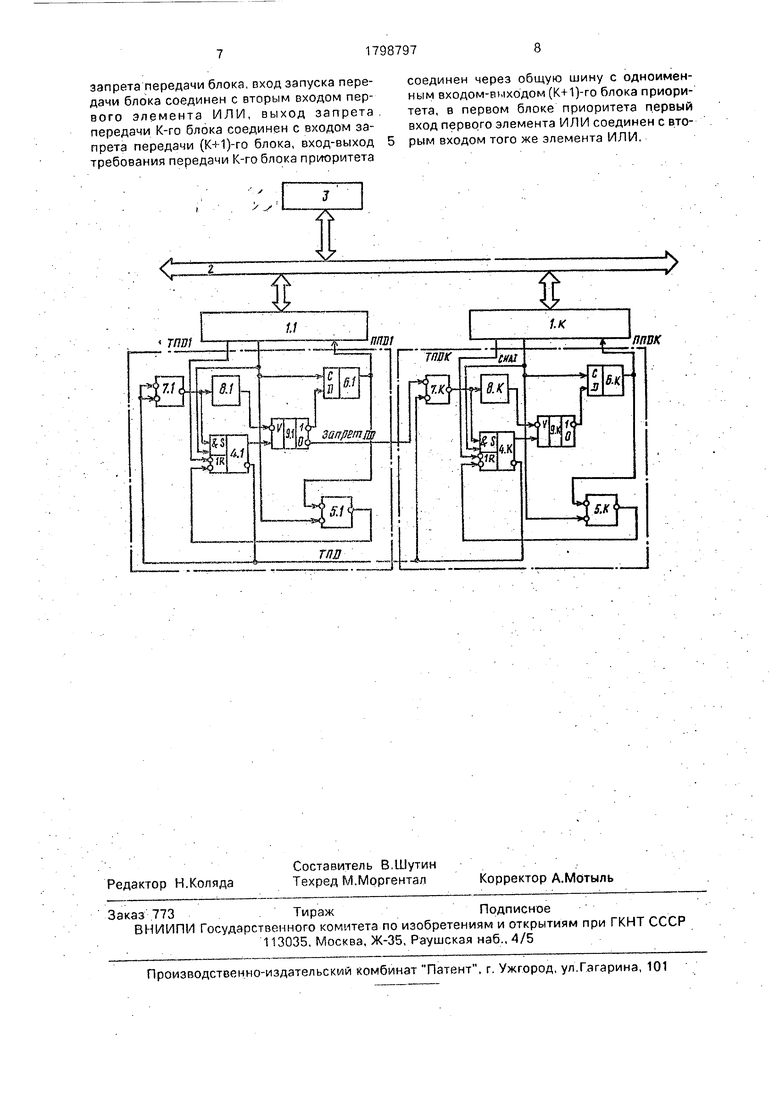

Многопроцессорная система, представленная на чертеже, содержит процессорные блоки 1.1,..,1.N, входы/выходы данных, адреса и управления которых через общую . шину 2 соединены между собой и с одно- именными входами/выходами системной памяти 3. Первые выходы процессорных блоков 1.1„..,1.1М соединены с первыми входами установки в ноль соответствующих первых триггеров 4,1,...AN, вторые входы установки в ноль первых триггеров 4.1,... AN соединены с выходами соответствующих вторых элементов ИЛИ. 5.1,...,5.N. Вторые входы вторых элементов ИЛИ 5.1.....5.N соединены с выходами соответствующих триггеров 6.1.....6.N и с входами соответствующих процессорных блоков

1.1,...,1.N. Вторые выходы процессорных блоков 1.1,...,1.N соединены с первыми входами соответствующих вторых элементов ИЛИ 5.1,...,5.N, с входами синхронизации соответствующих вторых триггеров 6.1,...,6.N и со вторыми входами установки в единицу соответствующих первых триггеров 4,1,,..AN. Первые входы установки в . единицу первых триггеров 4,1,...AN соединены с выходами соответствующих первых элементов ИЛИ 7.1,...,7.М и с входами соответствующих элементов задержки 8.1,...,8.N. Выходы элементов задержки 8.1,...,8.№ соединены со входами разрешения соответствующих дешифраторов 9.1,...,9.М. Информационные входы дешифраторов ...,(9.М соединены с прямыми выходами соответствующих первых триггеров 4.1,...,4,1М, Инверсные выходы первых триггеров 4.1,...AN соединены с линией ТПД (требования передачи), с которой соединены первый и второй входы первого элемента ИЛИ 7.1, соответствующего первому про-5

Ё

VI

45 00 VI VI

цессорному блоку 1.1, и первых элементов ИЛИ 7,2,...,7.N, соответствующих процессорным блокам 1.2.....1 .N, соединены со вторыми выходами дешифраторов 9.1,.,.,9 (N-1), соответствующих предыдущим процессорным блокам 1.1,,..,1 (N-1), Первые выходы дешифраторов 9.1,,..,9.N соединены информационными входами соответствующих вторых.три$теров 6.1 ,...,6.М. Элементы 4.К, 5.К, 6.К, 7,К, 8Ж, 9.К представляют собой К-й блок приоритета.

Процессорные блоки 1.1,..,,1. N могут быть построены на базе серийно выпускаемых однокристальных микропроцессоров К1801 ВМ1, КТ80ВМ2, К580ВМ80, К1910ВМ86 и др. В качестве управляющих входных и выходных сигналов можно использовать соответствующие сигналы этих микропроцессоров. В состав общей шины 2 входят проводники, обеспечивающие передачу между устройствами адреса, данных и управляющих сигналов. Количество и назначение указанных проводников определяется в ы б р а н н ы м п р о ц е с с о р о м. Например, для процессора микроЭВМ Электроника-60 число и назначение указанных проводников определяется в соответствии с ОСТ 11.305.903-80. Для построения системной памяти 3 мо гут быть использованы микросхемы типа К565РУЗ, К5б65РУ6,а также,. К537РУЮ, К573РФЗ, К537РФ5 и др. Триггеры 4.1,...,4.К могут быть реализованы на стандартных микросхемах серий К555, К531 и др. В качестве остальных элементов могут быть использованы.стандартные микросхемы серий К555, К531, например К555 ЛАН, К555ТМ2, К531ИД14, К555ЛЛ1 и др.

При возникновении требования передачи и захвата общей шины процессорными блоками система работает следующим образом. Дейзи-цепочка Запрет ПОД задает приоритет процессорных блоков: процессорный блок 1.1 имеет высший приоритет, процессорный блок 1.N - низший. При отсутствии требований передачи и захвата общей шины (ТПД1 0), первые триггеры 4.1,...,4.4 установлены в ноль, и на линии ТПД устанавливается в ысокий уровень. При этом на управляющих входах (V) дешифраторов 9.1,...,9.N высокий уровень, на информационных входах вторых триггеров 6.1,,..,6.N высокий уровень, на тактирующих входах этих триггеров высокий уровень (так как общая шина не занята - сигнал СЙА1 имеет высокий уровень) и на выходах вторых триггеров 6.1,...,6.N устанавливается высокий уровень, т.е. сигналы ППД (предоставление передачи) отсутствует. При появлении сигналов требования передачи (ТГ1Д1

1) первые триггеры соответствующих процессорных блоков устанавливаются в единицу так как на всех входах этих триггеров - высокий уровень. На линии ТПД появляется низкий уровень. В дальнейшем, для удобства, рассмотрим работу системы при наличии сигналов требования передачи захвата общей шины от двух первых процессорных бл оков, хотя многопроцессорная

система работает аналогичным образом при наличии сигналов требования передачи и захвата общей шины и от других процессорных блоков. Сигнал низкого уровня с линии ТПД проходит элементы 7.1 и 8,1 и открыва5 ет дешифратор 9.1. При этом на выходе второго триггера 6.1 установится сигнал ППД1 (низкий уровень), разрешающий выход процессорного блока 1.1 на общую шину 2, Получив сигнал ППД1, процессорный блок 1.1

0 выполняет цикл ввода-вывода по общей шине 2 (устанавливается сигнал СИА1 низким). Сигнал СИА1 запрещает запись во второй триггер 6.1 и устанавливает в ноль первый триггер 4.1, так как вследствие того, что на

5 обоих входах второго элемента ИЛИ 5.1 низкий уровень, с выхода его попадает на второй вход установки в ноль триггера 4,1. На линии запрет ПД между процессорными

блоками 1.1 и 1.2 появится при этом низкий 0 уровень, который через элементы 7.2 и 8,2 откроет дешифратор 9.2. При этом на информационном входе второго триггера 6.2 установится низкий уровень. Но сигнал ППД2 на входе процессорного блока. 1.2 не 5 появится, так как низкий уровень на такти рующем входе второго триггера 6.2 (СИА1) запрещает запись в него. По окончании обмена процессорный блок 1.1 сбрасывает сигналы ТПД1, СИА1, На выходе второго

0 триггера 6,1 сбрасывается, а на выходе второго триггера 6.2 устанавливается сигнал ППД. . .

Элементы задержки 8.1,...,8.N служат для задержки сигналов, открывающих де5 шифраторы 9.1 ,...,9.N на время, достаточное

для переключения первых триггеров

4,1,..,,4,N. Необходимость такой задержки

обусловлена следующим. Допустим, сигна. лом ТПД2триггер 4.2 установился в едини0 цу и. на линии ТПД установился низкий уровень. Допустим, что прежде чем сигнал низкого уровня с линии ТПД прошел на выход первого элемента ИЛИ 7.1 и попал на вхйд установки в единицу первого тригге5 ра 4.1, юявился сигнал ТПД1 и началось переключение первого триггера 4.1 в единицу. Тогда при отсутствии элемента задержки дешифратор 9.1 может открыться до окончания переключения триггера 4.1 и низкий уровень с прямого выход.ч триггера 4.1

появится на линии Запрет ПД, позволяя выработку сигнала ППД2. Когда же триггер 4.1 закончит переключение в единицу, выработается сигнал ППД1. Таким образом, появляется возможность одновременной передачи по общей шине двумя (а в общем случае и больше) процессорными блоками. Эта ситуация исключается при наличии элементов задержки 8.1,...,8.М. Следует добавить, что при наличии нескольких сигналов ТПД1 разрешение передачи по общей шине ППД1 будет предоставляться последовательность, в соответствии с приоритетами процессорных блоков 4.1,,..,4.N (блоки с большим номером имеют меньший приоритет. Если же в то время, когда доступ к общей шине осуществляет 1.М процессорный блок и установлен сигнал требования передачи и захвата общей шины, допустим, от 1 .(М+5) процессорного блока (т.е. триггер 4.(М+5) установлен в единицу), сигналы требования передачи и захвата общей шины выставят, допустим, 1.1, 1.(М-3), 1.(М+3) и 1.(М+7) процессорные блоки (М 3; М+ 7 М), то разрешение передачи по общей шине процессорные блоки получат в такой последовательности: 1.{М+3), 1.(М+5), 1,(М+7), 1.(М-3). Это обусловлено наличием связей между выходами первых элементов ИЛИ 7.1,...,7.N и первыми входами установки в единицу соответствующих первых триггеров 4..1,...,4.N. Эти связи не позволяют устанавливаться первым триггерам з единицу при наличии низкого уровня на линии ТПД.

Обоснование технико-экономической эффективности.

В предлагаемой вычислительной системе уменьшается среднее время ожидания процессорными блоками доступа к общей шине, что увеличивает производительность вычислительной системы по сравнению с прототипом. Если в многопроцессорной системе, выбранной в качестве прототипа, количество процессорных блоков превышает отношение времени вычисления каждым процессорным блоком ко времени обмена информацией, то часть процессорных блоков, имеющих малые приоритеты, вообще не смогут получить предоставление доступа к общей шине, а для остальных среднее время ожидания доступа к общей шине будет возрастать к общей -шине обеспечивается при любом количестве процессорных блоков, независимо от соотношения времени вычисления и времени обмена. Например, в системе числового управления CNC каждый процессор осуществляет расчет величин для управления приводами в такте управления, длительность которого составляет 2-8 мс. Кроме того, в каждом такте осуществляется обмен информацией между компонентами систем. Отношение времени вычисления ко времени обмена информа- цией при этом для каждого процессорного блока может достигать 5:1. Прототип в этом случае может иметь не более пяти процессорных блоков, так как при большем числе процессорных блоков доступ к общей шине

0 будет затруднен. В предлагаемой системе можно использовать большее количество процессорных блоков, что позволит обеспечить управление большим числом приводов, т.е. повысить производительность системы,

5. Формула изобретения

Многопроцессорная система, содержащая системную память, N процессорных блоков, N блоков приоритета, каждый из которых содержит два элемента ИЛИ и два

0 триггера, причем входы-выходы данных адреса и управления всех процессорных блоков через общую шину соединены между собой и с одноименными входами-выходами системной памяти, выходы требования

5 передачи и захвата общей шины К-го (К 1,...,N) процессорного блока соединены соответственно с одноименными входами К-го блока приоритета, выход разрешения передачи которого соединен с одноименным

.0 входом К-го процессорного блока, в К-м блоке приоритета вход требования передачи соединен с первым входом установки в О первого триггера, инверсный выход которого соединен с входом-выходом требования

5 передачи блока приоритета, с первым входом первого элемента ИЛИ, выход которого соединен с первым входом установки в 1 первого триггера, вход захвата общей шины соединен с вторым входом установки в 1

0 первого триггера, первым входом второго элемента ИЛИ и входом синхронизации второго триггера, прямой выход которого соединен с выходом разрешения передачи блока приоритета и вторым входом второго

5 элемента ИЛИ, выход которого соединен с вторым входом установки в О первого триггера, отличающаяся тем, что, с целью повышения производительности системы путем обеспечения возможности из0 менения приоритета процессорных блоков, в каждый блок приоритета введены элемент задержки и дешифратор, причем в К-м блоке приоритета выход Первого элемента И соединен с входом задержки, выход которой

5 соединен с входом разрешения дешифратора, первый выход которого соединен с информационным входом второго триггера, прямой выход первого триггера соединен с информационным, v входом дешифратора, второй выход которого соединен с выходом

запрета передачи блока, вход запуска передачи блока соединен с вторым входом первого элемента ИЛИ, выход запрета передачи К-го блока соединен с входом запрета передачи (К-И)-го блока, вход-выход требования передачи К-го блока приоритета

соединен через общую шину с одноименным входом-выходом (К+1)-го блока приоритета, в первом блоке приоритета первый вход первого элемента ИЛИ соединен с вторым входом того же элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров с общей шиной мультипроцессорной системы | 1988 |

|

SU1571606A1 |

| Счетчик импульсов | 1986 |

|

SU1370781A1 |

| Устройство приоритетного выбора непрерывного дискретизированного сигнала по принципу "большинства | 1984 |

|

SU1252937A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1508233A1 |

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Волоконно-оптическая система связи | 1990 |

|

SU1823141A1 |

| Устройство для поиска максимального числа | 1985 |

|

SU1314334A1 |

| Многопроцессорная система | 1990 |

|

SU1709330A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

Изобретение относится к вычислительной технике, в частности к быстродействующим многопроцессорным системам.. Целью изобретения является повышение производительности многопроцессорной вычислительной системы. Поставленная цель достигается тем, что система содержит N процессорных блоков, N блоков приоритета, каждый из которых содержит два элемента ИЛИ. два триггера, элемент задержки и дешифратор, системную память. 1 и л.

| Валяк Е | |||

| Последовательно-параллельные вычисления | |||

| М.:МИР, 1985, с.50 | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-28—Публикация

1990-05-21—Подача